基于UVM實現SM4算法的自動化驗證平臺

馬 盼,靳 旭

(1.北京全路通信信號研究設計院集團有限公司,北京 100070;2.北京市高速鐵路運行控制系統工程技術研究中心,北京 100070)

1 概述

隨著國內高速鐵路的快速發展,越來越多的前沿技術被應用于軌道交通安全通信系統中。由于硬件集成度高、可并行處理數據等特點,為提升鐵路信號平臺系統性能和降低軟件復雜度,CPLD/FPGA(可編程邏輯器件)和定制芯片等硬件產品得到廣泛應用。針對這些硬件產品,邏輯功能仿真驗證是保證產品正確性和安全性的重要環節,其目的就是驗證硬件產品是否滿足設計需求[1]。目前鐵路相關CPLD/FPGA邏輯仿真采用傳統定向測試序列進行功能驗證[2],這種方法針對不同序列搭建不同的測試環境,導致平臺搭建時間長,平臺移植復用性差,驗證效率不高。

驗證方法學的發展有效地提高了驗證效率,通用驗證方法學(Universal Verification Methodology,UVM)面向所有數字設計,涵蓋從模塊級到芯片級,從專用集成電路(Application Specific Integrated Circuit,ASIC)到CPLD/FPGA,從控制邏輯、數據通路到處理器的全部場景[3]。驗證語言SystemVerilog的面向對象和隨機約束等核心特性配合UVM提供的基礎類庫和基本驗證結構可以快速實現驗證環境的自動化。本文提出了以SM4加解密算法模塊為驗證對象,采用SystemVerilog語言構建基于UVM的自動化驗證平臺。

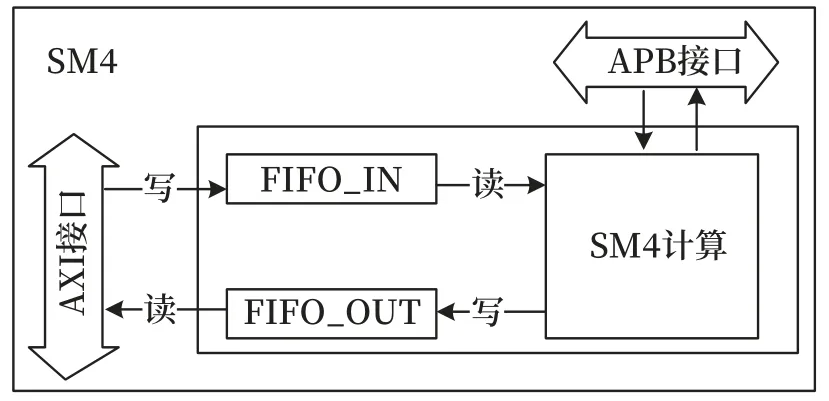

2 待測設計SM4硬件分析

SM4硬件設計結構如圖1所示,該硬件模塊內部包含兩個緩存先入先出隊列(First Input First Output,FIFO),來暫存部分傳輸數據,一個SM4計算模塊,其功能是解析傳輸數據,并計算SM4加解密結果。該算法遵循中華人民共和國國家標準《信息安全技術 SM4分組密碼算法》(GB/T 32907-2016)進行輪密鑰生成以及加密解密計算[4]。

圖1 SM4硬件設計結構框圖Fig.1 SM4 hardware design structure diagram

SM4硬件模塊通信接口符合外圍總線(Advanced Peripheral Bus,APB)和可擴展接口(Advanced Extensible Interface,AXI)總線協議,其中APB接口是片上總線協議(Advanced Microcontroller Bus Architecture,AMBA)中提出的一種低功耗和低復雜度的二級總線,在SM4硬件設計中傳輸配置模塊內部寄存器信息。AXI是一種面向高性能、高帶寬、低延遲的片內總線[5]。它的地址/控制和數據相位是分離的,支持不對齊的數據傳輸。在突發傳輸中,只需要首地址,同時分離的讀寫數據通道、支持未完成狀態下的傳輸訪問、亂序訪問和更加容易達到時序收斂。在本文描述的驗證對象中,AXI接口用于傳輸明文和密文數據。

3 UVM驗證平臺設計

UVM融合了VMM(Verification Methodology Manual)和OVM(Open Verification Methodology)驗證方法學的特性,將驗證過程中可重用和標準化的部分規定在其方法學的類庫中[6],例如uvm_object、uvm_driver、uvm_env等,通過對這些核心類的繼承和重載,使驗證平臺內的組件具有良好的封閉性并形成結構層次關系,這種具有復用性的驗證環境可以有序完成不同的測試場景。一個UVM驗證平臺主要包括序列發生器、驅動器、監視器、代理容器、參考模型和計分板,這些組件集成在環境組件中,與待測設計通過定義的接口連在一起。

本文的驗證平臺根據SM4硬件結構的特性采用標準的UVM架構進行設計,其結構如圖2所示。UVM驗證平臺組件之間通過事務級建模(Transaction Level Modeling,TLM)端口進行數據通信,從環境層次結構而言,測試頂層uvm_test用于建立整個驗證環境,從環境的結構和連接關系到使用哪條測試序列都是由測試頂層決定[7]。

環境組件包含多個代理容器和其他組件,這些不同的組件共同構成完整的驗證環境。通過測試頂層例化環境組件得到一個以uvm_test為樹根的樹狀拓撲結構,這種樹狀環境結構具有可配置性,使得環境組件可以復用。

圖2 驗證平臺結構Fig.2 verification platform structure

主代理容器封裝了序列發生器、驅動器和監視器3個基本組件,其中序列發生器可以選擇和調度由定序器產生的隨機測試序列并傳送給驅動器。驅動器從序列發生器中獲取到事物數據后,根據端口協議經過模擬轉化,在接口中對待測設計進行時序激勵。監視器用于采樣待測設計端口信號并轉換成事務級數據返回給上層代理容器進行數據傳輸。在本設計中主代理容器負責向待測設計提供符合AXI接口協議的驅動信號,并將監視器采集到的驅動數據傳遞給參考模型。從代理中只有監視器一個組件,用于實時監視待測設計的計算輸出,通過反饋接口采集結果數據。配置代理負責提供模擬寄存器的配置信號,該信號時序符合APB接口協議,用于配置測設計。

參考模型模擬待測設計的功能,在驗證平臺中參考模型與待測設計輸入相同的數據,二者經過各自的計算后,將產生的數據傳遞到計分板中進行自動對比和報告。

4 基于C的UVM參考模型

參考模型通常由驗證人員使用硬件描述語言進行開發,對于運算方法復雜的設計,需要占用大量的時間進行概念理解、編寫代碼并調試,這無疑給驗證開發帶來了額外的負擔。SystemVerilog語言提供的直接編程接口(Direct Programming Interface,DPI)可以連接C/C++高級語言,實現硬件與軟件的跨邊界通信[8]。

本文的待測設計為一個純粹的算法模塊,SM4算法具有標準的C語言函數模型,其功能為依據加密解密標志,對輸入的明文進行SM4加密,得到密文,或者對輸入的密文進行SM4解密,得到明文。為避免對算法C模型進行二次轉換,本文提出的驗證平臺采用DPI接口將算法C模型嵌入UVM環境中進行聯合仿真,具體方法如下。

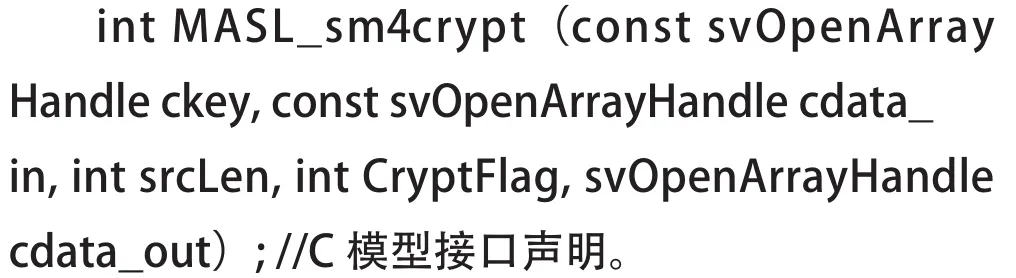

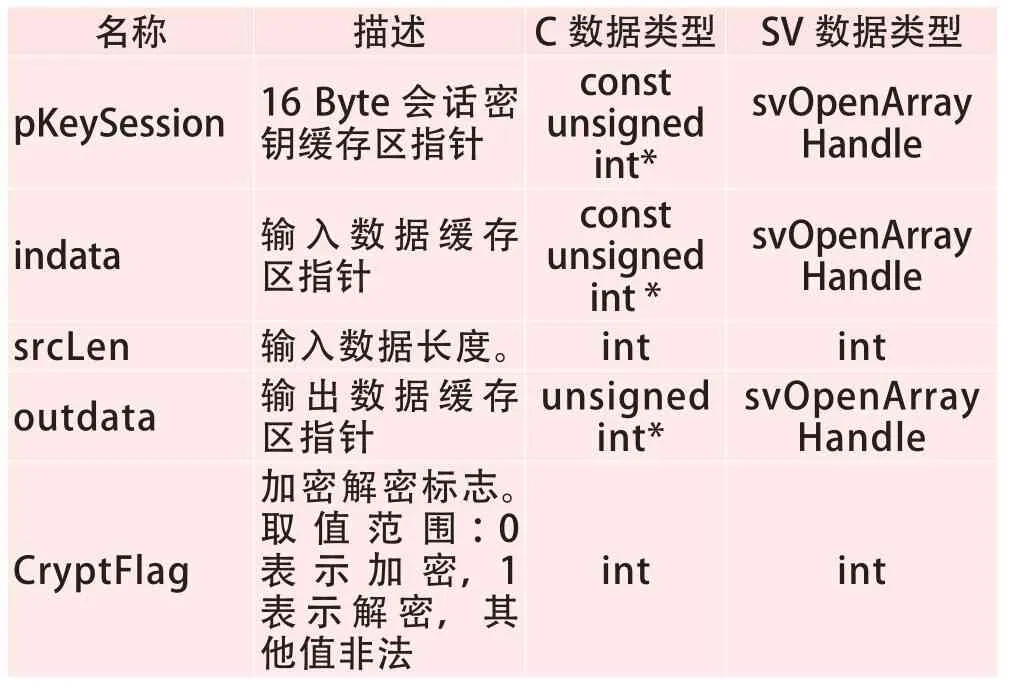

1)修改C函數接口,確定SystemVerilog和C語言程序輸入輸出之間的數據類型映射關系。在本設計中,其中C函數的端口定義如表1所示,修改前的C函數接口為:

int MASL_sm4crypt(const unsigned int*pKeySession,const unsigned int *indata,int srcLen,int CryptFlag, unsigned int*outdata); //C函數接口聲明

對照表1映射標準,C函數結構修改成如下格式:

表1 C接口定義及與SV語言之間的數據類型映射Tab.1 Mapping of data type between C interface definition and SV language

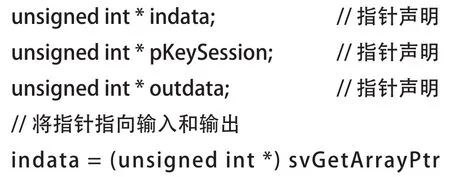

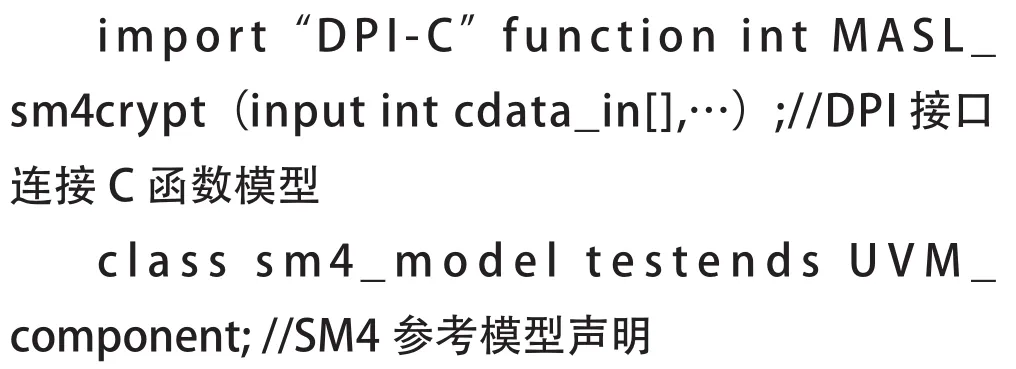

2)C程序內部聲明指針,并將指針指向輸入輸出動態數組地址,進行數據傳遞。代碼實現如下:

3)在C程序內導入數學庫函數svdpi.h,庫函數定義了SystemVerilog DPI結構和方法。

4) 在UVM參考模型中導入C函數模型。在導入C模型時,需要規定參數的方向:當數據是從System Verilog流向C函數時,參數方向規定為input,反而則為output,如果某個參數即從System Verilog流向C,同時又從C流向System Verilog,則需聲明為inout型。

5)在UVM參考模型中調用C函數。在參考模型組件中,涉及UVM和C混仿的代碼實現如下:

5 仿真運行結果

以測試序列rand_test(隨機測試)為例分析驗證結果。該測試序列由序列發生器產生不定長度的2 000包密文或者明文數據,再由驅動器產生APB配置信號和AXI讀寫操作信號進行單次激勵,單次數據大小由隨機化的長度信號決定,可實現16的整數倍字節傳輸,加密或解密計算方式選擇由隨機化加解密標志信號決定。

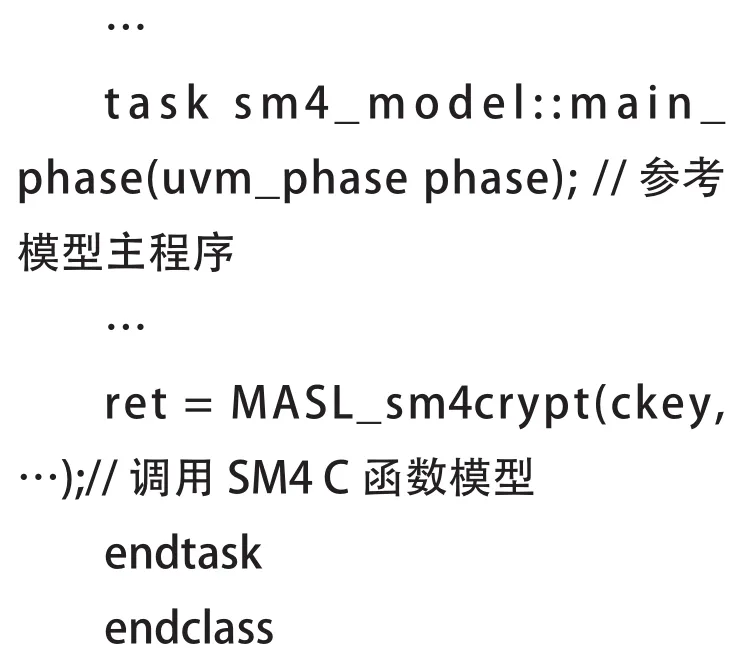

如圖3所示為該測試序列單次數據包的AXI讀數據仿真波形,根據APB端口配置的首地址,從地址0x10D0_0000開始,依次寫入64位數據字節長度、64位加解密標志(0:加密,1:解密)、128位密鑰和加解密數據。

圖3 AXI讀數據仿真波形Fig.3 Simulation waveform of AXI reading data

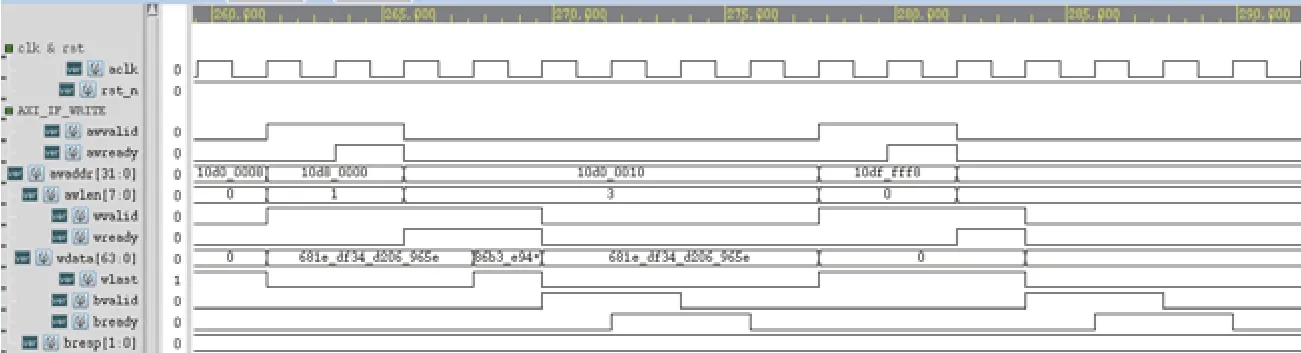

如圖4所示為該測試序列單次數據包的AXI寫數據仿真波形,加解密之后的數據寫入地址由0x10D8_0000開始,全部計算完成并將計算結果成功寫出后,計算結果標記地址0x10DFFFF8處標記為0,至此單次數據包激勵完成,驅動器申請下一包數據進行驅動。

圖4 AXI寫數據仿真波形Fig.4 Simulation waveform of AXI writing data

測試序列的驗證結果對比報告會實時在終端中打印出來并形成文件保存,如圖5所示為仿真報告,打印信息表明測試序列經過2 000次成功對比,沒有警告、一般錯誤或嚴重錯誤,該測試序列通過驗證。經過隨機測試,對未覆蓋的地方采用定向測試,遍歷FIFO空滿邊界,復位測試,并構造錯誤序列驗證待測設計是否能及時檢測并做出相應報警,經覆蓋率統計分析得到代碼行覆蓋率為98%,決策覆蓋率為95%,功能覆蓋率達到100%,因為設計中存在一些實際運行中并不會出現的冗余情況,行覆蓋率和決策覆蓋率沒有達到100%,與設計人員確認并排除此情況后,覆蓋率符合指標。

圖5 仿真報告Fig.5 Simulation report

6 結論

本文以SM4加解密算法模塊為驗證對象,采用隨機測試向量并利用DPI接口內嵌C函數模型構建了基于UVM的自動化實時監控驗證平臺,實現UVM和C模型的聯合仿真。從SM4參考模型的代碼量來看,C函數的代碼量為390行,嵌入C模型后的UVM參考模型代碼量僅有100行,大大簡化了驗證平臺復雜度,縮短驗證周期。而隨機測試序列和自動實時監控,區別于傳統仿真,驗證平臺可以有序完成不同的測試場景,避免對驗證平臺的大量修改和單純用人工檢查,保證驗證周期的完備性。該驗證平臺結構組件封閉獨立具有復用性,可實現CPLD/FPGA和芯片硬件功能驗證平臺從模塊級到系統級的移植。