基于FPGA的OOK可見光通信系統仿真與實現

王許浦 孫曉紅 薛琦

摘? 要: 根據OOK(開關鍵控)的原理,基于FPGA開發板用Verilog HDL語言實現OOK調制、解調和同步模塊,并通過邏輯分析儀進行仿真。配合驅動電路、光電探測電路和放大電路等實現了整套可見光通信系統的設計,最后通過搭建實驗平臺進行測試,測試結果表明,收發電路通信距離達到12 cm,系統傳輸速率達到3.125 Mb/s。

關鍵詞: 可見光通信; FPGA; OOK; 驅動電路; 光電探測器; 位同步

中圖分類號: TN929.1?34? ? ? ? ? ? ? ? ? ? ? ?文獻標識碼: A? ? ? ? ? ? ? ? ? ? ? ? ? 文章編號: 1004?373X(2020)17?0025?04

Abstract: According to the principle of OOK (on?off keying), the modules of modulation, demodulation and synchronization are realized by using Verilog HDL language and FPGA board, and simulated by logic analyzer. The whole set of visible light communication system is designed with driving circuit, photoelectric detection circuit and amplification circuit. The experiment platform was built to test the system. The test result shows that the communication distance of the transceiving circuit can reach 12 cm, and the transmission rate can reach 3.125 Mb/s.

Keywords: visible light communication; FPGA; OOK; drive circuit; photo detector; bit synchronization

0? 引? 言

可見光通信技術可以解決傳統無線通信存在頻譜資源緊缺、信息不安全以及電磁干擾等問題,同時,它在高速通信的同時又具備節能照明的特點而被廣泛關注和研究[1?3]。目前研究可見光通信的很多,但是基于FPGA的可見光通信系統研究還并不多,由于FPGA具備運行速度快、管腳多和設計靈活等優點,因此,將可見光通信技術與FPGA相結合可以大大提高系統的性能[4?5]。本文基于FPGA開發板,運用Verilog HDL語言并結合電路設計搭建起一套可見光通信系統并進行驗證。

1? 可見光通信系統整體設計

本系統發射端采用Alter公司Cyclone系列芯片,型號為EP4CE15F23C8的FPGA開發板對信號進行數字處理及時序控制,接收端采用Alter公司Cyclone系列芯片,型號為EP4CE30F23C8的FPGA開發板對接收的信號進行處理。重點在于OOK(On?Off Keying)的調制解調、同步等算法與Verilog HDL語言實現,以及發送電路設計和接收電路中互阻放大電路、同相積分器等電路的設計。其中,系統發射端的信號為FPGA產生的0,1周期符號序列,通過OOK調制到白光LED驅動電路中;系統接收端包括光電轉換模塊、放大電路模塊和FPGA解調模塊等,如圖1所示。

2? 基于OOK的可見光通信系統發射端的設計

2.1? 基于Verilog的OOK調制

OOK是二進制振幅鍵控(2ASK)的一個特例。振幅鍵控是利用載波的幅度變化來傳遞數字信息,其頻率和初始相位保持不變。載波可以是正弦波,也可以是方波,本文傳輸碼元用的是方波。對于2ASK,當發送碼元1時,載波振幅取[A1];當發送碼元為0時,碼元振幅取[A2]。根據載波的幅值區分碼元信息,可表示為:

OOK調制即將2ASK中一個振幅取0,另一個非0。OOK調制后波形示意圖如圖2所示。

基于上述原理,OOK調制本質上為載波信號與輸入信源相乘。因此在設計的過程中,需要解決以下問題:信源如何產生,載波如何產生,合適參數的設置。

調制信號是通過FPGA內部自帶的時鐘信號的上升沿進行觸發來產生的,所用的FPGA開發板內部的時鐘頻率為50 MHz,程序中定義了一個寄存器將調制信號的頻率降低到光電轉換器識別范圍內。程序中設置00100111為一個周期信號。

載波信號是方波,用“0”和“1”的高低電平來表示,所以它直接和調制信號相乘得到已調信號。它是由AX515開發板50 MHz的時鐘頻率16分頻得到,也就是方波的一個周期需要16個時鐘信號的觸發,即方波頻率為3.125 MHz。

2.2? 驅動電路的設計

根據發光二極管的放電特性,LED上升沿不是垂直的,而是有一個慢慢上升的過程,所以傳輸方波信號的速率受到一定限制。實驗過程中通過電路修改嘗試補償存在的問題,結果表明需要選擇合適的電容值對LED限流,才能使發光二極管發射出比較完美的方波信號。電路圖如圖3所示。

圖3是發送電路,主要由電容和SI2300MOS型三極管構成,選用此三極管放大功率驅動LED發光,雖然有較大的功耗,但是抗干擾能力強,同時電路簡單。

3? OOK可見光通信系統接收端的設計

3.1? 接收電路設計

圖4是接收電路硬件電路圖,主要由光電探測器、運放OPA847構成的互阻放大器、運放OPA335構成的同相積分器、芯片TLV3501構成的判決電路等模塊構成。

圖4中,[R1],[C1],Z1用于提供一個2.7 V穩定的參考地電壓;運放芯片U1,[R2]構成互阻放大器,U1采用OPA847,反饋電阻的取值決定了模擬部分的增益,[R2]采用0402封裝,以盡可能減小寄生電容。依靠此電阻存在的寄生電容可以抑制振蕩,同時,較小的寄生電容有利于提升系統高頻特性。運放U2,[R3],[R4],[R5],[R6],[C2]構成同相積分器。對于一般的互阻放大電路往往難以兼顧高靈敏度和寬動態范圍:若電路的增益高、靈敏度高,則放大電路在強光下容易飽和;反之,若要求能夠在強背景光下檢測信號,則電路增益必須減小。本電路增加了此積分器設計兼顧了高增益和高抗飽和能力,使得系統也能夠在室外環境下正常工作。同時,此積分器也使得整個電路具有高通特性,常見的50 Hz工頻干擾光(如日光燈光)能夠得到比較有效的抑制。VR1,VR2,VR3是穩壓器,保證電路電壓穩定,U3構成判決電路,通過TLV3501能有效進行高低電平的判決,為解調作準備。

3.2? 基于Verilog的OOK解調

光電探測器把光信號轉換成電流的形式傳輸,經過互阻放大器后轉變為電壓的形式,然后經過判決等模塊后將得到的信號送入型號為AX530的FPGA開發板中,利用數字鎖相環實現位同步,得到每一位信號的判決時刻,把位同步信號作為解調用的工作時鐘解調出原信息。本文的解調原理框圖如圖5所示。

本文采用數字鎖相環實現采樣頻率的同步。解調的思想是根據OOK調制信號的特點,即在高電平調制的地方有載波,而低電平調制的地方沒有載波。所以通過載波同步信號采樣恢復出調制信號,但是采樣時刻要和數據位同步,在這里通過數字鎖相環實現與載波信號鎖相后,再利用鎖相后信號的下降沿采樣已調信號來實現OOK的解調,數字鎖相環Netlist視圖如圖6所示。

為了提高解調采樣數據的準確性,圖6是解調時設計的鎖相環Netlist視圖,這里用數字鎖相環對載波相位鎖定后,其下降沿是數據比特(modata)的中心采樣來減小解調的誤碼率。數字鎖相環由異或門鑒相器(XOR_pd:u1)、加減脈沖計數器(Kcounter:u2)、脈沖增減模塊(idcounter:u3)、控制器(利用clk對fin脈沖的測量并給出[N]值模塊counter_[N]:u4)、分頻器([N]分頻模塊div_[N]:u5)等5個模塊組成。輸入信號與分頻信號通過鑒相器模塊后,鑒相器根據輸出信號相位是否超前(滯后)于輸入信號,從而產生加減脈沖計數器的計數方向用來控制信號,加減脈沖計數器根據計數方向控制信號來調整計數值。當控制信號為高電平時進行減計數,當計數值到達0時,就可以輸出借位脈沖信號;反之,當控制信號為低電平時進行加計數,當計數值達到預設的[K]模值時,此時輸出進位脈沖信號,脈沖增減電路則根據借位脈沖和進位脈沖信號在輸出電路信號中進行脈沖的增加和減少操作,調整輸出信號的頻率持續進行上面的過程進行調整,則分頻器最終輸出信號與輸入信號頻率一樣,即作為解調使用的位同步信號。

4? 調制解調仿真分析

編寫一個頂層文件例化調制、解調模塊后生成的RTL視圖,如圖7所示。圖7中,two_ASK:U_mo為生成的調制模塊,ASK_two:U_demo為生成的解調模塊。

Quartus Ⅱ中的邏輯分析儀觀察到的調制解調的整個過程如圖8所示。其中,sig_S為基帶信號,carriers為載波(頻率為3.125 MHz),modata為調制信號,pll_carriers為采樣頻率(和載波同步),demodata為解調信號。從圖8中可以看出,基帶信號00100111為一個符號周期,解調出來的依然是00100111,解調結果正確。

5? 實驗測試及分析

本節主要對搭建的基于OOK的可見光通信系統進行測試,包括發送電路、接收電路和調制解調過程的測試以及收發電路通信距離、通信速率的測試,目的是在通信距離范圍內測試搭建系統的最大傳輸速率。

圖9a)為搭建起來的可見光通信系統實驗平臺,包括發射端、接收端、信號發生器以及示波器,值得說明的是,程序主要用USB?Blaster由FPGA開發板的JTAG口燒錄開發板。圖9b)主要是系統模塊介紹,發射端包括發送板與驅動電路,接收端包括接收板與接收電路。

5.1? 收發端電路測試

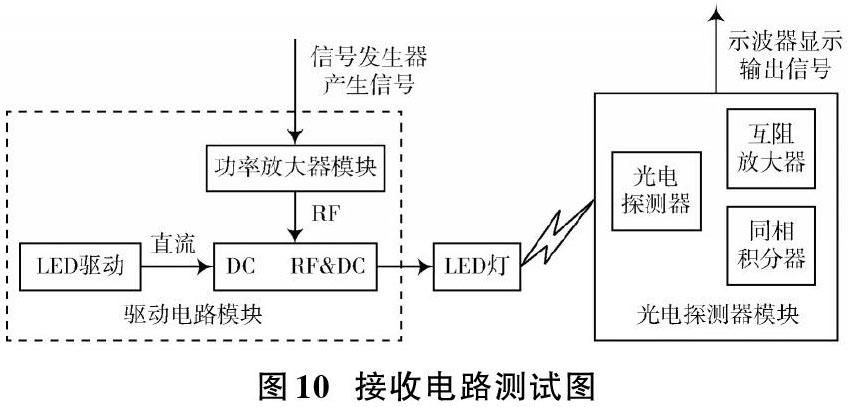

如圖10所示,此次接收電路的測試主要由信號發生器和示波器完成,驅動電路上的LED燈由直流偏置電流和信號發生器產生的信號加載到LED燈上共同驅動發光,經過接收電路中光電探測器探測到的信息并且經過放大等處理后輸出在示波器上顯示。

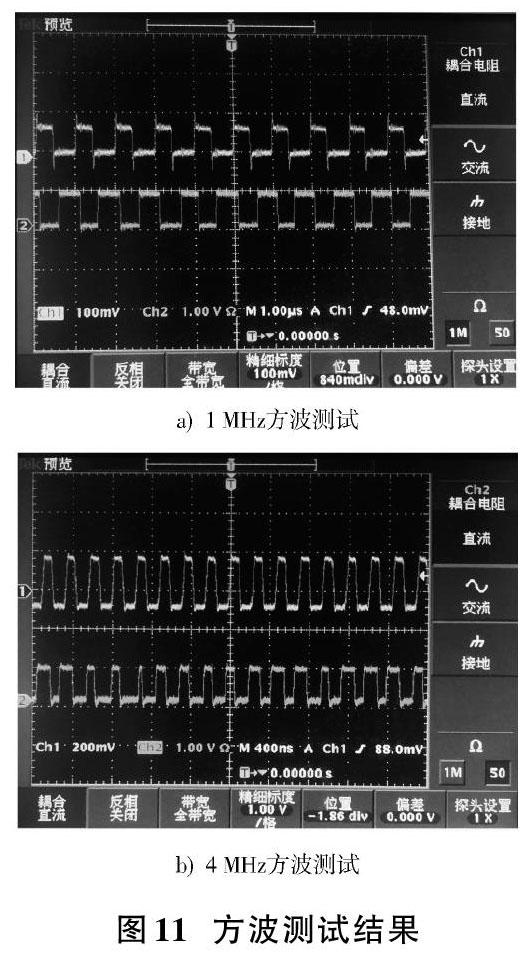

圖11是根據圖10方式測試的結果,圖11a)是信號發生器產生的頻率1 MHz未經過發送、接收電路板處理和經過發送、接收電路板處理的信號,其中,上方的黃線是發送端信號,電壓為60 mV,下方的藍線是接收端信號,經過電路處理放大后電壓為1 V。圖11b)是信號發生器產生的頻率4 MHz未經過發送、接收電路板處理和經過發送、接收電路板處理后的信號,其中,上方的黃線是發送端信號,電壓為280 mV,下方的藍線是接收端信號經過電路處理放大后的信號,電壓為1 V,經過測試表明,接收電路板可以達到系統需求。

圖12是根據圖10方式測試的結果,用信號發生器產生頻率4 MHz的方波信號來測試收發電路通信距離。圖12a)~圖12d)是通信距離分別為5 cm,12 cm,15 cm,22 cm時信號發生器產生的信號波形和經過收發電路處理后接收到的信號波形。其中,上方的黃線是信號發生器產生的信號波形,下方的紫線是經過收發電路處理后接收到的信號波形,可以看出,收發端電路的距離在12 cm范圍內能很好地實現信號的接收,超過12 cm接收端接收到的信號波形會出現錯誤信息,發生誤碼,當收發端電路的距離為22 cm時,接收到的信號波形發生變化,顯然不是要接收的信息。

5.2? 系統測試

通過前面收發電路通信速率和通信距離的測試,本次主要在最佳通信距離12 cm范圍內進行測試。圖13中,上方的黃色線為FPGA產生的載波為3.125 MHz的OOK已調信號,電壓值為220 mV,經過發送板電路的處理后驅動LED發光,下方的紫色線是光電探測器將探測到的光信號轉變成電流信號,經過互阻放大器、同相積分器處理和TLV3501判決輸出的信號作為接收端FPGA開發板要解調的信號,電壓值為3.3 V。其中,每8個數據符號(00100111)為一個周期,可以看出只有輸入信號“1”時載波才會與OOK理論仿真圖8一致,能夠實現很好地發射和接收,此系統驗證成功。

6? 結? 語

本文主要通過FPGA設計了一個OOK的可見光通信系統進行實驗驗證。首先運用Verilog HDL語言進行調制解調以及同步模塊的編寫,并借助軟件Quartus Ⅱ中的邏輯分析儀連接FPGA開發板進行仿真驗證,然后對收發電路的傳輸速率和通信距離進行測試,系統測試結果表明,傳輸速率達到3.125 Mb/s,收發電路在12 cm范圍內能很好地完成信號接收。

注:本文通訊作者為孫曉紅。

參考文獻

[1] 王永進,王金元,朱秉誠.可見光通信最新研究進展[J].郵電設計技術,2017(8):1?6.

[2] 遲楠.讓Li?Fi點亮你的網絡[J].中國經濟報告,2016(1):116?118.

[3] 鄔江興.可見光通信在中國[J].中國科技產業,2014(10):32?34.

[4] 梁景熙,劉宏展.2ASK可見光通信系統的硬件設計與實現[J].現代電子技術,2015,38(21):56?59.

[5] 梁景熙,張劍鳴,劉宏展.基于FPGA的PPM可見光通信系統的仿真與實現[J].光通信技術,2015,39(9):57?59.

[6] 李茹,張濤,朱秋煜,等.基于FPGA的OOK可見光通信系統設計與實現[J].工業控制計算機,2016,29(12):106?107.

[7] 武夢龍,郭佳,劉文楷,等.LED作為收發元件的雙向可見光通信系統方案及實現[J].光學學報,2018,38(4):62?68.

[8] 楊宇,劉博,張建昆,等.一種基于大功率LED照明燈的可見光通信系統[J].光電子激光,2011,22(6):803?807.

[9] 畢成軍,陳利學,孫茂一.基于FPGA的位同步信號提取[J].現代電子技術,2006,29(20):121?123.

[10] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008.