C波段小型化雙通道變頻收發模塊設計

吳元清,解效白,郭 睿,朱鴻浩

(中國船舶集團有限公司第八研究院,南京 211153)

0 引 言

隨著相控陣體制在雷達等軍用電子裝備中的廣泛應用,需要研制生產大量小型化、高密度、多功能的微波模塊。這對組裝和互連技術提出了越來越高的要求。微組裝技術(Micro-assembly Process Technology, MPT)以其高密度、高速度、高可靠性的特點成為了當今軍品電子技術發展的主流。它是在高密度多層互連基板上采用微焊與封裝工藝把構成電路的各種微型元器件組裝起來。由于微組裝技術采用的芯片大多為無封裝的裸露芯片,較封裝芯片而言具有體積小、功能全、集成度高等優點,進而極大地提高了微波模塊的集成度。由組裝技術發展規律來看,組裝密度每提高10%,模塊體積可減少40%~50%,質量減少20%~30%。[1]因此,微組裝技術對于減小微波功能模塊的體積與質量,以及滿足雷達裝備小型化、輕量化、數字化具有重要意義。本文基于微組裝技術研制一款應用于XX項目的C波段小型化雙通道收發變頻模塊。

1 鏈路主要性能指標設計

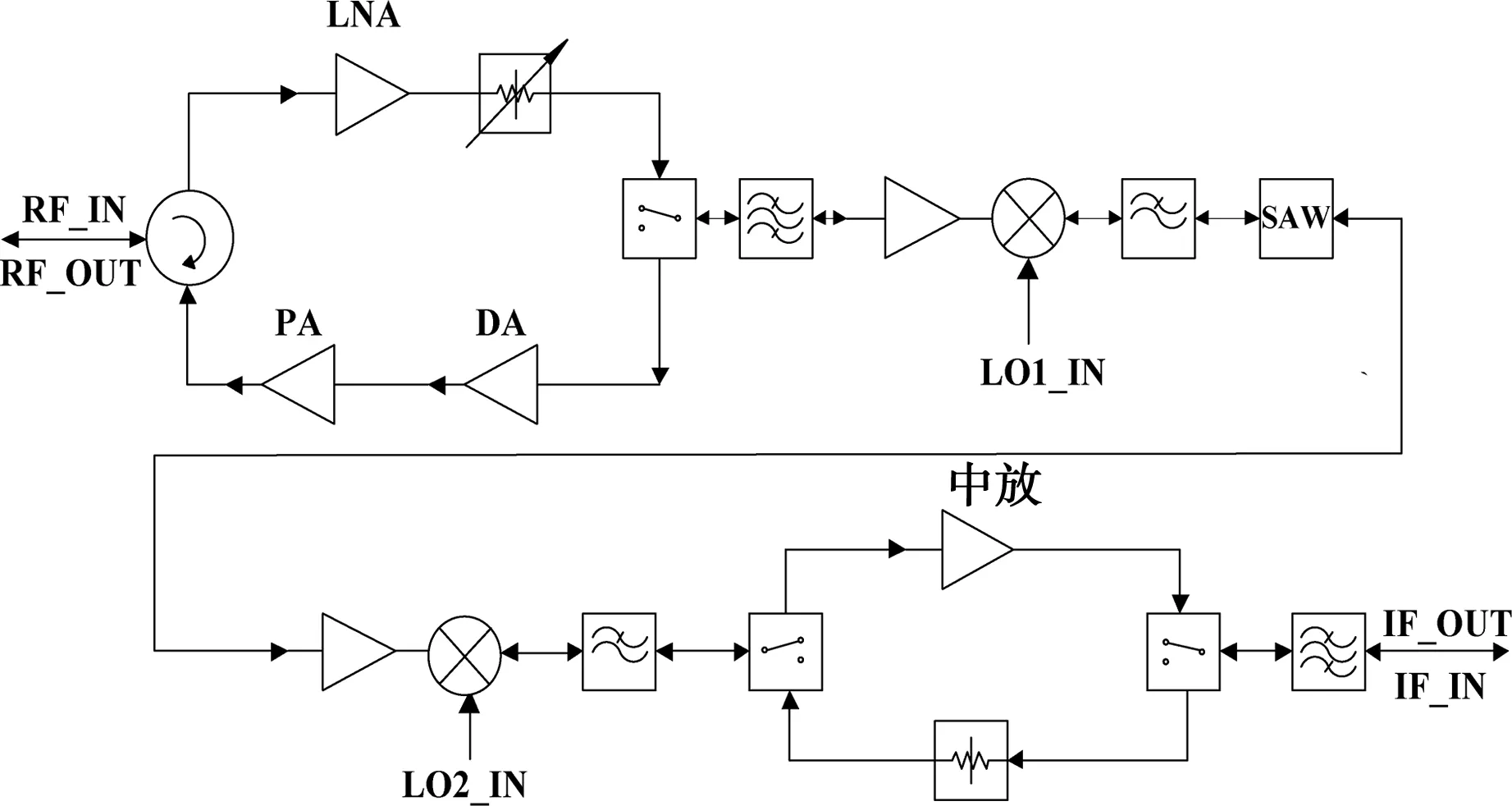

模塊采用二次變頻超外差結構實現射頻頻率與中頻頻率的相互變換。模塊單通道主要鏈路框圖如圖1所示,主要包括環形器、限幅低噪放、驅放、功放、第1次混頻多功能電路、第2次混頻多功能電路,配以相關的放大器與濾波器。

圖1 模塊單通道主要鏈路圖

1.1 下行增益與噪聲系數設計

射頻模塊多個芯片級聯總增益按下式計算:

GRF(dB)=G1(dB)+G2(dB)+…+Gn(dB)

(1)

多個芯片級聯總噪聲系數按下式計算:

(2)

下行增益分配時主要考慮鏈路噪聲系數和抗飽和干擾能力,將增益均勻分配在每一級鏈路中,并在末級使用固定1 dB壓縮點的放大器對接收支路的壓縮點進行固化。由公式(2)可知,模塊第1級電路(環形器)的噪聲系數對整個鏈路的噪聲大小起著決定性的作用。為了獲得較小的鏈路噪聲系數,模塊選取了損耗為0.3 dB的環形器作為系統的第1級電路;吸收式限幅低噪聲放大器載片作為系統第2級電路,有著1.2 dB的低噪聲系數與28 dB的高增益特性,使模塊具有較低噪聲系數的同時為后級電路提供了一定增益。為了進一步降低系統噪聲系數,在第1次混頻前系統增加了一級射頻放大器。但是,當混頻前射頻電路增益過大時(一般不超過35 dB),系統受到的外部干擾將會大大提升,繼而損失系統的動態范圍。因此,增益、噪聲系數與動態范圍三者必須折中考慮,選取適合系統的最佳值。此外,中頻放大器的噪聲系數對鏈路噪聲也有一定影響。設計過程中在保證鏈路增益設計的前提下需要選擇噪聲系數相對較低的放大器芯片以降低系統噪聲系數。

1.2 帶內平坦度設計

模塊采用MMIC(微波集成電路芯片)在微波多層混壓印制板上實現模塊小型化與集成化的特性。考慮到頻帶內平坦度的要求,通過選取高平坦度芯片以降低帶內增益起伏;優選多功能芯片以降低芯片種類,減少由于芯片之間金絲互連的裝配誤差引起的帶內及通道間的增益不一致性。對于基于微組裝工藝的模塊,模塊內環形器、限幅低噪聲放大器、驅動放大器以及功率放大器均以焊料燒結的形式與模塊殼體直接互連。該互連方式既保證了器件的良好接地性能,對于大功率器件其散熱效果也遠好于螺釘安裝方式。但是,在燒結器件與多層混壓印制板互連時金絲互連引入的額外電感易導致傳輸線失配,繼而導致鏈路帶內平坦度的惡化。本節采用三維電磁仿真軟件HFSS對燒結器件與微波多層板之間的過渡連接進行建模與仿真優化,如圖2所示。

圖2 燒結器件與微波多層板間互連三維模型

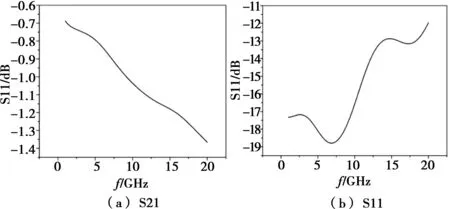

雙層印制板選用的是相對介電常數為3.48、厚度為0.254 mm的Rogers 4350B板材。微波多層板選用的8層混壓板,其板厚分別為0.254/0.2/0.127/0.12/0.1/0.12/0.254 mm。其中,多層板中第1、2層與第7、8層選取的是厚度為0.254 mm的Rogers 4350B板材,第3、4層選取的是厚度為0.127 mm的Rogers 4350B板材,第5、6層選取的是厚度為0.1 mm的FR4板材。微波信號傳輸板材與PP片混壓成8層印制板,雙層板與多層板間采用金絲實現信號互連。全波仿真結果如圖3所示。

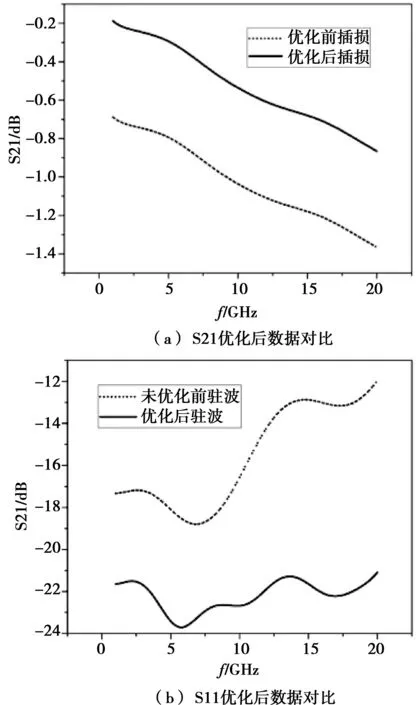

圖3 互連模型S參數

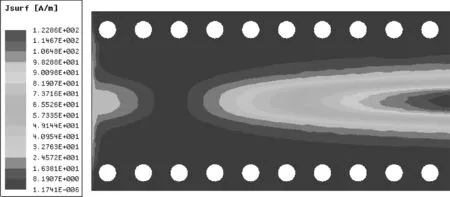

當頻率小于7.5 GHz時互連傳輸性能尚優,而隨著頻率增加傳輸性能迅速惡化。圖4所示為多層板電流傳輸性能。多層板回流電流主要通過板邊的過孔進行傳輸,增加了信號回流路徑以及平面的寄生電感,導致高頻處傳輸線的互連失配。

圖4 多層板電流傳輸性能

為了改善微波多層板與雙層載片互連的傳輸特性,首先通過在傳輸線附近引入額外電容以補償互連時電感失配效應;其次采用板邊包金技術,使多層板的回流電流通過良好的寬平面進行傳輸。優化后仿真模型與電流傳輸性能如圖5所示。

圖5 優化后仿真模型與多層板電流傳輸性能

如圖5所示,采用板邊包金工藝后電流密度集中在微帶線下方直接通過良好的地平面傳輸,減少了電流回流路徑。微帶線互連傳輸優化仿真結果如圖6所示。

優化后在DC~20 GHz的頻段內插入損耗明顯降低小于0.9 dB,在模塊需求頻段(C波段)插入損耗小于0.3 dB,且帶內駐波均小于-20 dBc,有效地提升了傳輸性能。

1.3 功率輸出設計

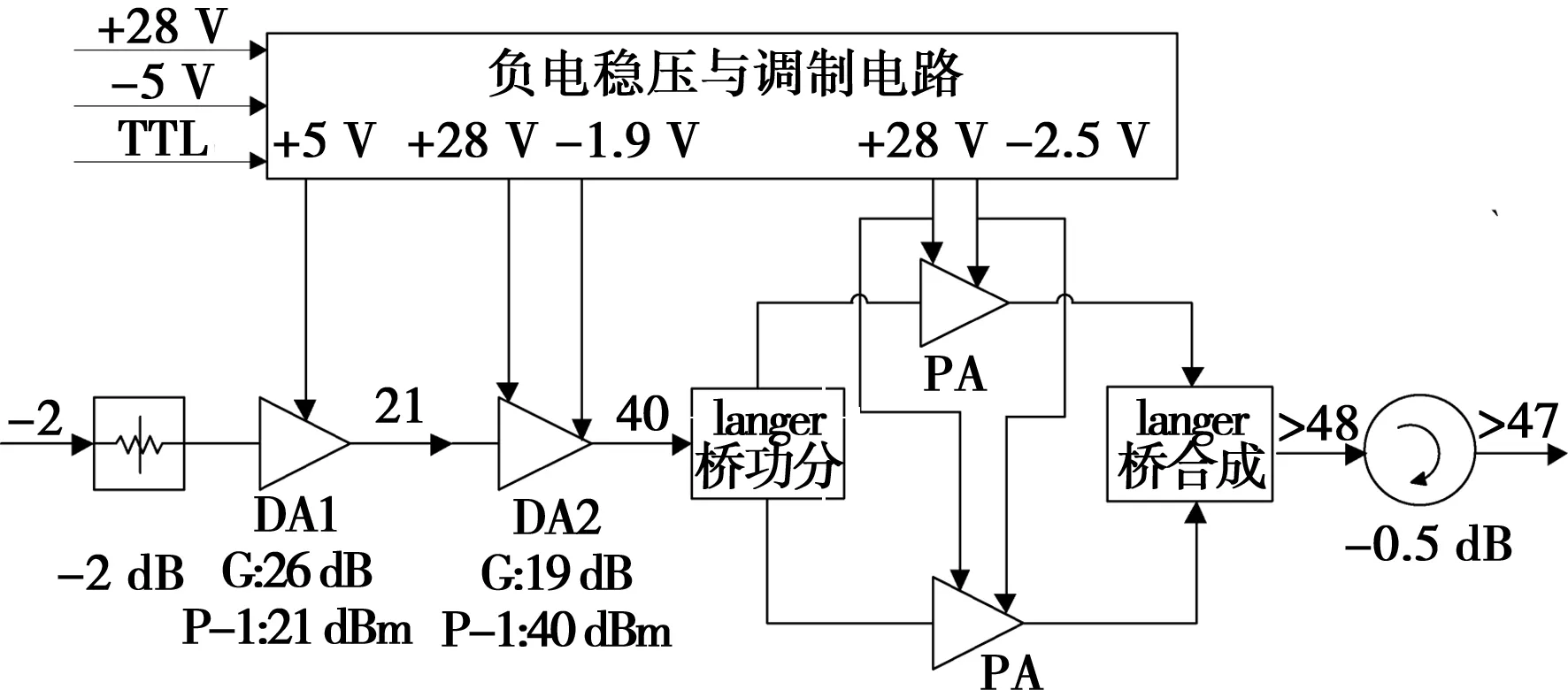

模塊采用3級放大器級聯的形式完成模塊輸出功率大于50 W的技術指標要求,如圖7所示。

-2 dBm的射頻信號經過衰減器后由第1級驅動放大器飽和放大至21 dBm,第2級驅動放大器由第1級驅動放大器推動飽和放大輸出至40 dBm(10 W)。為了改善驅動放大器與功率放大器的級聯匹配,選取了輸入輸出為Langer橋功分合成平衡式功率放大器

圖6 優化仿真結果

圖7 模塊單通道功率放大鏈路框圖

載片。該功放載片無需加入隔離器進行功放輸入駐波匹配,節約模塊布局空間的同時提高了第2級驅動放大器、功率放大器、環形器三者之間的級聯匹配,優化了功率放大器的諧波性能。

模塊功率放大鏈路采用+5 V、-5 V與28 V TTL電源共同供電。為了消除電源級聯產生的低頻調制信號對主輸出功率的干擾,模塊對驅動放大器與功放使用的28 V直流信號進行一對一單獨調制,實現了高電壓電源之間的物理隔離。調制電路具有負電保護功能,避免由于負電掉電后造成功率管的燒毀。對驅放2與功放使用的柵壓負電信號,采用柵壓穩壓芯片對-5 V分別進行穩壓,與電阻分壓相比能夠有效提高柵壓的穩定性,從而增加驅放和功放的可靠性。

1.4 組合干擾設計

如圖8所示,模塊組合干擾主要來源于第1次下(上)混頻干擾,第2次下(上)混頻干擾以及本振頻率間的組合干擾。

圖8 模塊混頻鏈路圖

對于第1、2次下混頻干擾與第1次上混頻干擾,近端雜散主要由聲表面波濾波器、中頻帶通濾波器進行濾除;對于遠端雜散,主要由LTCC低通濾波器與混頻器的雜波抑制性能共同抑制。模塊采用雙平衡混頻器,與其他混頻器相比具有組合干擾少、噪聲系數小、本振與射頻、中頻隔離度高的優點[2],在后端通過選取合適的濾波器級聯可以較好地實現模塊帶內雜散、鏡像頻率與中頻帶外抑制。

對于第2次上混頻干擾,通過ADS軟件計算,存在2LO1-5IF1雜散落在射頻帶內。模塊選取了對頻率為5IF1抑制性能較好的混頻1芯片,滿足模塊帶內雜散抑制要求。其余由第1次混頻產生的低頻雜散、本振頻率泄漏與鏡像頻率,主要由混頻器1的雜波抑制性能與選取高選擇性的MEMS射頻濾波器共同濾除。MEMS濾波器具有高Q值、體積小、易集成與可靠性高等優點。相同結構的MEMS濾波器體積是傳統腔體濾波器的1/220[3],有效提升了模塊的集成度。

對于下變頻本振頻率間干擾,通過ADS軟件計算,交調信號LO1~5LO2雜散落在中頻帶內,主要通過混頻器1與一中頻LTCC低通濾波器對LO1信號共同抑制以降低交調信號干擾。對于上變頻本振頻率間干擾,存在LO1~LO2信號落在射頻帶內,無法通過射頻帶通濾波器濾除。采用聲表面波濾波器對LO2信號抑制大于70 dBc,滿足模塊帶內雜散大于60 dBc的抑制要求。

1.5 電磁兼容設計

模塊在狹小的空間內完成雙通道兩次變頻上下行發射接收電路,包含射頻小信號與射頻大功率信號、一中頻信號、二中頻信號,以及一、二本振信號和來自T/R組件的數字控制信號。其信號種類復雜多樣,設計時主要從電源設計、屏蔽設計和濾波設計的方面考慮模塊內部的電磁兼容特性:(1)在電源輸入處進行濾波,阻止外部干擾信號從電源進入模塊;(2)對控制線信號進行RC濾波,防止線間信號相互串擾;(3)發射接收鏈路分時供電,發射時接收鏈路數控衰減器全開,避免在大功率信號發射時由于接收鏈路隔離度不夠造成環路自激;(4)一中頻、二中頻信號分腔設計,本振信號獨立隔腔設計,避免不同信號之間的空間串擾;(5)布板電路設計時走線方式上要避免不同信號之間的平行走線,降低走線間的耦合干擾;(6)模塊內蓋板采用蓋板隔墻一體式設計,避免由于加工精度造成模塊內部腔體不密閉,繼而引起大功率自激震蕩;(7)模塊內蓋板敏感頻率與大功率器件上方粘貼吸波材料,有效衰減射頻泄漏的能量。

2 實現與測試結果

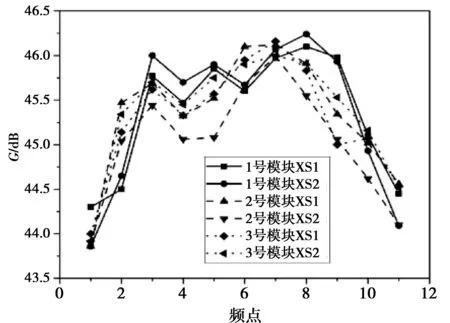

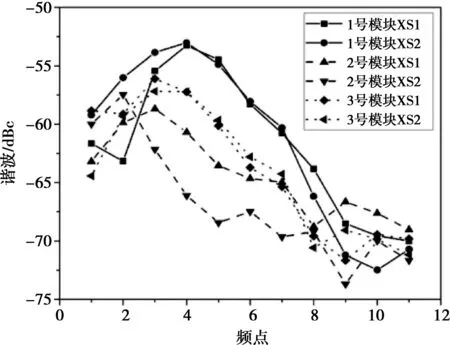

經過對模塊的合理布局與設計,模塊在55 mm*95 mm*10.8 mm的空間內完成雙通道收發變頻功能,實物圖如圖9所示。模塊經過高低溫、振動實驗,測試指標均滿足技術指標要求,3只模塊6個通道的增益、噪聲系數、上行輸出功率、二次諧波測試曲線如圖10、11、12、13所示。由圖10可知,模塊增益為45±1.1 dB。根據本文1.2節對模塊帶內平坦度進行優化。模塊下行帶內平坦度為±1.1 dB,較模塊技術指標±1.5 dB的要求有所提升。模塊噪聲系數均小于1.7 dB,上行輸出功率大于47.6 dBm(55 W),二次諧波抑制大于53 dB,具有一定的設計余量,實測指標均優于技術指標要求。此外,模塊在帶內雜散抑制可控制在60 dBc以上,帶外雜散抑制可控制在65 dBc以上,滿足技術指標要求。

圖9 C波段T/R模塊實物圖

圖10 增益測試曲線圖

圖11 噪聲系數測試曲線圖

圖12 輸出功率測試曲線圖

圖13 二次諧波測試曲線

3 結束語

本文介紹了一種基于MMIC與微組裝工藝技術的C波段雙通道T/R模塊的設計方法。MMIC芯片體積小、功能全、集成度高等的優點大大地降低了微波功能模塊的體積與質量,有效滿足了現代化雷達高密度、輕量化、高可靠性的要求。經過充分的試驗驗證,模塊的性能水平達到了預期的研制目標,滿足某C波段旋轉相控陣雷達的使用需求。