半導體工藝中二氧化硅的刻蝕速率研究

高 益

(重慶航天職業技術學院電子工程系,重慶400021)

1 引 言

大規模半導體集成電路的廣泛應用,要求MOSFET 器件的溝道長度越來越小,目前已經縮小至深亞微米范圍,向納米逼近[1]。傳統的平面化技術,只能實現局部平面化,然而對于微小尺寸的電子器件,必須實現全局平面化以滿足加工要求。平坦化工藝定義,簡單來說就是在晶片的表面保持平整平坦的工藝。上世紀90 年代的新型化學機械拋光技術,從加工性能和速度上都可以滿足硅片圖形的加工要求,幾乎是當前唯一可以提供全局平面化的技術。目前在半導體制造工藝中存在兩種基本的刻蝕方法:濕法刻蝕和干法刻蝕。濕法刻蝕一般用在大尺寸的情況下,用來腐蝕硅片上某些層或去除干法刻蝕后的殘留物[2]。干法刻蝕是把硅片表面曝露于特定氣態中產生等離子體,利用等離子體通過光刻膠中開出的窗口,進而與硅片表面發生化學反應,達到去掉曝露的表面材料的效果。

2 半導體刻蝕工藝

半導體刻蝕工藝就是使用物理、化學或兩者兼用的方法,有目的性地把沒被抗蝕劑掩蓋的那一部分薄膜層除去,這樣就可以在薄膜上得到與抗蝕劑膜上一模一樣的圖形。刻蝕工藝可以分成干法刻蝕工藝與濕法刻蝕工藝[3]。通常,利用某些反應氣體和等離子體進行薄膜刻蝕就是干法刻蝕工藝;利用化學試劑與被刻蝕材料發生化學反應進行刻蝕就是濕法刻蝕工藝。

2.1 濕法刻蝕特點

濕法刻蝕是傳統的刻蝕方法,具體原理是把硅片浸泡在某種化學試劑或試劑溶液中,讓沒有被抗蝕劑掩蓋的那一部分薄膜表面與試劑發生化學反應而被除去。其優點主要在于操作比較簡單方便、對設備要求較低、易于大批量生產,并且刻蝕的選擇性也較好。但是由于化學反應的各向異性較差,橫向的鉆蝕會使刻蝕剖面出現圓弧形,這讓精確控制圖形變得非常困難。濕法刻蝕的另一問題是抗蝕劑在溶液中,特別在較高溫度的溶液中易受破壞,使得掩蓋效果不理想,所以對于那些只能在高溫下刻蝕的薄膜要采用更加復雜的掩蔽方式。

2.2 干法刻蝕特點

干法刻蝕是一種利用等離子體進行薄膜刻蝕的工藝。當氣體以等離子體形式存在時,等離子體中的這些氣體活性比常態下要強,如果根據被刻蝕材料的不同,選擇合適的氣體,就可以更快地與材料進行反應,實現化學刻蝕去除的目的。還可以利用電場對等離子體進行引導和加速,使它具備一定的能量,再用于轟擊被刻蝕材料的表面時,即可將其原子擊出,這樣就達到了利用物理的能量轉移來實現刻蝕的目的。

干法刻蝕具有精度高、各向異性、刻蝕均勻性好的優點,滿足半導體器件微細加工的要求,是目前主要的刻蝕方式。

反應離子刻蝕是由化學和物理相結合的方法,在真空中利用氣體等離子進行刻蝕[4],利用離子能量讓被刻蝕層的表面形成易刻蝕層以促進化學反應。繼而用電場加速的高能離子轟擊被刻蝕的材料,以提高被刻蝕材料表面的活性,這樣就加速與化學活性刻蝕反應基團的反應速度,獲取很快的刻蝕速度。在化學和物理反應的相互促進下,反應離子刻蝕就具有很大的優越性,體現在:良好的各向異性、高選擇比、較快的刻蝕速率。

3 刻蝕機制

3.1 刻蝕工藝原理及流程

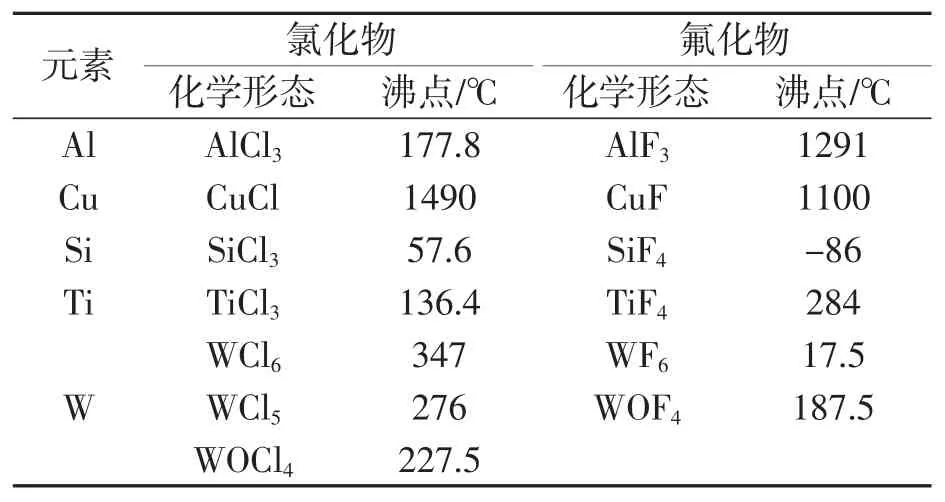

刻蝕涉及一系列物理及化學方法的應用:物理方式通過正離子高速轟擊表面的濺射刻蝕;化學方式通過等離子體產生的反應物與表面相互作用產生揮發性產物。將二者結合的反應離子刻蝕常用的刻蝕氣體為含鹵素的物質,如 CF4、SiF6、Cl2、HBr 等,再加入添加氣體如:O2,H2,Ar 等。常用刻蝕氣體可歸納為表1。

表1 常用刻蝕氣體

刻蝕工藝的大致流程可歸納如下:

生成等離子體刻蝕反應物→反應物通過擴散的穿過滯留氣體層到達表面→反應物被表面吸收→通過化學反應產生揮發性化合物→化合物離開表面回到等離子體氣流中,被抽氣泵抽出。

基于這一流程,對具體條件參數進行調節,即可設計出適應不同工藝要求的刻蝕工藝。

3.2 刻蝕氣體選擇

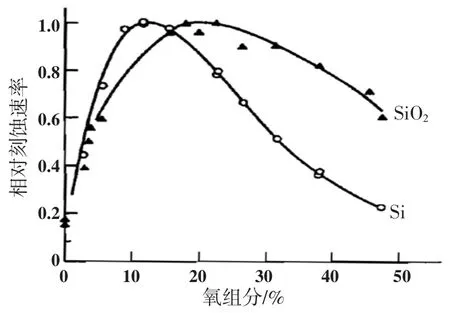

在刻蝕工藝中,用CF4和O2來刻蝕擴散后的硅片,這個反應需要一個凈正能量。CF4不會直接刻蝕硅,只有當等離子體高能量的電子碰撞使CF4分子分裂產生自由的氟原子和分子團,從而形成SiF 來達到這一目的。在進行多晶硅柵電極的刻蝕時,就需要下層柵氧化膜具有高選擇比,所以反應氣體可選用Cl2或SF6[5];刻蝕單晶硅的氣體可以用SiCl4/Cl2;刻蝕SiO2氣體可選用CF4/H2;刻蝕Al 的氣體可選用 BCl3、Cl2或 SiCl4[6];刻蝕 Si3N4的腐蝕氣體可用CF4/O2、SF6/O2;刻蝕 W 的氣體可用 SF6或 CF4;對鍺材料,含F 的氣體是非常有效的。因為氧氣與碳原子會產生反應生成CO2,如果從等離子體中減少C,而增加F 的濃度,就會提高對硅的刻蝕速率。比如向CF4等離子體中每增加12%的氧氣,F 濃度會增加一個數量級,這樣的話對硅的刻蝕速率將增加一個數量級。具體的影響程度如圖1 中的曲線所示。

圖1 添加氧對腐蝕速率的影響

由曲線可以看出在CF4腐蝕氣體中加入少量O2將會提高Si 和SiO2的刻蝕速率。

4 反應離子刻蝕速率研究實驗

為詳細考查反應離子刻蝕速率在不同工藝條件下的規律性,設計相關實驗進行研究。先測量SiO2薄膜厚度,然后進行反應離子刻蝕工藝。用電場加速的高能離子轟擊被刻蝕材料,因電壓差較大,使得正離子朝向晶片盤漂移,進而與待蝕刻的材料碰撞。此時離子與薄膜表面上的材料發生化學反應,也通過轉移一些動能敲除掉了部分的材料。因反應離子的大部分都是垂直傳遞的,所以反應離子蝕刻可以產生非常好的各向異性的蝕刻形貌輪廓。

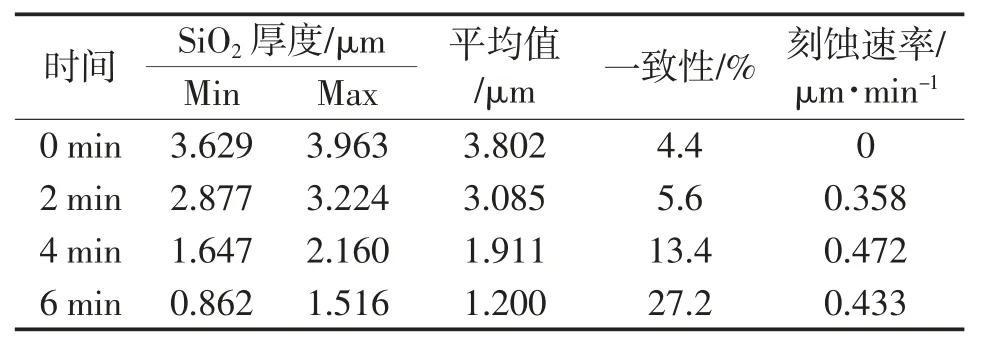

刻蝕完畢后, 再對剩余的SiO2薄膜厚度進行測量[7]。由兩次測得的厚度差算出在一定時間內刻蝕掉的SiO2薄膜厚度, 這樣就能定量研究刻蝕速率和均勻性等參數。實驗得到的具體數據如表2 所示。

表2 實驗測試數據

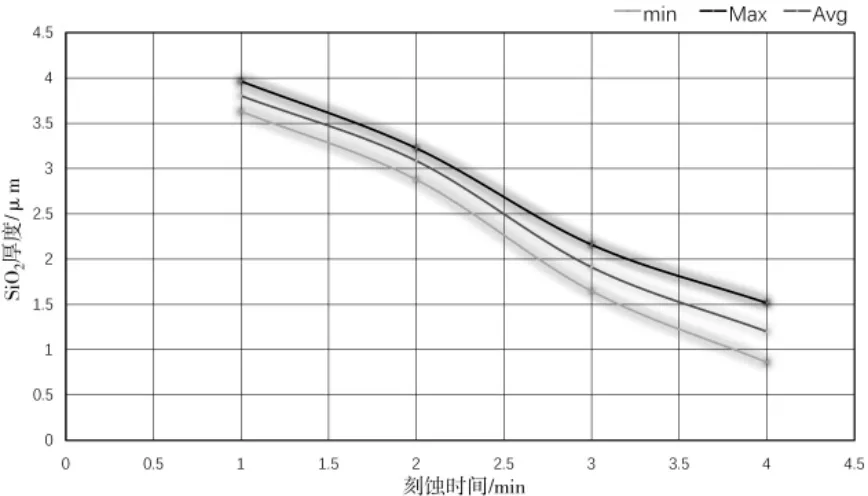

在通常情況下, 反應離子刻蝕速率的均勻性可用一個參數U 來衡量[8],即由所測刻蝕掉的二氧化硅薄膜厚度的Max 和Min 之差,比上2 倍的所測的所有值的平均值。氧化層厚度與刻蝕時間的關系的實驗結果如圖2 中曲線所示。由圖可見,在反應離子刻蝕中SiO2均勻性隨著刻蝕時間的增加而變差。

圖2 SiO2 厚度與刻蝕時間關系曲線

5 結束語

在半導體制造技術中,目前主要的蝕刻工藝還是反應離子刻蝕。在真空中利用氣體等離子來進行刻蝕,利用離子促進化學反應來實現各向異性刻蝕,同時離子還可起到清潔刻蝕材料表面的作用。基于對半導體刻蝕工藝和刻蝕機制的理論分析,設計進行了反應離子刻蝕速率研究實驗。從實驗得到的數據驗證了刻蝕均勻性與時間、氧化層厚度等參數關系的規律性,可用于最佳刻蝕工藝條件的摸索,進而通過優化控制刻蝕時間,獲得較高的圖形質量。