一種FIR濾波參數可調的電壓采集模塊設計

楊 旭,徐巧玉,王軍委,周新穩

(1.河南科技大學 機電工程學院,河南 洛陽 471003;2.洛陽銀杏科技有限公司,河南 洛陽 471003)

0 引言

在電壓信號采集過程中,由于電路設計、工作環境等原因,采集到的信號中通常包含著與信號無關的高頻噪聲。在多種數字濾波器中,有限長單位沖激響應(finite impulse response,FIR)數字濾波由于性能穩定和線性相位的特點,能夠很好地應用于高頻噪聲的濾除[1-7]。目前,FIR濾波器的設計通常依賴MATLAB軟件,首先由MATLAB軟件根據濾波參數生成濾波器系數,然后在嵌入式系統中實現濾波運算[8-14]。該方式能夠在設計濾波器的同時,對濾波器的性能進行很好地分析和仿真,但對MATLAB軟件有著很強的依賴性,一旦采集的信號或者濾波要求發生改變時,需要重新生成濾波器系數,因此降低了現場應用的靈活性。現場可編程門陣列(field programmable gate array,FPGA)具有并行執行、運算速度快的特點,越來越多的FIR濾波器通過FPGA實現[15-20]。FPGA能夠在不影響其他模塊的情況下對數據進行濾波,大幅提高了濾波效率,但是存在濾波器階數固定、參數不易更新、靈活性較差的問題。

針對以上問題,本文提出了一種基于FIR濾波參數可調的電壓信號采集模塊設計方案。該方案采用高級精簡指令集微處理器(advanced RISC machine,ARM)+FPGA的硬件架構,由ARM完成消息處理、采樣配置、濾波器系數生成、數據管理等工作,FPGA完成模數(analog-digital,A/D)轉換控制、FIR數字濾波、數據緩存等工作。為提高FIR低通數字濾波器使用的靈活性和方便性,由ARM根據采樣頻率、截止頻率等濾波參數計算生成濾波器系數并發送給FPGA。FPGA在直接型FIR濾波器的基礎上,通過增加數據輸出的方式改進濾波器結構,實現濾波器階數的可調。利用FPGA并行執行的優勢,在不影響8個電壓輸入通道的信號采集速率的情況下,實現了對采集數據參數可調的FIR低通數字濾波。

1 系統總體方案設計

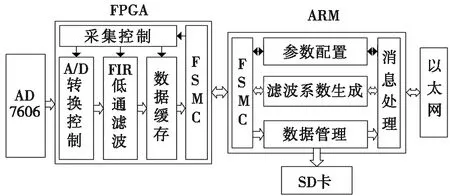

為了實現電壓信號采集和參數可調的FIR低通濾波,本文采用ARM+FPGA的架構。電壓采集模塊系統框圖如圖1所示。電壓采集模塊主要包括AD7606單元、FPGA單元、ARM單元、以太網單元和SD卡單元5個硬件單元,ARM和FPGA通過可變靜態存儲控制器(flexible static memory controller, FSMC)總線進行數據交互。

圖1 電壓采集模塊系統框圖

AD7606單元:采用最高采樣率為200 kHz的AD7606芯片作為模數轉換器,具有8個模擬量輸入通道,通過FPGA控制將±10 V/±5 V電壓的模擬信號轉換為數字信號。

FPGA單元:FPGA模塊采用Altera公司的EP4CE15F23C8N芯片,主要實現模數轉換控制、FIR低通濾波、數據緩存和采集管理等功能。

ARM單元:ARM模塊采用STM32F767IGT6芯片,主要負責通信消息處理、采集參數配置、濾波器系數生成和數據管理等工作。通過FSMC總線與FPGA進行通信,用于控制FPGA程序運行,進而實現對電壓信號采集參數配置及數據讀取。

以太網單元:實現采集模塊與上位機的通信,用于上位機對采集模塊的參數設置、數據讀取和采樣控制。

SD卡單元:將Micro SD卡作為數據存儲,將采集的電壓信號數據保存為數據文件。

工作流程:本模塊由上位機控制,采集模塊通過以太網單元接收上位機的命令消息,并從消息中提取采樣頻率、采樣通道、濾波器參數等配置參數。基于ARM的濾波器系數生成單元,根據FIR濾波器參數,計算得到濾波器系數,并發送給FPGA,由其根據濾波器系數及階數完成FIR數字低通濾波運算。FPGA根據ARM發送的配置參數運行程序,實現對電壓信號采集參數配置。ARM讀取FPGA中的采集數據,保存到SD卡或者通過以太網上傳至上位機。

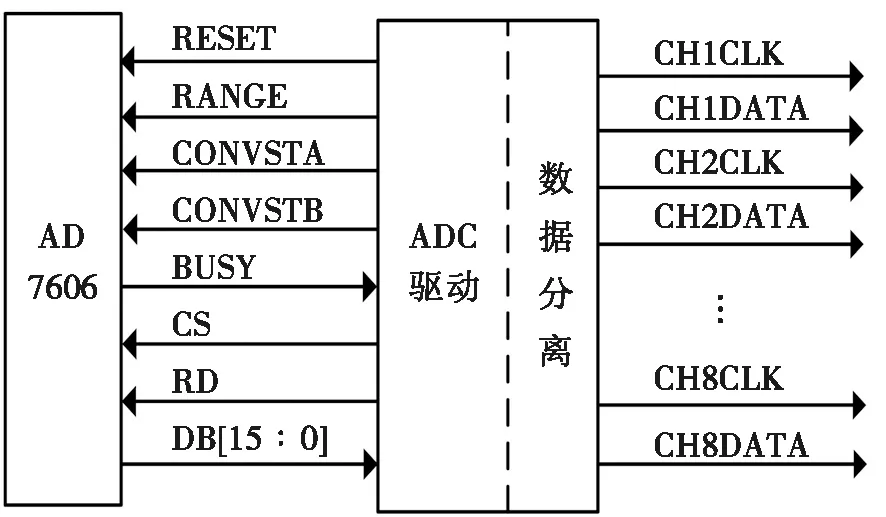

2 電壓信號的模數轉換

電壓信號的模數轉換由FPGA驅動AD7606實現,分為AD7606驅動和數據分離兩部分,如圖2所示。AD7606驅動部分根據芯片時序要求,控制AD7606進行模數轉換并完成數據的讀取,數據分離部分從AD7606輸出數據中分離出每個模擬通道的數據,便于對每個通道數據進行單獨的濾波和緩存。

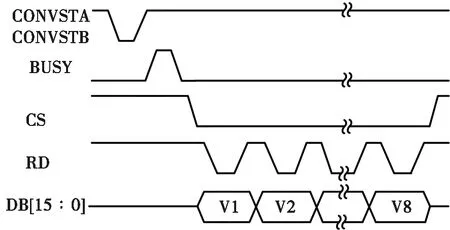

AD7606模式轉換和數據讀取時序如圖3所示。首先將CONVSTA和CONVSTB信號拉低后再拉高,開啟本次模數轉換,CONVSTA和CONVSTB拉高后開始監測BUSY信號線的平狀態,當監測到BUSY由高電平拉低時,表示本次模數轉換完成,開始進行數據的讀取。讀取數據時,首先拉低CS信號,然后將RD信號先拉低后拉高,在RD信號的上升沿鎖存數據線DB[15∶0]上的數據,對RD信號按照以上步驟操作8次,將通道1到通道8的數據依次讀出,讀取結束后拉高CS信號。

圖2 模數轉換模塊結構圖

圖3 AD7606模式轉換及數據讀取時序圖

從AD7606讀取的數據是以通道為單位的串行數據,為了對每個通道的數據進行單獨的數字濾波,需要將數據轉換為以通道為單位的并行數據。數據分離部分收到數據后,按照通道1到通道8的順序,將數據及數據輸出時鐘信號分配到對應的輸出口,便于后續各個通道數據的濾波處理。

3 參數可調FIR濾波器

參數可調FIR低通濾波器的實現由ARM和FPGA兩部分協同完成,ARM根據窗函數、濾波器階數、采樣頻率、截止頻率等濾波器參數計算生成濾波器系數,并通過FSMC總線將濾波器系數和階數發送給FPGA。FPGA將采集數據與濾波器系數進行對應階數的濾波運算,實現對電壓采集數據參數可調的FIR低通濾波。

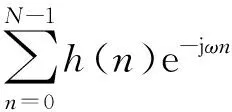

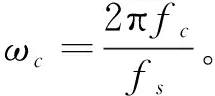

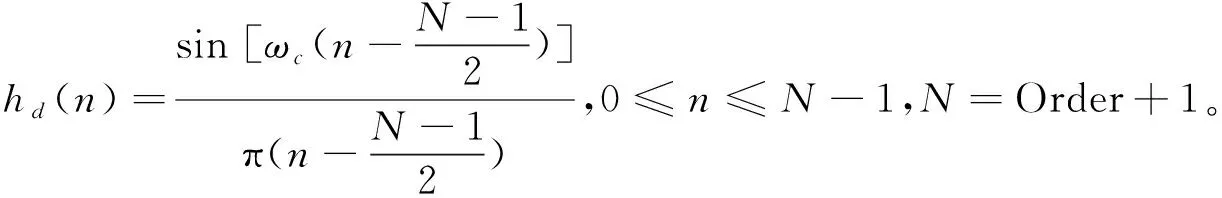

3.1 濾波器系數生成

針對窗函數法設計FIR濾波器時的浮點數運算問題,ARM芯片采用STM32F767IGT6,該芯片內部集成的浮點數運算單元對單精度浮點數和雙精度浮點數的運算都具有良好的支持性,能夠很好地用于濾波器設計時的浮點數運算。FIR濾波器系數計算步驟如下:

(Ⅳ)將濾波器階數Order代入所選擇的窗函數ω(n)中,計算得到窗函數序列。

(Ⅴ)將hd(n)與選擇的窗函數ω(n)相乘,得到單位脈沖響應h(n)=ω(n)hd(n)。

由于計算得到的濾波器系數為浮點數,FPGA直接對這些系數運算會耗費大量的邏輯單元,將影響濾波運算的效率,因此需要對系數進行量化。系數量化時,首先對所有濾波器系數乘以(215-1),將處理后的系數取整數,然后將整數濾波器系數轉換成二進制補碼數據。ARM在完成對濾波器系數的計算和量化后,通過FSMC總線將濾波器系數和階數發送給FPGA,由FPGA完成FIR低通濾波運算。

3.2 階數可調的濾波器結構

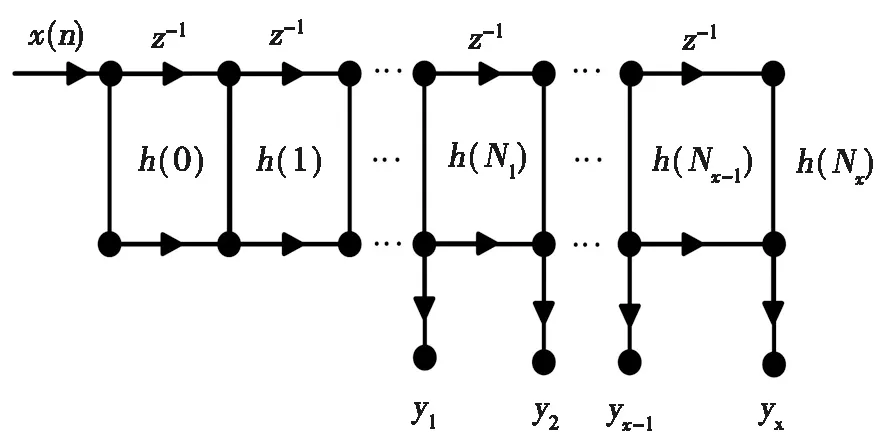

為了實現FIR濾波器階數可調,本文在直接型FIR濾波器的基礎上,設計了一種多輸出口的濾波器結構。FIR直接型濾波器結構系統函數[21]如式(1)所示。

(1)

由式(1)可知:直接型FIR濾波器能夠通過數據延遲、乘法、加法運算實現。在FPGA中采用這種結構進行設計,不僅能夠實現快速濾波運算,還能夠使濾波模塊與模數轉換模塊數據輸出保持時鐘同步。這種同步能夠保證數據在采樣、濾波和緩存之間的流水線傳輸,數字濾波不會影響采集速度和數據緩存,在長時間采樣時具有很大的優勢。

通過對直接型結構的傳遞函數進行變換,可以將式(1)所示傳遞函數分為兩部分,得到等價傳遞函數:

(2)

由式(2)可知:對于直接型結構的FIR濾波器,在低階濾波器后加入延遲單元、乘法單元和加法單元得到高階濾波器;低階濾波器可通過去除掉高階濾波器的部分延遲單元、乘法單元和加法單元的方式獲得。同理,還可以在此基礎上繼續對濾波器進行拆分,從而在一個高階濾波器中獲得若干個低階濾波器。根據此原理,本文在直接型FIR濾波器的基礎上,通過對濾波器拆分組合的方式,設計了一種多數據輸出口的網絡結構,如圖4所示。

由圖4可知:在不同的數據輸出點上數據參與的延遲、乘法、加法運算是不同的,在傳遞函數H(z)上體現為N值不同,因此每個數據輸出點對應不同階數的濾波運算,可通過選擇數據輸出點的方式選擇濾波器階數,從而實現濾波器階數的可調。

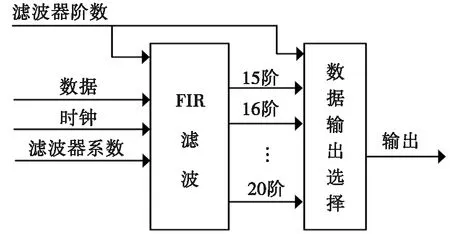

本文設計的FIR濾波器模塊具有6個數據輸出口,分別對應15~20共6種階數的濾波。FIR濾波模塊框圖如圖5所示。在濾波器參數改變時,ARM將濾波器階數和濾波器系數通過FSMC總線發送給FPGA,FPGA更新濾波器系數寄存器,并進行濾波運算。在FIR濾波運算后,根據濾波器階數選擇對應的數據輸出口輸出數據。

圖4 多數據輸出口FIR濾波器結構圖

圖5 FIR濾波模塊框圖

4 數據的緩存與讀取

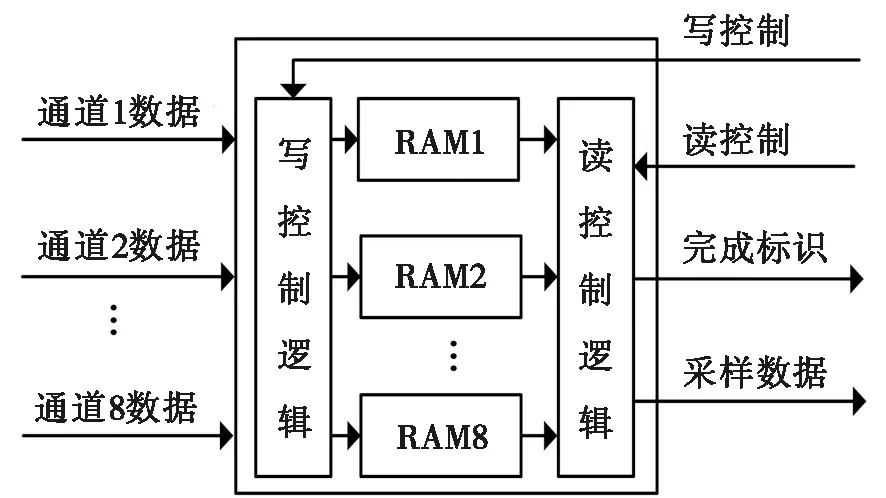

電壓采集模塊共有8個電壓信號輸入通道,為了能夠對每個通道的數據進行緩存,在FPGA內部建立了8個深度為1 024、寬度為32的隨機存取存儲器(radom access memory,RAM),編號為RAM1~RAM8,分別對應通道1到通道8的數據存儲,如圖6所示,圖6中輸入數據為濾波后數據。

圖6 數據濾波和緩沖結構圖

在電壓信號采集過程中,模數轉換和FIR濾波模塊一直運行,通過控制數據緩存單元數據的寫入與讀取,控制電壓信號采集。采集開始后,數據開始寫入緩存區,由于FSMC總線的通信速度遠大于AD7606的采集速度,可在不影響數據采集的情況下完成數據的讀取。采集結束后,數據停止寫入緩存區,ARM停止讀取數據。讀取數據時,ARM通過FSMC總線對數據進行讀取,讀取時根據指定的通道,讀邏輯控制單元切換RAM數據輸出接口,輸出對應RAM中的數據。ARM在讀取到數據后,根據設置的參數選擇將數據以文件的形式保存至SD卡或者直接上傳至上位機。

5 實驗與分析

為了對本方案進行驗證,分別從電壓采集精度和FIR濾波效果兩個方面進行測試。

5.1 電壓采集精度測試實驗

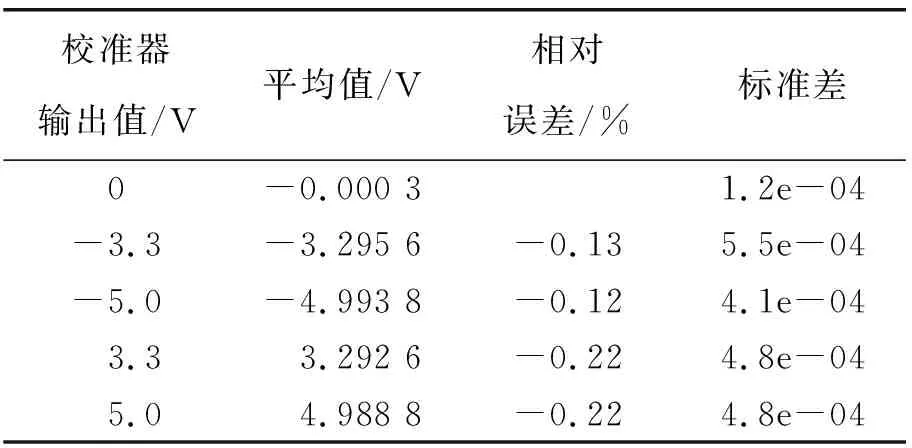

電壓采集精度測試主要通過采集福祿克5502A校準器輸出的電壓信號,并將采集值與輸出值進行對比,從而獲得電壓采集模塊的采集精度。

采用福祿克5502A校準器,輸出0~5 V多種幅值的直流信號,然后對電壓信號進行采集,采集數據量為1 000,實驗測量結果如表1所示。

由表1可知:采集模塊采集的相對誤差絕對值最大為0.22%,并且每組1 000點采集數據標準差值很小,采集模塊具有很高的電壓采集精度。

表1 電壓采集精度測量表

5.2 FIR濾波測試實驗

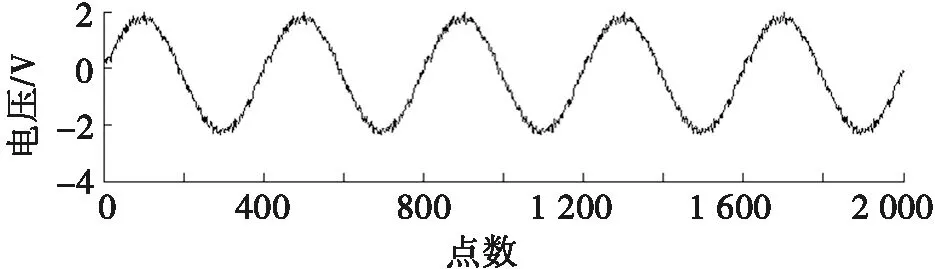

FIR濾波測試實驗將峰峰值為5 V、頻率為250 Hz正弦波信號作為采集對象,并在信號中疊加20 dB信噪比的白色高斯噪聲,作為濾波器濾除目標。電壓采集模塊以100 kHz的頻率采集信號,并采用不同參數的濾波器對信號濾波,通過分析濾波后的數據波形判斷濾波器的濾波效果。

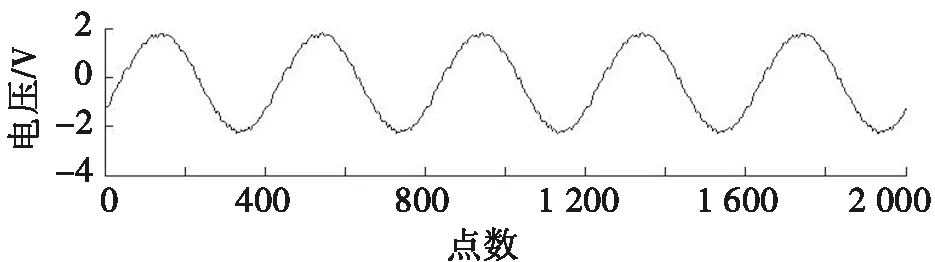

電壓采集模塊在未加濾波模式下,采集的原始信號如圖7a所示。由圖7a可以看出:采集的正弦波數據中存在著大量的噪聲信號聲。

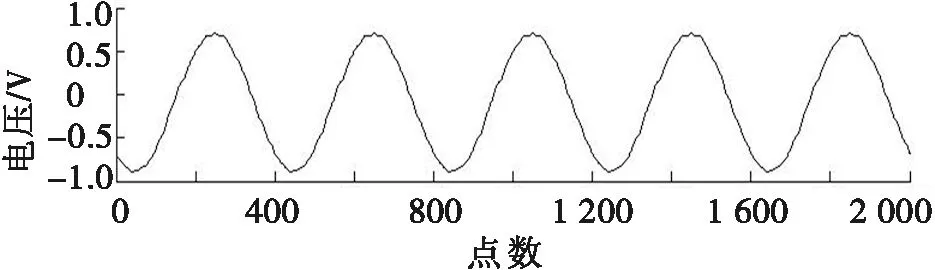

為了對本文設計的濾波器濾波功能進行驗證,以100 kHz采樣頻率,采用漢明窗作為窗函數,分別采用20階10 kHz截止頻率、20階2 kHz截止頻率和15階2 kHz截止頻率,對疊加了噪聲的原始信號進行FIR低通濾波,濾波后的數據波形如圖7b~圖7d所示。

(a) 原始信號

(b) 20階10 kHz截止頻率濾波效果圖

(c) 20階2 kHz截止頻率濾波效果圖

由圖7b~圖7d可知:濾波器的截止頻率越低,信號的濾波效果越好,但是對有效信號的衰減也較大,在同一截止頻率下,高階數濾波相對于低階數具有更好的濾波效果。因此,本電壓采集模塊的FIR數字低通濾波器根據設置參數對濾波器進行調整,并濾除信號中的高頻噪聲。

6 結論

本文提出了一種FIR濾波參數可調的電壓采集模塊,該模塊采用ARM+FPGA的硬件架構,能夠在實現電壓采集的同時,完成參數可以調整的FIR低通濾波運算。本采集模塊能夠完成電壓采集功能,采集相對誤差絕對值最大為0.22%,具有較高的電壓采集精度。設置濾波參數可以完成FIR低通濾波器系數生成和濾波器結構調整,濾除電壓信號中的高頻干擾噪聲。