高性能CMOS鑒頻鑒相器和電荷泵的設計

蘇 浩 ,郭 京 ,牟仕浩 ,羅云霞 ,華爾天 ,閆樹斌 ,3

(1.中北大學儀器與電子學院,山西 太原 030051;2.浙江水利水電學院電氣工程學院,浙江 杭州 310018;3.中北大學電氣與控制工程學院,山西 太原 030051)

CMOS技術具有低功耗和高集成度的特點,它最初是為數字電路應用而設計的。隨著近幾年來半導體技術的不斷發展,集成電路制造工藝不斷優化,CMOS技術也被廣泛應用在模擬電路中。現在,CMOS技術已經成為設計低成本、低功耗和高集成度的模擬前端(WIFI、藍牙、GPS、ZigBee和RFID)主流的選擇。

鎖相環電路是由模擬電路和數字電路組成的。在最近幾代通信系統中,鎖相環已經成為實現頻率合成器的標準方法。鎖相環本身的設計也是極具挑戰性的。

電荷泵鎖相環由于其具有捕捉時間短、捕捉范圍寬、線性度好和穩態相位差幾乎為零的優點,被廣泛運用在各類頻率合成器的設計中。

文中主要設計了一款應用在鎖相環系統中的鑒頻鑒相器和電荷泵的CMOS電路。

1 PFD/CP相位誤差分析

鎖相環電路[1]主要包括鑒頻鑒相器(Phase-Frequency Detector,PFD)、電荷泵(Charge Pump,CP)、環路濾波器(Loop Filter,LF)、壓控振蕩器(Voltage Control Oscillator,VCO)和分頻器(Frequency Divider,FD),文中參考信號頻率設定為10 MHz。

PFD/CP電路采用TSMC 0.18 μm工藝庫中晶體管和其他無源元件進行設計。晶體管和其他無源元件的非理想因素會給電路帶來諸如電流泄漏、電荷共享和電流失配等一系列問題,從而會引起鎖相環電路周期性的抖動,在VCO輸出端形成噪聲[2]。

一旦鎖相環鎖定,電荷泵在大部分時間里是不工作的。只有在復位過程中形成正負脈沖電流的那一小段時間內,它才被激活工作。該電流不會改變VCO的控制電壓,但是可能會引起鎖相環抖動。這些小的脈沖電流形成了輸出信號噪聲[3]。

產生這類噪聲的主要原因可以總結為下面幾點:泄漏電流、電荷泵充放電電流的差異、鎖定狀態下電荷泵充電脈沖和放電脈沖的不匹配。

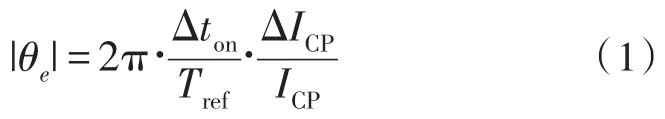

PFD的導通時間和延時失配是由PFD的結構決定的,而電流失配和電荷泵電流大小是由電荷泵的結構決定的。失配電流主要是由于PMOS(P型MOS管)晶體管和NMOS晶體管之間的不匹配性能造成的,同時晶體管的一些工藝參數的不同也會導致電荷泵失配電流大小的不同,式(1)表示受電流失配影響而產生的相位誤差|θe|大小:

式中,Δton表示鑒頻鑒相器的開通時間,ΔICP表示失配電流的大小,Tref表示參考時鐘周期大小。

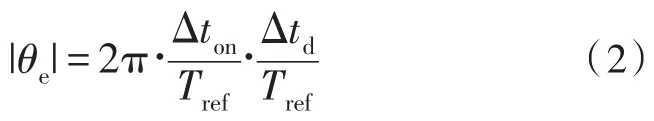

由于PFD出來的兩路信號(UP和DOWN信號)到達電荷泵時會存在一定的時間延遲誤差Δtd,這種延遲誤差帶來的相位偏差可以表示為:

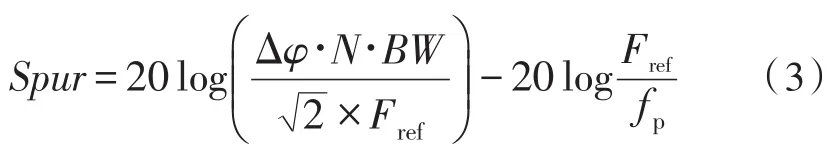

根據Maxim[4],參考雜散可以用式(3)計算:

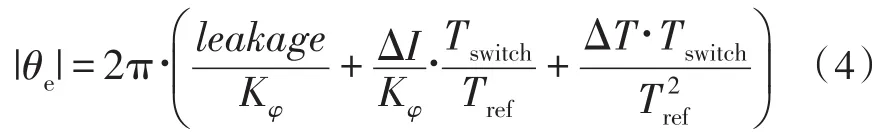

其中,Δφ表示由上述3個因素引起的相位誤差,BW代表鎖相環的帶寬(Hz),N是分頻數,fp是三階環路濾波器引入的另一個極點。相位誤差|θe|可以用式(4)估計:

其中,Tref表示輸入參考信號的周期,Tswitch表示電荷泵鎖定狀態下開關閉合的時間,ΔI表示鎖定狀態下電荷泵失配電流的大小,ΔT表示鎖定狀態下電荷泵失配電流的時間差。

因此,為了降低相位誤差,設計了一個帶有延時模塊,且輸出四路控制信號的PFD,以及一個低失配電流大小可調的電荷泵電路。

2 鑒頻鑒相器的設計

鑒頻鑒相器主要根據兩路輸入信號的相位和頻率差生成正比于這個差值的輸出信號。鑒頻鑒相器其中一路輸入信號是由石英晶體生成的恒定信號,另一路輸入信號是來自于通過分頻器后的輸出信號[5]。鑒頻鑒相器的功能是通過調整VCO控制信號從而修正振蕩器信號和石英晶體參考信號的頻率和相位差。

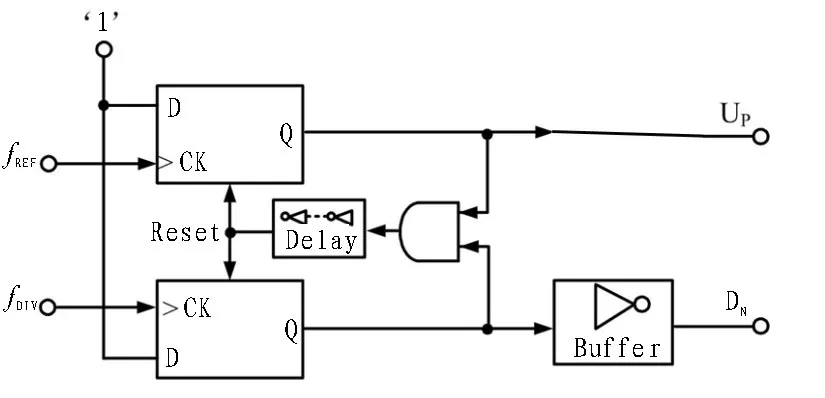

鑒頻鑒相器由兩個D觸發器和一個與門構成。初始狀態下,鑒頻鑒相器的兩路輸出信號(UP和DOWN)都為低電平,當任意一個輸入信號的上升沿到達時,D觸發器會將輸入信號(通常連接至高電平)輸出,而另一個D觸發器將繼續維持低電平輸出。當第二個信號上升沿到來時,它也將輸出高電平。這時,兩個D觸發器的輸出信號均為高電平,通過與門后,該高電平信號使兩個D觸發器復位。文中設計的D觸發器采用TSPC(True Single-Phase Clock,真單相時鐘)邏輯,TSPC結構相比于傳統主從D觸發器,具有電路結構簡單,工作速度快,功耗較低的優點,是目前最流行的PFD結構。觸發器的D輸入端都接邏輯“1”,因此上升沿時觸發器輸出高電平,這樣可以采用與門實現復位信號。D觸發器中RESET是高電平復位端,CLK為信號輸入端,Q為觸發器輸出端。但PFD存在死區(dead zone)的問題。當兩路輸入信號相位差過小時,由于結電容的存在,信號會存在一定的上升和下降時間,在這部分時間里,由于脈沖電平沒有到達足夠開啟MOS管的電平要求,導致電荷泵無法正常工作,也就無法通過改變壓控振蕩器的控制電壓使得輸入信號穩定。死區效應的存在使得壓控振蕩器必須等到隨機相位誤差積累到一定程度之后才能使環路反饋正常,這會導致抖動現象的存在。在-φ0~φ0這一死區的相位區間里,由于電荷泵無法正常工作,因此輸出電流幾乎為0,這一區域被稱為死區。

死區問題將導致環路輸出信號抖動的上升,并惡化鎖相環系統的相位噪聲。解決死區的方法之一是在復位支路上引入偶數個反相器增加延時,從而脈沖有足夠時間到達高電平,解決了死區問題。

為了配合電荷泵的設計,需要四路反向對稱的信號:UP,UPN,DN,DNN。由于電荷泵同時需要充電和放電支路,電荷泵的UP支路必須采用PMOS管實現,因此,UP支路也需要引入反相器從而使電荷泵可以正常工作。為了防止DOWN信號相比于UP信號產生延時,DOWN支路增加了傳輸門(TG)電路,這樣可以確保UP和DOWN信號沒有相位延遲。PFD總體設計如圖1所示。

圖1 PFD鑒頻鑒相器原理圖

3 電荷泵的設計

電荷泵的主要功能是將PFD輸出的相位信息(時間信號)轉變為電流信號(模擬信號),該電流信號經過環路濾波器之后會產生控制調節壓控振蕩器的電壓信號Vctrl。

圖2(a)所示是一個傳統的鑒相器和電荷泵電路的原理圖,鑒相器輸出信號UP和DN控制電荷泵電路中MOS管的啟閉,如果UP和DN均為低電平,那么兩個NMOS管均未導通,由于儲能電容Cp的存在,Vout保持不變;如果UP為高電平,DN為低電平,那么S1管導通,I1對 CP充電,Vout增大;如果 DN為高電平,UP為低電平,那么 S2管導通,CP通過 I2放電,Vout減小[6-8]。如圖 2(b)所示,信號A頻率大于信號B,則UP產生連續的高電平,推動Vout增大,通過環路反饋使得信號B頻率下降,最終兩輸入信號相位差降為0,環路穩定[9-10]。

圖2 電荷泵與PFD

電荷泵的設計對回路輸出信號的參考雜散有重要影響。鎖相環的電荷泵泄漏和不匹配都會產生參考雜散[11]。

當電路已經存在一個基準電流i1時,可以利用電流鏡結構獲得多個相同或者成比例的鏡像電流i0。

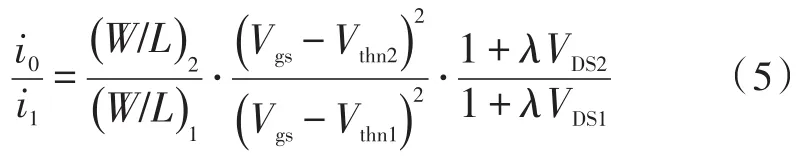

當VDS1=VGS1時,晶體管M1處在飽和區,當晶體管M2滿足 VDS2>VGS2-Vthn2且 VGS2>Vthn2,根據 MOS 管飽和區的公式,可以得出io與i1的電流關系:

當采取相同的集成電路工藝且在同一批次的集成電路流片時,有Vthn1=Vthn2,所以式(5)可簡化為:

從式(6)可以看出,要保證i0=ki1,其中k=1,2…,必須要盡量減小溝道長度調制效應的影響。又根據ron=1/(λID)可知,當λ減小時,輸出端電阻增大,從而可以減少由于電壓波動引起的電流波動。為了提高電流鏡輸出鏡像電流的準確性,需要抑制溝道長度效應調制的影響[12],盡量避免使用工藝提供的最小尺寸的晶體管可以有效抑制此影響。

由于NMOS晶體管電子移動速度比PMOS管更快,因此M2管的W/L(寬長比)需要比M12管的更大,這是為了減少上支路的溝道電阻。除此之外,由于各個晶體管尺寸的不同,寄生電容的大小也有區別。晶體管的工作速度會隨著寄生電容CH的增大而減小。當設計人員想通過提高晶體管的寬長比來提高工作速度時,寄生電容也會同時增大,而寄生電容增大會使晶體管工作速度減緩。在一定程度上,一味地增加晶體管的寬長比并不一定會加快晶體管的工作速度。因此,設計人員需要合理地設置晶體管的寬長比。

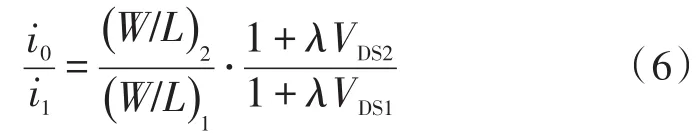

圖3所示是文中采用的電荷泵電路,該結構相比于帶有運放的電荷泵而言具有易于集成的優點。和傳統的電荷泵電路不同,設計中充當開關的是晶體管M1和M8,這樣可以減輕電荷注入誤差和時鐘饋通效應,從而降低壓控振蕩器控制電壓的抖動和鎖相環系統的參考雜散[13-14]。晶體管 M1、M2、M8、M12分別和M4、M5、M9、M11配合,可以精確地映射電流源 I6的電流(50 μA)。

圖3 電荷泵CMOS原理圖

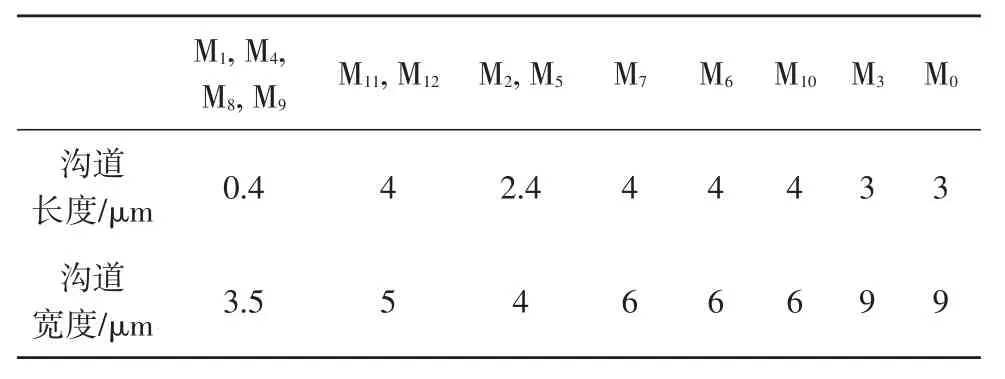

電荷泵電路中各個晶體管的溝道長、寬數據如表1所示。

表1 電荷泵中晶體管的溝道長度、寬度

4 仿真結果分析

4.1 鑒頻鑒相器仿真分析

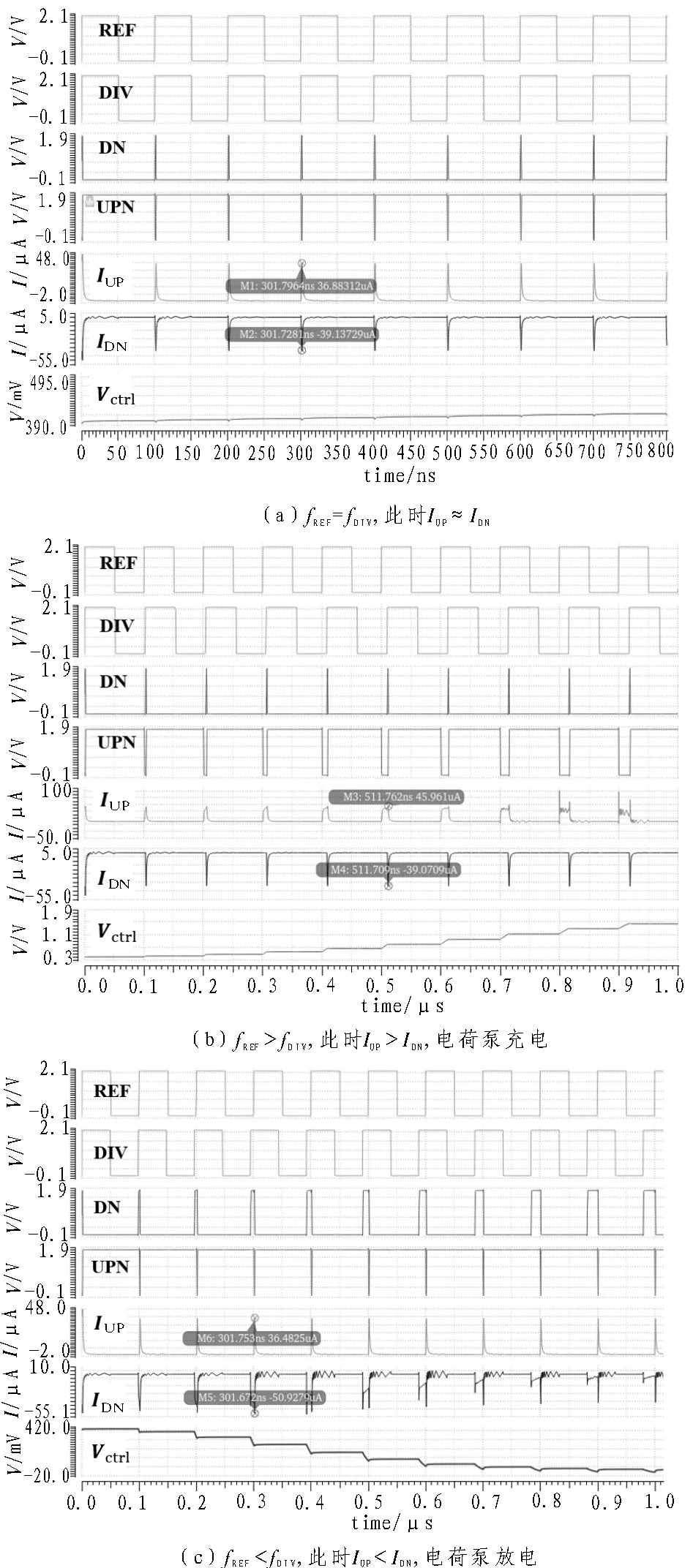

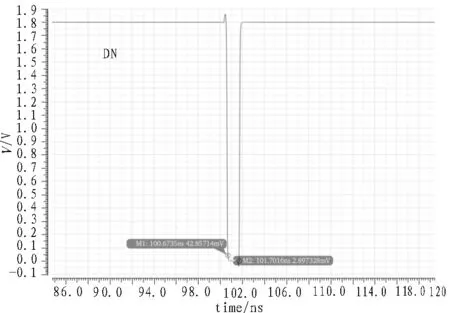

瞬態仿真采用TSMC(Taiwan Semiconductor Manufacturing Company)0.18 μm工藝庫,是由Cadence提供的Spectre simulator得到的。圖4所示是PFD仿真波形圖,圖 4(a)(b)(c)對應的分別是當參考頻率等于、大于和小于分頻器輸出頻率時,對應的UPN和DN輸出波形。仿真波形表明,PFD具有良好的鑒頻功能。當相位差為0,延時模塊為4個延時單位時,鑒頻鑒相器的導通時間仿真如圖5所示。由仿真結果可知,鑒頻鑒相器的4個延時單位的導通時間約為1 ns,因此每個延時單位控制的導通時間約為0.25 ns。

圖4 電荷泵輸出電流圖

4.2 電荷泵仿真分析

當環路鎖定時,理想的電荷泵輸出的充放電電流應該是相等的[15],此后通過環路濾波器產生調節VCO的控制電壓。圖4(a)是在參考頻率和分頻器輸出頻率同頻同相時的波形圖,此時IUP=36.9 μA,IDW=39.1 μA,充放電電流最大差距僅為2.2 μA,這意味著兩者最大失配百分比小于6%。為了測得電荷泵電流失配對鎖相環的影響,在仿真過程中測量了環路濾波器的輸出電壓值,見圖4中信號Vctrl。

圖5 鑒頻鑒相器延時模塊仿真圖

圖6 PFD/CP相位噪聲測試結果

當 fREF=fDIV時,電荷泵充放電電流同時開啟,由于存在少量電流失配,Vctrl出現波動,但輸出穩定后是一個常量,此時振蕩器輸出信號穩定,鎖相環環路鎖定;當 fREF=fDIV時,Vctrl上升,控制振蕩器輸出頻率上升,直到 fREF=fDIV;當 fREF=fDIV時,Vctrl逐步下降,控制振蕩器輸出頻率下降,直到 fREF=fDIV。

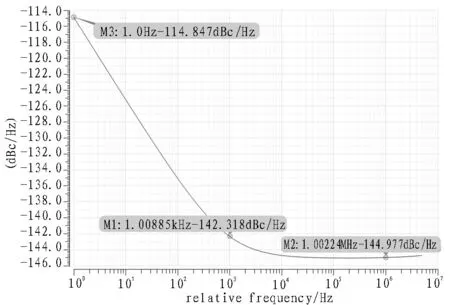

4.3 相位噪聲

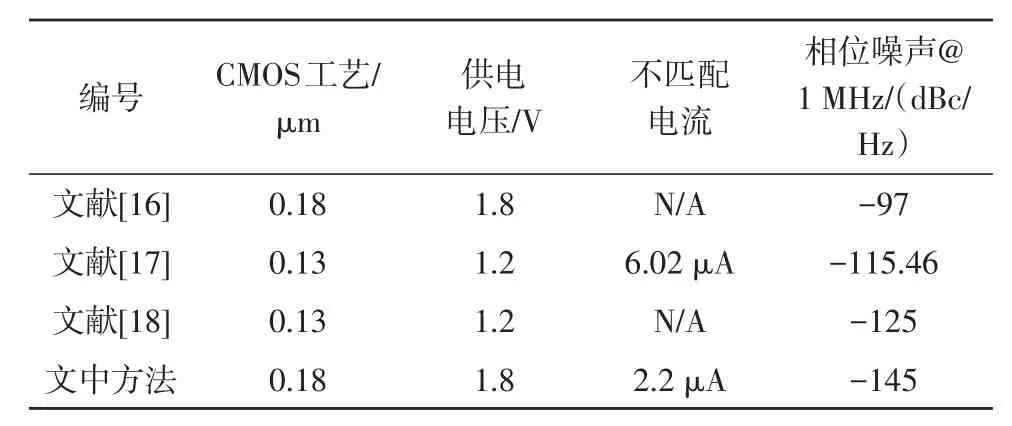

通過Spectre RF仿真工具(PSS和Pnoise仿真)得到鑒頻鑒相器和電荷泵總體的輸出相位噪聲圖。如圖6所示,輸出信號相位噪聲在1 Hz處大小為-114.8 dBc/Hz@1 Hz,在1 MHz處大小約為-145 dBc/Hz@1MHz,電荷泵的泄漏電流和電荷注入誤差得到了有效抑制,輸出信號相位噪聲較小。表2列出了幾種電荷泵結構的參數表現對比。

表2 幾種CMOS CP的性能表現對比

5 結 論

采用TSMC 0.18 μm CMOS工藝,設計并實現了一款應用在芯片級銣原子鐘3.4 GHz激勵源中的鑒頻鑒相器和電荷泵電路。鑒頻鑒相器由兩個邊沿觸發、帶復位的D觸發器和一個與門組成。為了消除死區,在鑒頻鑒相器復位支路加入了延時單位。電荷泵采用電流鏡結構設計,有效抑制了電流失配,進一步降低了輸出信號的噪聲。測試結果表明,在電源為1.8 V,電荷泵電流為50 μA時,充放電電流失配最大僅為2.2 μA,輸出噪聲為-145 dBc/Hz@1 MHz。