圖像卷積實(shí)時(shí)計(jì)算的FPGA實(shí)現(xiàn)

張帆

(中國科學(xué)院長春光機(jī)所,吉林 長春 130033)

卷積運(yùn)算普遍應(yīng)用在圖像模糊、圖像銳化以及卷積神經(jīng)網(wǎng)絡(luò)、目標(biāo)識(shí)別等數(shù)字圖像處理中,是圖像預(yù)處理的關(guān)鍵步驟。根據(jù)卷積計(jì)算操作單一化、算法簡便的特點(diǎn),結(jié)合FPGA資源循環(huán)復(fù)用和并行處理結(jié)構(gòu),實(shí)現(xiàn)了基于FPGA的圖像卷積計(jì)算[1-4]。但是圖像卷積計(jì)算要求遍歷圖像所有像素點(diǎn),圖像像素越多,計(jì)算時(shí)間越長;同時(shí)在圖像處理中涉及多級(jí)聯(lián)卷積計(jì)算,例如卷積神經(jīng)網(wǎng)絡(luò)計(jì)算時(shí),其并行性差,導(dǎo)致圖像處理實(shí)時(shí)性很難得到保證,因此對(duì)基于FPGA的圖像卷積計(jì)算方式的研究顯得尤為重要[5-6]。

目前對(duì)于提升FPGA圖像處理中卷積計(jì)算時(shí)間的研究主要分為硬件和軟件兩個(gè)方面。其中基于硬件電路的設(shè)計(jì)方法簡單,根據(jù)圖像卷積處理目的設(shè)計(jì)出特定的電路結(jié)構(gòu),以滿足圖像處理需求[7-8]。這種方法能夠有效地實(shí)現(xiàn)卷積計(jì)算,但是不具有通用性,實(shí)用價(jià)值不高。所以基于FPGA算法處理圖像數(shù)據(jù)的方法更具有研究意義。結(jié)合FPGA的高速處理能力和并行計(jì)算特點(diǎn),設(shè)計(jì)算法框架以實(shí)現(xiàn)降低資源消耗,提升圖像處理速率的目的[9-10]。文獻(xiàn)中提出多種方法,包括基于FPGA設(shè)計(jì)一種卷積計(jì)算IP核,通過對(duì)IP核參數(shù)設(shè)置,實(shí)現(xiàn)對(duì)不同窗口大小、不同系數(shù)的卷積計(jì)算[11]。利用FPGA的并行機(jī)制以及分布式,用查找表代替乘法器,降低圖像運(yùn)算量[12]。采用異步接收發(fā)送以及流水線結(jié)構(gòu),實(shí)現(xiàn)圖像數(shù)據(jù)準(zhǔn)確傳輸及計(jì)算[13-16]。文獻(xiàn)中提出的基于FPGA卷積計(jì)算是根據(jù)系統(tǒng)獲取圖像數(shù)據(jù)后,通過不同的卷積計(jì)算方法減少圖像處理時(shí)間,提高圖像處理效率。在此基礎(chǔ)上設(shè)計(jì)一種實(shí)時(shí)圖像卷積計(jì)算方法,實(shí)現(xiàn)在圖像數(shù)據(jù)采集過程中完成圖像預(yù)處理卷積計(jì)算功能,提高圖像處理速率;同時(shí)針對(duì)多級(jí)聯(lián)卷積計(jì)算,圖像輸出計(jì)算結(jié)果實(shí)時(shí)性不受卷積次數(shù)影響,圖像輸入輸出同步化。

基于FPGA實(shí)現(xiàn)多級(jí)聯(lián)卷積計(jì)算步驟主要包括:首先,應(yīng)用乒乓FIFO的方式對(duì)輸入的數(shù)字圖像數(shù)據(jù)進(jìn)行異步緩存及同步操作;然后,輸入到循環(huán)復(fù)用的RAM存儲(chǔ)器中,對(duì)數(shù)據(jù)進(jìn)行逐行卷積計(jì)算并將結(jié)果直接輸出到下一級(jí)卷積計(jì)算模塊。整個(gè)計(jì)算過程中,數(shù)據(jù)并行處理及傳輸,系統(tǒng)不需要存儲(chǔ)整幅圖像數(shù)據(jù),節(jié)省了FPGA的存儲(chǔ)空間。通過比較MATLAB圖像處理結(jié)果和ISIM仿真結(jié)果,驗(yàn)證了該方法的可行性以及正確性。同時(shí)搭建了硬件操作系統(tǒng),對(duì)相機(jī)獲取的圖像進(jìn)行卷積圖像操作,實(shí)現(xiàn)圖像處理的并行性以及實(shí)時(shí)性的驗(yàn)證。

1 FPGA多級(jí)聯(lián)圖像卷積計(jì)算

數(shù)字圖像卷積計(jì)算廣泛應(yīng)用于圖像平滑、圖像銳化、形態(tài)學(xué)處理、模板匹配、卷積神經(jīng)網(wǎng)絡(luò)、目標(biāo)識(shí)別等。根據(jù)實(shí)際要求,選擇不同卷積核,將輸入圖像處理成期望結(jié)果。常見的卷積操作包括圖像平滑中選用均值濾波、高斯濾波等方法實(shí)現(xiàn)噪聲濾除;圖像銳化中邊緣提取的Roberts算子、Sobel算子、Prewitt算子、Laplacian算子以及Canny算子等,卷積神經(jīng)網(wǎng)絡(luò)中獲取圖像特征的卷積計(jì)算。

卷積核是卷積運(yùn)算的核心,形式多為二維矩陣,矩陣中各位置權(quán)重不同,對(duì)圖像的處理結(jié)果也存在差異。對(duì)于輸入的數(shù)字圖像F,寬度和高度分別為w、h,卷積核H的維度參數(shù)為wH、hH,卷積核的長度和寬度多為奇數(shù)。其中wH、hH<=w、h。卷積計(jì)算示意圖如圖1所示。

圖1 卷積核內(nèi)部計(jì)算示意圖

將卷積核中心像素點(diǎn)與數(shù)字圖像中待計(jì)算的像素點(diǎn)重合,圖像F中鄰域區(qū)間與卷積核中數(shù)據(jù)一一對(duì)應(yīng),根據(jù)公式(1)計(jì)算中心像素點(diǎn)對(duì)應(yīng)在輸出圖像G中像素點(diǎn)的灰度值。應(yīng)用卷積核遍歷整幅圖像,獲取相應(yīng)操作的輸出圖像。

可以看出圖像的卷積計(jì)算方法簡單,可重復(fù)性強(qiáng),但是計(jì)算數(shù)據(jù)量大。對(duì)于圖像需要多次卷積計(jì)算的處理時(shí)間更長。對(duì)此,文中結(jié)合FPGA并行性,提出了高效實(shí)時(shí)計(jì)算圖像多級(jí)聯(lián)卷積計(jì)算的方法。

1.1 基于FPGA的圖像卷積計(jì)算設(shè)計(jì)

基于FPGA的圖像卷積計(jì)算主要是通過循環(huán)利用RAM存儲(chǔ)器實(shí)現(xiàn)的。由于圖像的卷積計(jì)算算法簡單,每個(gè)像素點(diǎn)操作方法相同,依據(jù)FPGA硬件的并行算法能夠有效實(shí)現(xiàn)數(shù)值的實(shí)時(shí)運(yùn)算。

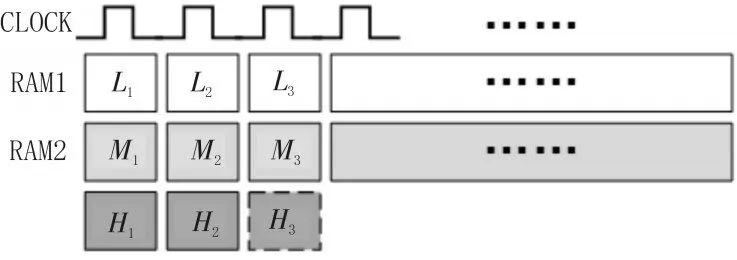

圖像數(shù)據(jù)按照FPGA內(nèi)部數(shù)字時(shí)鐘逐行順序輸入。FPGA內(nèi)部設(shè)定(2hH-2)個(gè)RAM存儲(chǔ)器,其中hH表示卷積核的高度。每個(gè)RAM存儲(chǔ)器位長為M bit,位深為w,M等于圖像數(shù)據(jù)的位長,位深w即為圖像每行的數(shù)據(jù)量。下面以3×3的卷積核為例,詳細(xì)介紹圖像卷積計(jì)算的實(shí)現(xiàn)。

當(dāng)卷積核是3×3大小時(shí),F(xiàn)PGA預(yù)先設(shè)定4個(gè)RAM 存儲(chǔ)器,其中 RAM1、RAM2為一組,RAM3、RAM4為另一組,實(shí)現(xiàn)相鄰兩行圖像數(shù)據(jù)的緩存。如圖1所示,RAM1、RAM2中分別存儲(chǔ)前兩行數(shù)據(jù),當(dāng)?shù)谌袛?shù)據(jù)按順序依次輸入時(shí),根據(jù)數(shù)字輸入時(shí)鐘節(jié)拍讀取RAM1、RAM2同一列數(shù)據(jù),先后得到L1、M1、H1以及 L2、M2、H2;FPGA新讀入第三列數(shù)據(jù)時(shí),獲取 L3、M3、H3數(shù)據(jù),原圖像中以 M2為中心點(diǎn)的八鄰域數(shù)據(jù)全部獲得。將該鄰域數(shù)據(jù)與卷積核進(jìn)行相應(yīng)計(jì)算,結(jié)果作為卷積處理后圖像M2位置處的像素值輸出。

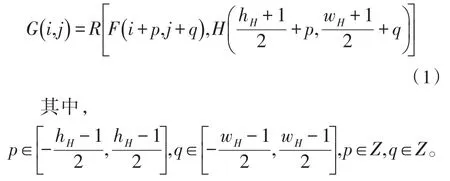

對(duì)整幅圖像進(jìn)行操作時(shí),循環(huán)使用RAM1、RAM2和RAM3、RAM4對(duì)數(shù)據(jù)進(jìn)行緩存,其過程如圖2所示。首先將圖像前兩行數(shù)據(jù)F(1,:)、F(2,:)依次存入RAM1、RAM2中;在第三行數(shù)據(jù) F(3,:)輸入過程中,求出卷積處理后圖像的第二行數(shù)據(jù)G(2,:)并輸出,同時(shí)將RAM2中數(shù)據(jù)和新輸入的行數(shù)據(jù)(即F(2,:)和 F(3,:))存入 RAM3、RAM4中。當(dāng)?shù)谒男袛?shù)據(jù) F(4,:)輸入時(shí),依照上述方法,結(jié)合RAM3、RAM4存儲(chǔ)器中數(shù)據(jù)和新輸入的數(shù)據(jù)計(jì)算圖像G(3,:)對(duì)應(yīng)的輸出結(jié)果,同時(shí)將RAM4中數(shù)據(jù)和第四行數(shù)據(jù)(即F(3,:)和 F(4,:))存入 RAM1、RAM2中。以此類推,在行數(shù)據(jù)輸入過程中,完成該行的卷積計(jì)算以及下一行卷積計(jì)算數(shù)據(jù)的預(yù)存儲(chǔ)。循環(huán)利用RAM1、RAM2和RAM3、RAM4組合,交替存儲(chǔ)數(shù)據(jù),逐行計(jì)算圖像卷積結(jié)果,當(dāng)最后一行數(shù)據(jù)寫入結(jié)束時(shí),對(duì)應(yīng)的G圖像數(shù)據(jù)也計(jì)算完成,實(shí)現(xiàn)了圖像卷積計(jì)算結(jié)果的實(shí)時(shí)輸出。

圖2 圖像卷積計(jì)算過程

對(duì)于圖像首末行、列空缺數(shù)據(jù),根據(jù)計(jì)算要求采取相應(yīng)的方法。對(duì)于圖像濾波等操作,可以采用補(bǔ)值方法,將原圖像數(shù)據(jù)直接輸出補(bǔ)充該位空缺值;對(duì)于卷積神經(jīng)網(wǎng)絡(luò)、目標(biāo)識(shí)別等圖像操作,可以直接輸出計(jì)算結(jié)果,忽略空缺位置。

此外結(jié)合FPGA運(yùn)算準(zhǔn)則對(duì)卷積核與圖像數(shù)據(jù)間的函數(shù)計(jì)算進(jìn)行分析,如果僅涉及到加減法或者乘法運(yùn)算,例如邊緣梯度計(jì)算,F(xiàn)PGA內(nèi)部提供相應(yīng)IP核可以直接實(shí)現(xiàn)數(shù)值計(jì)算。但是對(duì)于均值濾波這種需要實(shí)現(xiàn)數(shù)據(jù)除法計(jì)算時(shí),F(xiàn)PGA內(nèi)部沒有直接使用的IP核,考慮到在FPGA中實(shí)現(xiàn)二進(jìn)制除法的復(fù)雜性,文中采用倒數(shù)求解法來實(shí)現(xiàn)除法的計(jì)算。首先將除數(shù)取倒數(shù)后轉(zhuǎn)換為二進(jìn)制的小數(shù)格式,整數(shù)保留一位(考慮到除數(shù)為1的情況)。然后,將被除數(shù)與該二進(jìn)制倒數(shù)相乘,計(jì)算結(jié)果的整數(shù)部分即為除法運(yùn)算的商。倒數(shù)求解法將除法運(yùn)算轉(zhuǎn)換為乘法運(yùn)算,使卷積計(jì)算的操作過程更簡便。

1.2 多級(jí)聯(lián)卷積實(shí)時(shí)計(jì)算

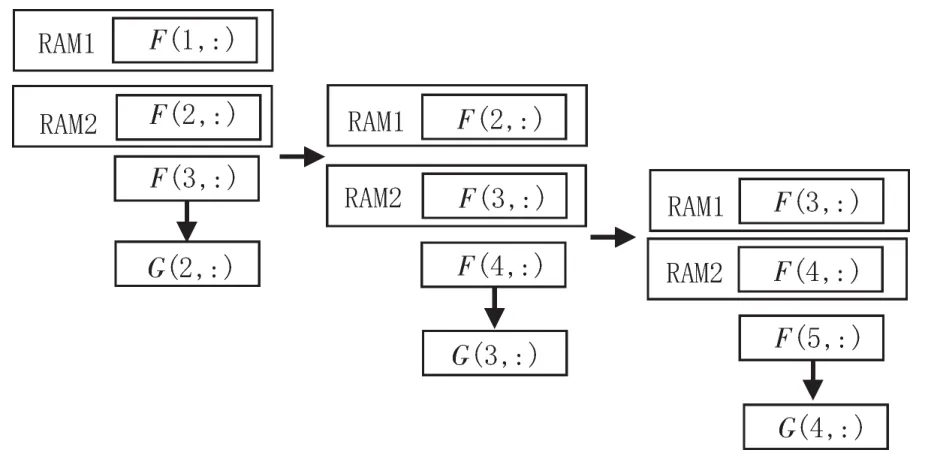

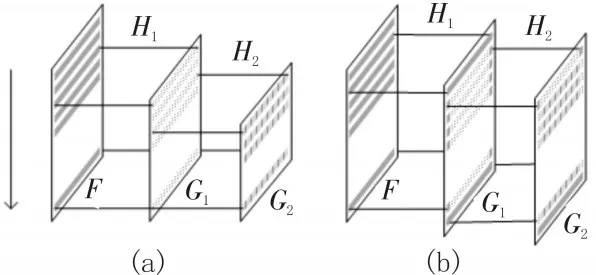

對(duì)于圖像處理中存在多級(jí)聯(lián)卷積計(jì)算時(shí),采用并行處理的方式實(shí)現(xiàn)圖像數(shù)據(jù)的實(shí)時(shí)傳輸。如圖3所示。

圖3 多級(jí)聯(lián)卷積計(jì)算過程

當(dāng)忽略圖像首末行、列數(shù)據(jù)缺省現(xiàn)象,即圖3(a)所示,原始圖像F逐行輸入卷積計(jì)算模塊,根據(jù)上節(jié)原理進(jìn)行計(jì)算,當(dāng)?shù)谌袛?shù)據(jù)輸入時(shí),經(jīng)過卷積核H1計(jì)算出的結(jié)果G1中第一行數(shù)據(jù)輸出,同時(shí)將圖像G1首行數(shù)據(jù)輸入卷積核為H2的卷積計(jì)算模塊中。依此類推,隨著圖像F的逐行輸入,F(xiàn)與卷積核H1的卷積計(jì)算結(jié)果G1實(shí)時(shí)逐行輸出;同時(shí)得到的G1圖像數(shù)據(jù)直接輸入下一級(jí)卷積計(jì)算模塊,實(shí)現(xiàn)與卷積核H2的計(jì)算。由此可以看出,最終輸出圖像G2的最后一行數(shù)據(jù)與輸入的原始圖像F最后一行數(shù)據(jù)同時(shí)結(jié)束,實(shí)現(xiàn)了多級(jí)聯(lián)圖像卷積計(jì)算的實(shí)時(shí)性。

當(dāng)圖像首末行、列數(shù)據(jù)空缺處填補(bǔ)數(shù)據(jù)的情況下,如圖3(b)所示,當(dāng)原始圖像F第二行數(shù)據(jù)輸入到卷積計(jì)算模塊時(shí),直接作為圖像G1首行數(shù)據(jù)輸出,同理其余行首末列數(shù)據(jù)直接輸出。當(dāng)圖像F最后一行數(shù)據(jù)輸入時(shí),經(jīng)過卷積核H1計(jì)算得到G2倒數(shù)第二行數(shù)據(jù),然后將F最后一行數(shù)據(jù)直接輸出,填補(bǔ)G1最后一行數(shù)據(jù)空缺。從圖中可以看出,G1輸出時(shí)間相比于原圖F延遲一行數(shù)據(jù)傳輸?shù)臅r(shí)間;G2輸出時(shí)間相比于G1延遲一行數(shù)據(jù)輸出時(shí)間,相比于F延遲兩行數(shù)據(jù)輸出時(shí)間。所以對(duì)空缺行列數(shù)據(jù)進(jìn)行補(bǔ)位的圖像卷積計(jì)算過程中,第N層卷積計(jì)算結(jié)果輸出圖像相比于原始圖像延遲N行數(shù)據(jù)輸出時(shí)間。該延遲時(shí)間相對(duì)于圖像數(shù)據(jù)的輸入時(shí)間可以忽略不計(jì),因此該系統(tǒng)實(shí)現(xiàn)了多級(jí)聯(lián)圖像卷積計(jì)算的實(shí)時(shí)性。

2 FPGA卷積計(jì)算系統(tǒng)仿真

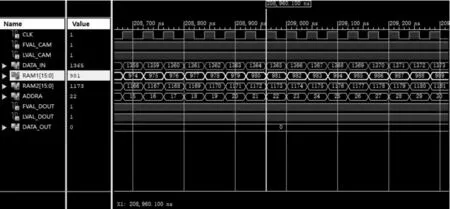

該文借助ISEM14.7仿真軟件對(duì)FPGA卷積計(jì)算過程進(jìn)行仿真。將原始圖像數(shù)據(jù)逐行排列轉(zhuǎn)換為txt文件。通過仿真程序依次讀取圖片數(shù)據(jù),同時(shí)按照Camera Link接口協(xié)議模擬FVAL、LVAL以及DVAL信號(hào)輸入。卷積計(jì)算中RAM復(fù)用仿真圖如圖4所示。

圖4 卷積計(jì)算系統(tǒng)信號(hào)仿真圖

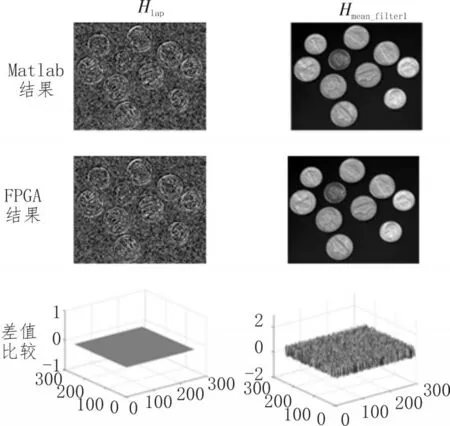

分別計(jì)算基于FPGA卷積圖像處理中均值濾波和拉普拉斯邊緣兩類卷積計(jì)算結(jié)果。將仿真結(jié)果與MATLAB軟件處理結(jié)果進(jìn)行比較,其結(jié)果如圖5所示。

圖5 FPGA、MATLAB卷積計(jì)算結(jié)果比較

通過比較FPGA仿真和MATLAB處理結(jié)果,可以看出FPGA系統(tǒng)設(shè)計(jì)有效地實(shí)現(xiàn)了圖像的卷積處理。其次對(duì)于類似拉普拉斯算子類型的僅包含圖像加法、乘法計(jì)算的卷積處理,F(xiàn)PGA處理結(jié)果與MATLAB計(jì)算結(jié)果一致;對(duì)于涉及除法運(yùn)算的卷積處理,例如均值濾波算子,F(xiàn)PGA計(jì)算結(jié)果與MATLAB處理結(jié)果相近但是存在差值。由于FPGA除法計(jì)算時(shí)進(jìn)行了除數(shù)取倒數(shù)操作,其倒數(shù)小數(shù)位有效位選取影響圖像計(jì)算結(jié)果。下面對(duì)FPGA圖像計(jì)算結(jié)果誤差進(jìn)行分析。

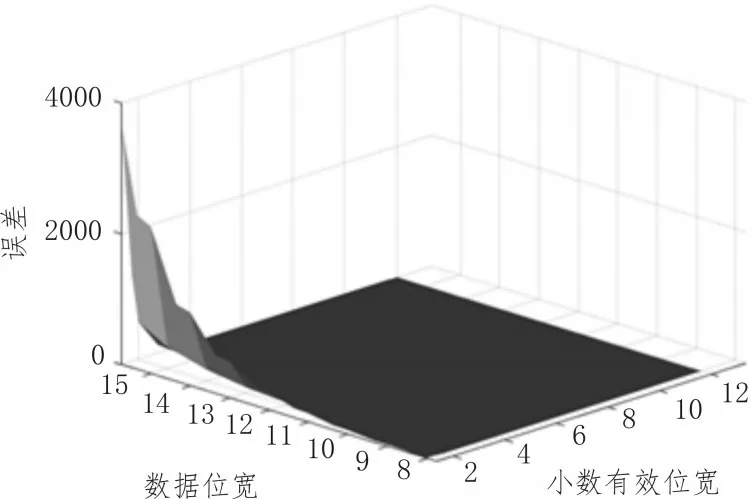

對(duì)于圖像數(shù)據(jù)位數(shù)和除法計(jì)算中倒數(shù)小數(shù)位數(shù)選取的不同,卷積計(jì)算結(jié)果存在差異。以均值濾波為例,卷積精確結(jié)果與FPGA除法運(yùn)算后的計(jì)算誤差為2n/10x,其中n是圖像數(shù)據(jù)位寬,x是小數(shù)有效位寬。誤差結(jié)果隨圖像數(shù)據(jù)位數(shù)和除數(shù)小數(shù)位數(shù)變化情況如圖6所示。

圖6 FPGA卷積計(jì)算誤差

從圖中可以看出,為了滿足系統(tǒng)誤差精度,對(duì)于圖像處理過程中不同位長的數(shù)據(jù),其除數(shù)小數(shù)位數(shù)選取也存在差異。對(duì)于文中相機(jī)輸出16位圖像數(shù)據(jù),除數(shù)倒數(shù)選取5位小數(shù),F(xiàn)PGA圖像處理卷積計(jì)算結(jié)果與計(jì)算真值誤差在一個(gè)灰度值內(nèi)。

通過仿真軟件對(duì)基于FPGA的卷積計(jì)算輸入輸出信號(hào)進(jìn)行分析,可以看出:整個(gè)系統(tǒng)實(shí)現(xiàn)了圖像卷積計(jì)算輸入輸出同步化的目的;同時(shí)對(duì)于包含除法類別的卷積計(jì)算,其誤差在一個(gè)灰度值之間。

3 FPGA卷積計(jì)算系統(tǒng)實(shí)驗(yàn)驗(yàn)證

3.1 卷積計(jì)算系統(tǒng)組成

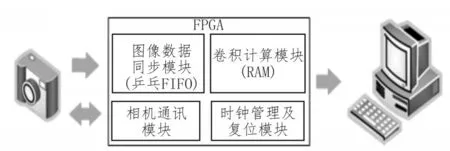

圖像采集及卷積計(jì)算處理結(jié)構(gòu)示意圖如圖7所示,主要包括相機(jī)數(shù)據(jù)采集、FPGA圖像處理以及結(jié)果輸出。系統(tǒng)的工作流程是:根據(jù)相機(jī)成像要求,F(xiàn)PGA生成控制指令,設(shè)置相機(jī)工作參數(shù)并發(fā)送攝像指令;經(jīng)過相機(jī)曝光后采集到的數(shù)據(jù)通過Camera Link接口傳輸?shù)紽PGA;FPGA接收到數(shù)據(jù)信號(hào)后,同步相機(jī)數(shù)據(jù)并進(jìn)行相應(yīng)的卷積計(jì)算,結(jié)果通過Camera Link接口輸出。其中相機(jī)與FPGA之間、FPGA與PC之間均通過Camera Link接口連接。

圖7 FPGA卷積計(jì)算系統(tǒng)結(jié)構(gòu)示意圖

FPGA內(nèi)部圖像處理主要分為4個(gè)模塊:時(shí)鐘管理及復(fù)位模塊、相機(jī)通訊模塊、數(shù)據(jù)同步模塊以及卷積計(jì)算模塊。時(shí)鐘管理及復(fù)位模塊提供了全局時(shí)鐘以及復(fù)位信號(hào);相機(jī)通訊模塊主要控制相機(jī)攝像參數(shù);圖像數(shù)據(jù)同步模塊實(shí)現(xiàn)相機(jī)輸入新號(hào)的同步操作;卷積計(jì)算模塊實(shí)現(xiàn)圖像卷積計(jì)算并輸出處理結(jié)果。文中選用VHDL語言完成模塊設(shè)計(jì),設(shè)計(jì)流程采用自上而下的設(shè)計(jì)方法。具體設(shè)計(jì)如下:

1)時(shí)鐘管理及復(fù)位模塊

時(shí)鐘管理及復(fù)位模塊主要產(chǎn)生整個(gè)系統(tǒng)所應(yīng)用到的時(shí)鐘以及復(fù)位信號(hào)。時(shí)鐘主要包括FPGA內(nèi)部工作時(shí)鐘、Camera Link接口通訊波特率時(shí)鐘,選用FPGA內(nèi)部時(shí)鐘管理單元DCM生成相應(yīng)頻率時(shí)鐘。復(fù)位操作在系統(tǒng)上電開始工作的同時(shí),對(duì)內(nèi)部信號(hào)及狀態(tài)賦上初始值,避免因初始值不確定導(dǎo)致后續(xù)程序出現(xiàn)錯(cuò)誤,增加系統(tǒng)可靠性。

2)相機(jī)通訊模塊

文中應(yīng)用EAGLE V 4240相機(jī)作為探測(cè)器,該型相機(jī)可以通過外部Camera Link接口實(shí)現(xiàn)對(duì)相機(jī)工作模式的控制,包括相機(jī)工作模式、工作溫度、快門延時(shí)時(shí)間、曝光時(shí)間、數(shù)據(jù)讀出速率、感興趣區(qū)域、binning模式設(shè)定等。相機(jī)與FPGA通訊波特率為115 200 bps,通過Camera Link接口中 SerTFG、SerTC兩路LVDS實(shí)現(xiàn)通訊,根據(jù)實(shí)際要求完成相機(jī)參數(shù)設(shè)定。

3)圖像數(shù)據(jù)同步模塊

相機(jī)輸出圖像通過Camera Link接口實(shí)時(shí)傳輸?shù)紽PGA。圖像有效數(shù)據(jù)位長為16 bit,相機(jī)輸出時(shí)鐘頻率為40 MHz,圖像大小為2 048×2 048,數(shù)據(jù)讀出速率為2 MHz。由于相機(jī)輸出時(shí)鐘、數(shù)據(jù)讀出速率均與FPGA工作時(shí)鐘異步,F(xiàn)PGA接收端口信號(hào)時(shí)需要對(duì)相機(jī)數(shù)據(jù)進(jìn)行緩存及同步處理。針對(duì)這種數(shù)據(jù)讀寫有序、輸入輸出時(shí)鐘異步的數(shù)據(jù),F(xiàn)PGA內(nèi)部采用乒乓FIFO的結(jié)構(gòu)接收?qǐng)D像數(shù)據(jù),實(shí)現(xiàn)數(shù)據(jù)的緩存及同步。

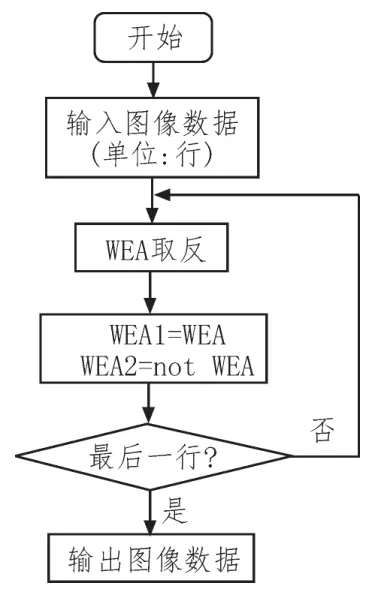

乒乓FIFO接收模塊工作示意圖如圖8所示。FPGA內(nèi)部設(shè)定兩個(gè)FIFO,每個(gè)FIFO位長為16 bit,位深為w。輸入時(shí)鐘連接Camera Link接口提供的數(shù)據(jù)有效信號(hào)DVAL,輸出時(shí)鐘連接FPGA內(nèi)部工作時(shí)鐘。WEA1、WEA2信號(hào)控制 FIFO1、FIFO2讀寫狀態(tài)。具體工作過程如下。

圖8 乒乓FIFO流程圖

對(duì)于輸入圖像行數(shù)據(jù),一個(gè)FIFO寫入數(shù)據(jù),另外一個(gè)FIFO讀出數(shù)據(jù);在下行數(shù)據(jù)輸入時(shí),兩個(gè)FIFO讀寫互換,交替進(jìn)行,直至最后一行圖像數(shù)據(jù)同步結(jié)束。根據(jù)乒乓FIFO模塊設(shè)置,Camera Link接口輸入的相機(jī)數(shù)據(jù)逐行緩存同時(shí)輸出同步圖像數(shù)據(jù)。同步后的圖像數(shù)據(jù)輸入到卷積計(jì)算模塊,進(jìn)行后續(xù)圖像操作。

4)卷積計(jì)算模塊

通過乒乓FIFO同步后的圖像數(shù)據(jù)輸入到卷積計(jì)算模塊,根據(jù)上節(jié)介紹的卷積計(jì)算方法,循環(huán)利用RAM存儲(chǔ)數(shù)據(jù)及計(jì)算,獲取卷積處理后的結(jié)果。對(duì)于多級(jí)聯(lián)卷積計(jì)算,并行處理圖像數(shù)據(jù),實(shí)現(xiàn)實(shí)時(shí)圖像的處理及輸出。

3.2 系統(tǒng)實(shí)驗(yàn)結(jié)果

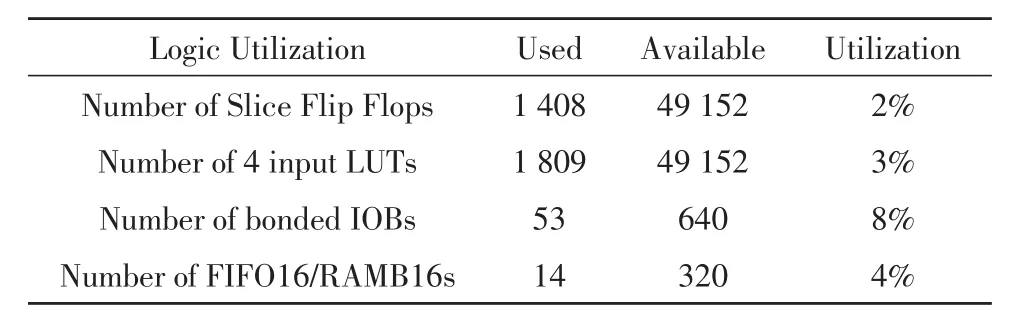

對(duì)于FPGA多級(jí)聯(lián)卷積計(jì)算操作,以實(shí)現(xiàn)原始圖像濾波后對(duì)圖像邊緣進(jìn)行提取為例,完成圖像兩層卷積計(jì)算。將編譯好的程序燒錄至xc4vsx55芯片中,實(shí)現(xiàn)圖像多級(jí)聯(lián)卷積計(jì)算功能。FPGA內(nèi)部資源如表1所示。

表1 FPGA內(nèi)部資源

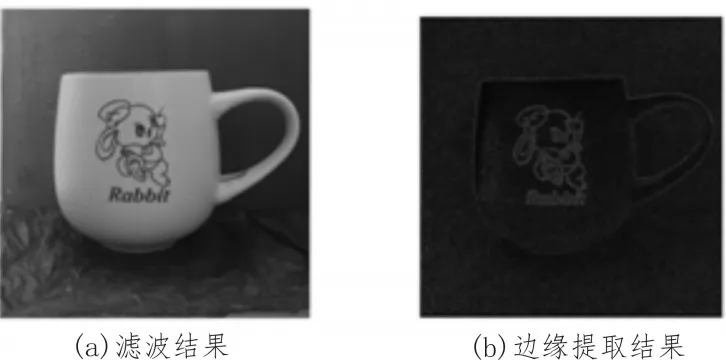

通過相機(jī)拍攝圖像,對(duì)相機(jī)圖像依次進(jìn)行均值濾波和邊緣檢測(cè)操作,F(xiàn)PGA輸出的結(jié)果如圖9所示,實(shí)驗(yàn)證明基于FPGA實(shí)現(xiàn)了圖像多級(jí)聯(lián)卷積計(jì)算、輸入輸出同步化操作。

圖9 圖像多級(jí)聯(lián)卷積計(jì)算實(shí)驗(yàn)結(jié)果

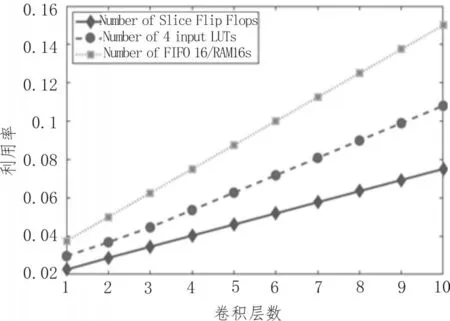

對(duì)于多級(jí)聯(lián)卷積計(jì)算,隨著卷積層數(shù)不同,F(xiàn)PGA內(nèi)部資源利用率也存在差異。FPGA資源利用率與圖像卷積計(jì)算層數(shù)之間的關(guān)系如圖10所示。

圖10 卷積層數(shù)與FPGA資源利用率關(guān)系

從圖中可以看出,F(xiàn)IFO/RAM數(shù)量隨卷積層數(shù)增多均勻增加,每增加一層卷積計(jì)算,RMA數(shù)量增加4個(gè);對(duì)于LUT以及FF利用率也隨著卷積層數(shù)增加而增加。由于每層卷積計(jì)算所需的資源僅僅與圖像列數(shù)相關(guān),與圖像行數(shù)無關(guān),即使大尺寸圖像卷積計(jì)算,其FPGA的資源利用率也不大。

通過FPGA內(nèi)部FIFO以及RAM的復(fù)用,有效地實(shí)現(xiàn)了實(shí)時(shí)多級(jí)聯(lián)圖像卷積計(jì)算。在相機(jī)獲取圖像后的圖像預(yù)處理中,能夠同步獲取包括濾波、邊緣提取、特征提取等涉及卷積計(jì)算的圖像處理結(jié)果,為后續(xù)圖像處理做準(zhǔn)備,同時(shí)節(jié)約了圖像處理時(shí)間以及硬件資源。在整個(gè)圖像處理過程中,不需要外部存儲(chǔ)器對(duì)圖像進(jìn)行存儲(chǔ),可復(fù)用性好,不存在資源浪費(fèi)現(xiàn)象。同時(shí)接口靈活,可編程性強(qiáng),通過改變卷積核內(nèi)部權(quán)重值,能夠?qū)崿F(xiàn)不同的卷積計(jì)算。對(duì)于多級(jí)聯(lián)卷積計(jì)算,卷積層間互不相關(guān),可單獨(dú)使用,也可以疊加使用,系統(tǒng)設(shè)計(jì)操作簡單;同時(shí)實(shí)現(xiàn)了輸入輸出圖像同步化,滿足系統(tǒng)實(shí)時(shí)性要求。

4 結(jié)論

文中提出一種基于FPGA實(shí)時(shí)對(duì)圖像數(shù)據(jù)多級(jí)聯(lián)卷積計(jì)算的系統(tǒng)方案。在圖像數(shù)據(jù)采集階段實(shí)現(xiàn)數(shù)據(jù)采集和圖像預(yù)處理卷積計(jì)算一體化。整個(gè)系統(tǒng)不需要外部存儲(chǔ)器來存儲(chǔ)整幅圖像,存儲(chǔ)空間要求僅與卷積核的寬度相關(guān),不需要考慮原始圖像的寬度,大大降低了圖像處理對(duì)FPGA存儲(chǔ)空間的要求。同時(shí)可編程性強(qiáng),可以實(shí)現(xiàn)不同類型卷積計(jì)算。對(duì)于多級(jí)聯(lián)卷積計(jì)算,卷積計(jì)算結(jié)果實(shí)時(shí)輸出,實(shí)現(xiàn)系統(tǒng)輸入輸出圖像同步化。