淺談PCB串擾及抑制措施

孫寶來 王海剛 杜尚勇

摘 ?要:目的:分析引起串擾的各種因素,提出相應的抑制措施,實現印制電路板(PCB)串擾的最小化。方法:通過探討PCB中串擾的產生機理及影響,并結合實例分析。結果:得到了抑制PCB串擾的有效措施,如選擇合適元器件、合理布局布線、使用屏蔽層、實施阻抗匹配以及進行串擾分析和仿真。結論:通過有效的抑制措施,PCB串擾可以最小化,本文可以為工程師設計PCB時提供參考。

關鍵詞:串擾;抑制措施;印制電路板;PCB;機理最小化

1引言

在PCB板級和系統級的分析和設計方法中,信號完整性(Signal Integrity,簡稱SI)分析與設計是尤為重要的,且在硬件電路設計中的作用愈來愈明顯。 信號完整性通常是指信號線上的信號質量,反射、振鈴、地彈和串擾,均屬于信號完整性問題范疇。其中,信號串擾最為復雜,涉及許多因素,難以計算和控制。本文重點分析信號串擾問題以及如何抑制。

2串擾的產生機理

串擾是指當信號在傳輸線上傳輸時,由于電磁耦合,它會對相鄰的傳輸線產生不良影響,一定的耦合電壓和耦合電流注入到了受干擾信號中。除了時鐘信號和周期信號,其它的關鍵信號,如數據、地址、控制和I / O走線等,都會受到這種非期望的電磁耦合的影響,這就是串擾。尤其需要關注的是呈現周期性的一些信號,如時鐘等。串擾超過某個閾值可能會引起電路故障并導致系統無法正常工作。

串擾發(fā)生的要素有兩個,即噪聲源線和噪聲源接收線。其中,噪聲源線是指產生耦合信號的傳輸線,而噪聲源接收線是指信號被耦合到的傳輸線。如圖1所示,傳輸線A的快速電平變化,會導致傳輸線B受到干擾,在傳輸線B上會產生干擾電壓或干擾電流。

串擾按照耦合方式分為容性串擾和感性串擾兩種。

2.1 容性串擾

容性串擾指的是兩條信號線之間通過耦合電容產生的干擾,如圖2所示。

因為走線之間存在耦合電容Cm,當噪聲源線的電壓變化時,噪聲就會從噪聲源線耦合到噪聲接收線上。引發(fā)的耦合電流就會在傳輸線的兩個方向傳輸,并在源端和負載端的阻抗處產生電壓,直到它被源和負載消耗掉。而在源端和負載端存在阻抗不匹配的情況時,就會發(fā)生反射,最終導致負載端出現較大的電壓尖峰。噪聲電壓的大小與噪聲源線的電壓變換率成正比,通常可以由公式(1)計算:

由于兩條傳輸線之間的耦合電容與傳輸線之間的距離有關,兩信號之間的距離越近,耦合電容越大,容性串擾越嚴重。所以,為了減少容性串擾,應盡可能加大傳輸線之間的距離。也可以在兩條傳輸線之間放置地線,作為隔離措施,消除耦合電容,從而消除容性串擾。

2.2 感性串擾

感性串擾指的是兩條信號線有電流流過時,通過它們之間的變壓器效應產生互感耦合,最終在噪聲接收線處產生干擾,如圖3所示。

當噪聲源線和噪聲接收線之間的距離足夠近,以致噪聲接收線被噪聲源線產生的磁場所包圍時,會在噪聲接收線上產生感應電流,這個感應電流由磁場產生。在電路模型中,該電流可以通過互感參數來表征。互感系數Lm表示驅動傳輸線通過磁場將電流感應到另一傳輸線的程度。受害線上產生的噪聲,則與驅動線的電流變化率有關,噪聲電壓的大小與電流變換率成正比,通常可以由公式(2)計算:

同樣的,由于感性串擾的大小與終端負載阻抗有關,負載阻抗越大,產生的干擾電壓越大,因此為了減少感性串擾,可以減小負載阻抗,或者通過終端阻抗匹配來抑制反射。

3串擾的影響

串擾一般是在噪聲接收線上產生耦合電壓和耦合電流,從而引起接收端處的電平變化。接收端的噪聲容限決定這種電平變化是否會使接收端產生誤觸發(fā)。這里的噪聲容限是指門電路的抗干擾能力,包括低電平噪聲容限VNL和高電平噪聲容限VNH,如圖4所示。

其中高、低電平噪聲容限可由公式(3)(4)計算:

式中:

VOH(min)——輸出的高電平的最小電壓值;

VIH(min)——輸入的高電平的最小電壓值;

VIL(max)——輸入的低電平的最大電壓值;

VOL(max)——輸出的低電平的最大電壓值。

對于驅動器端,輸出的高電平不低于VOH(min),輸出的低電平不高于VOL(max)。而對于接收端輸入來說,只要高于VIH(min)即可以保證接收到邏輯1,只要低于VIL(max)即可保證接受到邏輯0。而如果輸入電壓值位于VIH(min)和VIL(max)之間的區(qū)域時,可能被接收電路判為1,也可能判為0。因此對于接收電路來說,輸入的電壓值不能處于這個不定態(tài)區(qū)域中。

高、低電平噪聲容限越大,表示電路的抗干擾能力越強。當串擾引起接收端的電平變化超過其噪聲容限時,就會引起接收端的誤動作,可能直接導致整個系統無法正常工作。

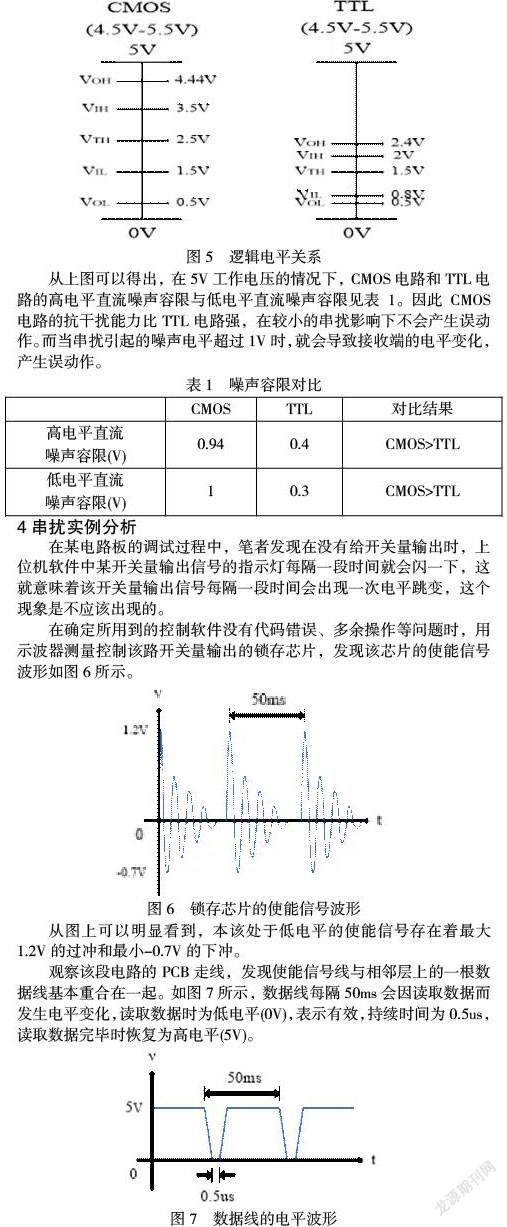

各種類型的集成電路中,以最常見的CMOS和TTL為例,它們的邏輯電平關系如圖5所示。

從上圖可以得出,在5V工作電壓的情況下,CMOS電路和TTL電路的高電平直流噪聲容限與低電平直流噪聲容限見表1。因此CMOS電路的抗干擾能力比TTL電路強,在較小的串擾影響下不會產生誤動作。而當串擾引起的噪聲電平超過1V時,就會導致接收端的電平變化,產生誤動作。

4串擾實例分析

在某電路板的調試過程中,筆者發(fā)現在沒有給開關量輸出時,上位機軟件中某開關量輸出信號的指示燈每隔一段時間就會閃一下,這就意味著該開關量輸出信號每隔一段時間會出現一次電平跳變,這個現象是不應該出現的。

在確定所用到的控制軟件沒有代碼錯誤、多余操作等問題時,用示波器測量控制該路開關量輸出的鎖存芯片,發(fā)現該芯片的使能信號波形如圖6所示。

從圖上可以明顯看到,本該處于低電平的使能信號存在著最大1.2V的過沖和最小-0.7V的下沖。

觀察該段電路的PCB走線,發(fā)現使能信號線與相鄰層上的一根數據線基本重合在一起。如圖7所示,數據線每隔50ms會因讀取數據而發(fā)生電平變化,讀取數據時為低電平(0V),表示有效,持續(xù)時間為0.5us,讀取數據完畢時恢復為高電平(5V)。

分析后,可以確定該數據線為噪聲源。在讀取數據的時候,數據線上快速的沿的變化,通過容性耦合在使能信號線上產生串擾,致使使能信號線上的電平每隔50ms出現一次振鈴現象。當使能信號線上的干擾電壓過大(大于鎖存芯片的噪聲容限,約為0.8V)時,會使得鎖存芯片誤動作,從而導致開關量輸出信號的電平發(fā)生跳變,造成指示燈閃爍。

原因查明后,通過更改走線的方式,將使能信號線稍微遠離數據線后,故障現象消失。再用示波器觀察使能信號線上的波形,發(fā)現干擾電壓依然存在,但幅值降低了許多(最大過沖為0.5V,最小下沖為-0.2V)。若要進一步減小串擾,可以通過繼續(xù)加大使能信號線和數據線的距離,在使能信號線旁增加地保護走線,或者在它們之間增加地線層等方法來達到目的。

5串擾抑制措施

設計PCB時,減少干擾源網絡與被干擾網絡之間的耦合,可以達到減小對系統具有負面影響的串擾現象的目的,但在復雜的PCB設計中不可能完全避免串擾。設計人員應考慮選擇適當的方法以最小化串擾而不影響系統的其它性能。結合以上分析,主要從以下幾個方面考慮解決串擾問題的方法:

(1)采用降低信號沿的變換速率的方法。由于高速信號易于對低速信號引起串擾,所以在滿足PCB設計的前提下,可嘗試選擇慢速器件以減慢電場和磁場的變化速率,并避免混合使用不同類型的信號。

(2)在布局PCB時應遵循的原則見表2。

(4)使用屏蔽方法。提供用于高速信號的數字接地是解決串擾問題的有效方法。但是,包地會增加布線量,使原來有限的布線區(qū)域更加擁擠。另外,為了實現接地線屏蔽以達到期望,接地線上的接地點之間的距離至關重要,通常小于信號變化沿長度的兩倍。同時,地線還將增加信號的分布電容,這將增加傳輸線的阻抗并減慢信號沿。由于表面層僅具有一個參考平面,因此表面層布線的電場耦合要強于中間層,因此對串擾更敏感的信號線應盡可能放置在內層中。

(5)實施傳輸線阻抗匹配。串擾的幅度跟終端阻抗與傳輸線阻抗是否匹配息息相關,因此可以通過端接,大大降低串擾的影響。如應用串聯終端、并聯終端、戴維南終端、AC并聯終端和二極管終端等傳輸線端接方式確保最優(yōu)的信號完整性和最小化射頻能量。其中比較常采用的是串聯終端匹配方式,簡單且低功耗,但減慢了負載端的信號上升沿時間。

(6)進行串擾分析和仿真。串擾分析的目的是為了在 PCB 實現中迅速地發(fā)現、定位和解決串擾問題。在仿真工具中可以設定電氣規(guī)則和物理規(guī)則,對可能的串擾進行仿真分析,并在布線時自動計算信號完整性要素,例如過沖和串擾。確定串擾是否會出現超出噪聲容限,可根據計算的結果自動修正布線再繼續(xù)分析修正,最終形成一個最小化串擾的解決方案。

6結論

本文通過探討PCB中串擾的產生機理及影響,并結合實例分析了引起串擾的各種因素,提出了選擇合適元器件、合理布局布線、使用屏蔽層、實施阻抗匹配以及進行串擾分析和仿真等措施,有效抑制PCB的串擾。隨著PCB日益高速和高密度,受限于設計面積和制造成本,串擾最小化變得尤為重要。本文可以為工程師設計PCB時提供參考,在成本和性能之間達到最好的平衡。

參考文獻:

[1]汪思敏,唐廣芝.PCB和電磁兼容設計(第2版)[M].機械工業(yè)出版社,2008,6.

[2]喬洪.高速PCB串擾分析及其最小化[J].中國集成電路,2007.

[3]周萍.高速PCB板的信號完整性設計[J].電子質量,2009.

[4]邵震洪,趙杭生.高速數字電路的PCB設計.[J].現代軍事通信,2005.

作者簡介:

孫寶來(1986-),男,工程師,主要從事電子對抗技術方面的研究工作。