傳輸線中高速信號反射建模分析與優化

陳章進,王文磊,季 淵,3,黃舒平,3

(1.上海大學微電子研究與開發中心,上海 200072;2.上海大學計算中心,上海 200072;3.上海昀光微電子有限公司,上海 200072)

隨著集成電路技術的發展,信號頻率提升迅速,部分服務器設計中已經出現了25 Gbit/s的設計.在高速電路設計中,單向點對點傳輸線在印制板布線中占有很大比重.在傳統的電路中如控制總線、地址總線均采用單向點對點傳輸線.在印制板的設計中,隨意繪制的信號線雖然在理論上能夠起到信號傳輸的作用,但在高速電路中寄生電容與電感將嚴重影響信號的傳輸質量,產生不必要的信號振蕩與過沖.信號振蕩與信號過沖廣泛存在于各種低速、高速電路中.過沖與振蕩不僅會削弱信號質量,造成信號能量的損失和誤碼,過高的過沖電壓還會對輸出端器件與接收端器件造成損害,嚴重的會造成器件的燒毀.

傳統電路分析方法大多是逐個因素分析,Doi[1]對高速互連線的基本特性進行了比較詳盡的分析研究.Ahn 等[2]對差分線的阻抗匹配等問題進行了比較詳盡的研究.在工程上,文獻[3-8]對高速電路中的過孔、傳輸線特性、信號振蕩進行了比較系統的闡述.在實際工程應用中,傳輸線中信號振蕩與過沖往往是多個因素作用的結果,因此振蕩與過沖的解決除依靠工程師的經驗,還需要進一步的建模和仿真分析.

本工作采用電路分布式模型與集總模型相結合的方式,對單向點對點傳輸線進行建模,分析構成傳輸線的過孔、線長對單向傳輸線信號振蕩的影響,推導振蕩與信號過沖的理論公式,并提出了解決信號振蕩與過沖的方案.最后,通過仿真驗證了方案的正確性,目前本設計方案已經成功應用于多個產品的設計中.

1 電路模型構建與分析

1.1 信號反射原理

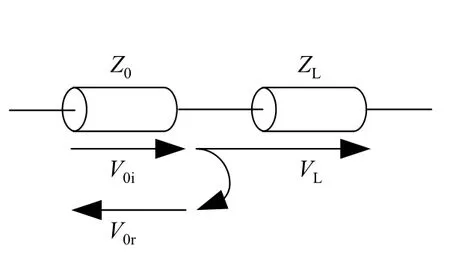

信號反射是信號在傳輸線上的回波,是影響信號傳輸質量的一個最基本也是最主要的原因.多次的信號反射疊加形成信號振蕩[9].本工作通過分析信號反射原理,對傳輸信號電路建立集總參數模型(見圖1).

圖1 傳輸線信號反射示意圖Fig.1 Transmission line signal reflection diagram

在傳輸信號電路中增加一個負載電阻ZL,輸入電壓為V0i,傳輸電壓為VL,反射電壓為.此時

從反射系數方程可以看到,當Z0=ZL時,反射系數Γ=0,此時信號無反射,這種情況是最理想的阻抗匹配狀態.阻抗的反射會與新輸入的信號發生疊加,產生信號過沖,多次反射會形成信號振蕩.

理論上解決傳輸線信號反射的問題除了控制線寬、優化過孔設計與數量外,最為常見也是最有效的方法是采用合理的阻抗匹配方案.阻抗匹配方案主要有4 種:串聯阻抗匹配方案、并聯阻抗匹配方案、戴維南阻抗匹配方案、RC 串聯阻抗匹配方案[11].在通常情況下,阻抗匹配方案采用串聯阻抗匹配或并聯阻抗匹配方案.串聯阻抗匹配方案直接便捷,但電路中的串聯電阻會造成信號電壓的分壓,衰減的信號電平可能造成信號數據丟失.而并聯阻抗匹配方案的優勢是并聯阻抗匹配端接電壓(termination voltage,VTT)的存在使得信號有著更好的信號邊沿特性,當采用特定端接電壓時,信號具有更好的上升沿與下降沿.但端接電壓的存在會改變信號的占空比,可能會導致數據的丟失.

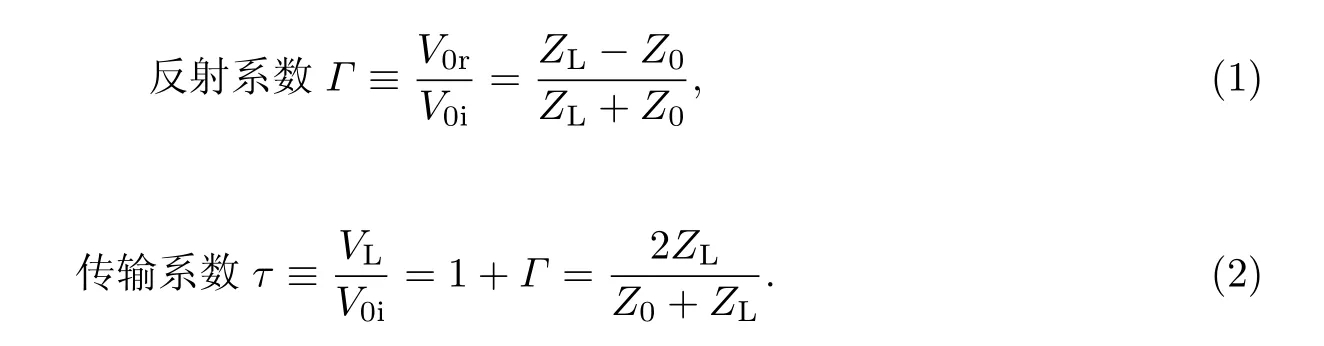

1.2 傳輸線分布式模型

在印制線路板(printed circuit board,PCB)中,任何傳輸線都或多或少會存在一定程度的信號反射問題.本工作在傳統集總電路模型基礎上,結合電路的分布式模型進行分析(見圖2).

圖2 傳輸線分布式模型Fig.2 Transmission line distributed model

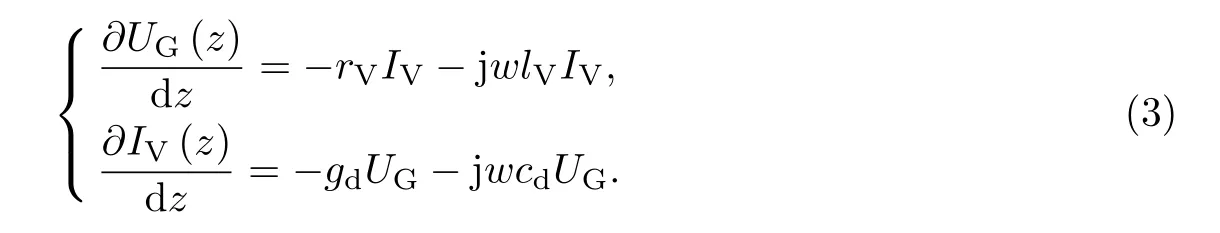

在圖2 中,rV和lV是電路的分布電容與分布電感,gd和cd是對參考面的等效電容與等效電抗.根據基爾霍夫電路定律,建立如下微分方程求解圖2 中UG與IV,

根據Z0=UG/IV,可以求得傳輸線特征阻抗

在高頻情況下,傳輸線的分布感抗遠遠大于分布電阻,分布容抗遠遠大于分布電導,即,此時可以對Z0進行化簡,

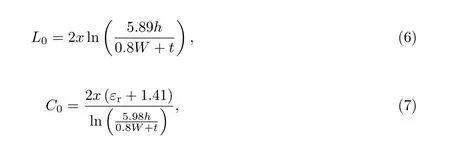

根據文獻[3,10]對rV,lV分布電容(nH)與分布電感(pF)進行積分,得到傳輸線的等效電感L0和等效電容C0,

式中:x為傳輸線長度;h 為傳輸線與基準面的高度;W為傳輸線線寬;t 為銅箔厚度;εr為印制板介電常數.此時傳輸線造成信號的上升延遲

從式(8)可以看到,傳輸線特征阻抗與傳輸線的長度無關,與印制板的材料、疊層設計有關.此時傳輸線的過沖電壓為

在一定頻率下,為了防止信號反射回波影響后續信號輸入,同時保證不發生信號反射,求取最大傳輸線長度為Lmax.根據文獻[12]以及工程經驗,傳輸線最大信號傳輸頻率fmax與信號的傳輸延時tpd存在經驗公式:

此時最大傳輸線長度

1.3 傳輸線中過孔建模

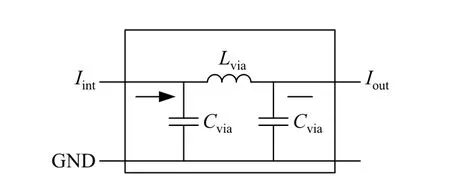

過孔是電路設計中不可缺少的一部分,過孔的主要功能是實現信號的換層.在高密度互連(high density interconnector,HDI)設計過程中,信號扇出需要大量的過孔,過孔的存在對信號傳輸質量有一定影響.對過孔的分析需要建立電路等效集總模型,根據文獻[13]建立如圖3所示的過孔模型(圖中GND 代表地線).

圖3 過孔等效模型Fig.3 Via equivalent model

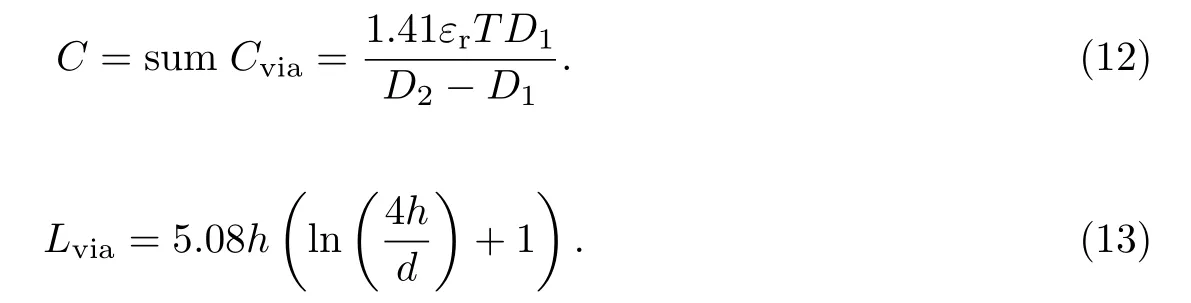

過孔等效電容與等效電感的大小與印制板的設計密切相關.通過計算分析得到過孔的等效電容和等效電感為C 和Lvia.過孔焊盤的直徑為D1,過孔在鋪地層上的隔離孔直徑為D2,基材介電常數為εr,PCB 板層厚度為T,d 為中心鉆孔的直徑,h 為過孔長度.

根據式(10),過孔對傳輸信號最大的影響是電容與電感造成的信號延遲,從而導致信號邊沿劣化.為降低信號反射的風險,過孔傳輸延時需要滿足

2 設計仿真驗證

2.1 硬件系統平臺搭建

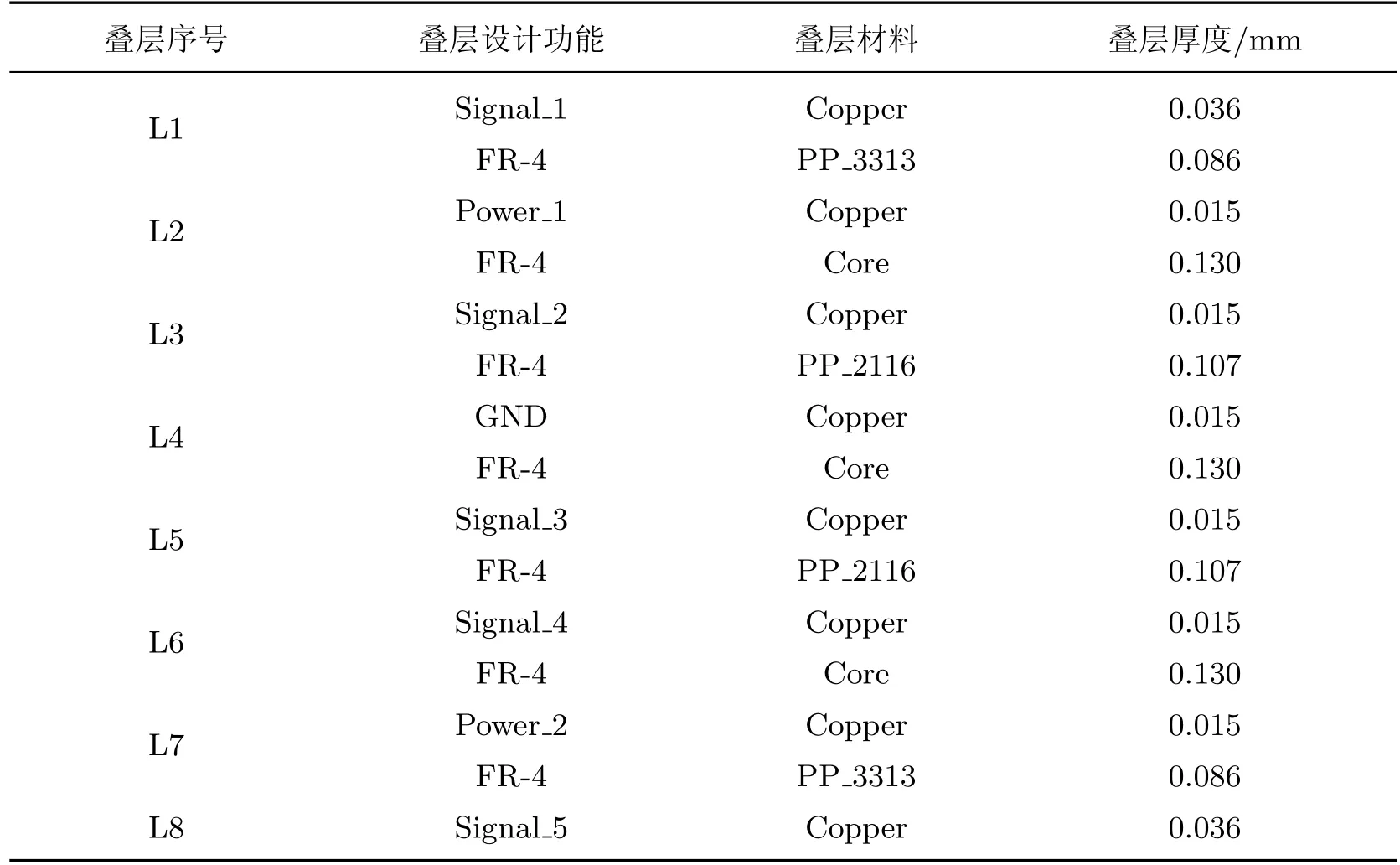

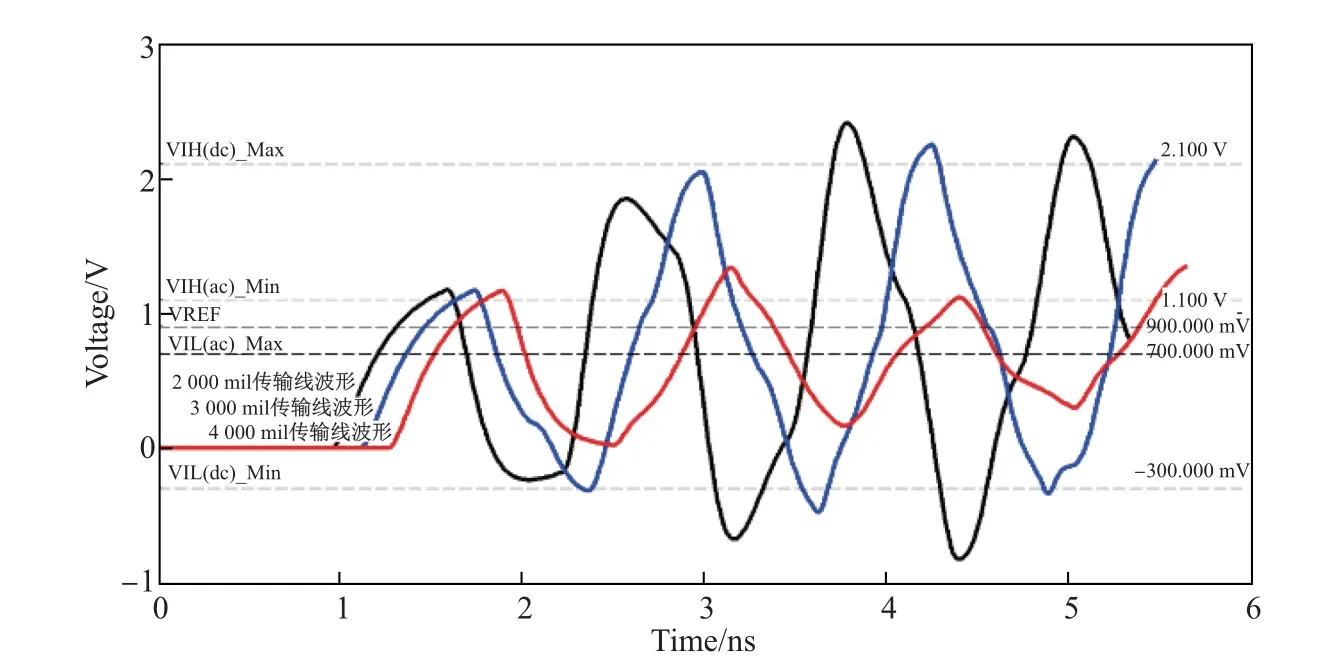

為解決某款高速現場可編程門陣列(field programmable gate array,FPGA)存儲系統設計中所遇到的信號反射問題,為工程設計提供一套可復用的規范化設計流程,本工作采用具有代表性的硬件產品.系統包含兩個DDR2,傳輸線類型為SSTL18[14],主控芯片采用Xilinx 的SPARTAN-6 系列.印制板設計采用了普通的FR-4 材料作為基材,介電常數εr為4.6,銅箔傳輸線損耗角為0.02[15].疊層設計采用了8 層電路板,印制板厚度為1.0 mm,具體配置如表1所示.差分線按廠家參考設計(見表2,表中1 mil=0.025 mm),傳輸線采用的是單端信號50 ?阻抗匹配、差分100 ? 阻抗匹配的方案.

表1 PCB 疊層設計參數Table 1 Design parameters of PCB stack

表2 PCB 廠家建議設計參數Table 2 Design parameters of PCB manufacturer’s suggested

在800 MHz 頻率下,通過式(5)~(7)計算得到,微帶線傳輸線特征阻抗Z0為48.8 ?,等效電感L 為7.307 2 nH/inch(1 inch=0.025 4 m),等效電容C 為3.065 6 pF/inch,傳輸延時tpd為149.670 7 ps/inch.根據式(11),傳輸線臨界長度Lmax為2 936 mil.此時輸入1.8 V 的沖激信號,接口內阻RS為50 ?.根據式(8)和(9),諧振系數Q 為0.976,產生的輸入端過沖電壓Vovershoot為0.277 V,信號增益為1.24 dB,不會對信號產生很強干擾.

考慮到目前國內制造工藝的限制,過孔內徑d 為8 mil,外徑D1為10 mil,PCB 總厚度h 為1.0 mm,反焊盤尺寸D2為16 mil.利用式(12)和(13),過孔電容C 為0.425 6 pF,過孔電感Lvia為0.796 0 nH,過孔等效阻抗為43.247 ?,諧振頻率為8 647.203 MHz,單個過孔對傳輸信號產生的信號延時tpd為20.245 9 ps.經過上述計算獲得,傳輸線長度不超過2 936 mil,過孔諧振頻率f 遠遠高于設計目標頻率Ftarget,單個過孔不會產生信號諧振影響傳輸線信號質量.通過式(14)計算,在保證信號質量的前提下,最大過孔數量為4 個.

2.2 設計仿真驗證

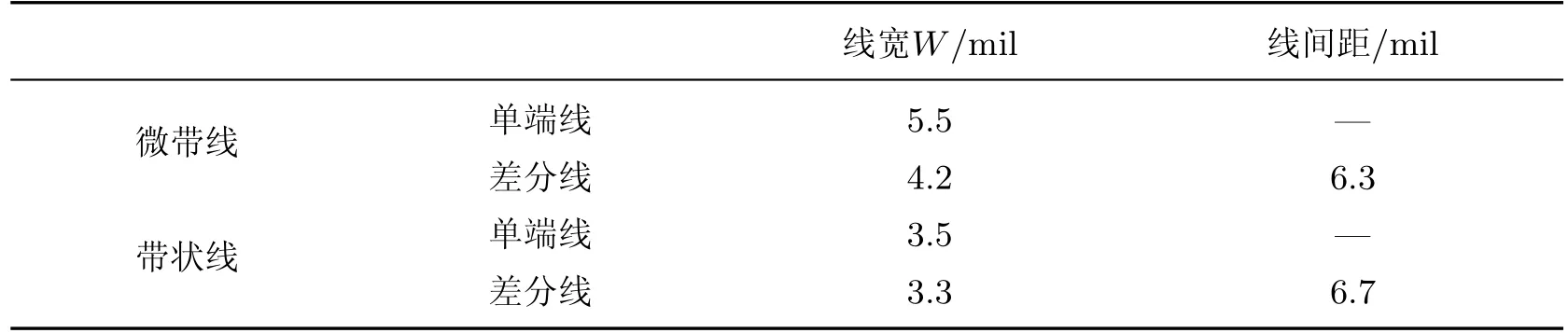

為了驗證理論推導的正確性及優化對設計方案的有效性,本工作采用Cadence Sigrity 軟件進行電路拓撲結構的提取與仿真,仿真模型采用Spartan-6 與Micrion DDR2 的IBIS 模型,Sparta-6 芯片接口類型為SSTL18-OT50-LR25,此時接口內阻為50 ?,管腳位置在芯片的左側,FPGA 芯片的輔助電壓為2.5 V.仿真傳輸線為內存地址線,采用地址線進行仿真所獲得的解決方案具有很高的可復用性.

2.2.1 傳輸線線長對信號的影響

通過式(6)和(7)的分析,傳輸線的長度會影響傳輸線的電容與電感.在不考慮信號串擾和電磁干擾/電磁兼容性(electromagnetic interference/electromagnetic compatibility,EMI/EMC)的情況下,增加的傳輸線電感與傳輸線電容會導致信號線產生信號振蕩.傳輸線仿真參數參照表1,仿真疊層為頂層,傳輸線中不添加過孔.通過計算可知,傳輸線的臨界長度為2 936 mil,因此仿真線長分別為2 000,3 000,4 000 mil(見圖4).

圖4 2 000,3 000,4 000 mil 仿真拓撲結構Fig.4 2 000,3 000,4 000 mil simulation topology structure

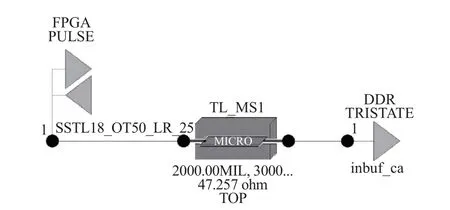

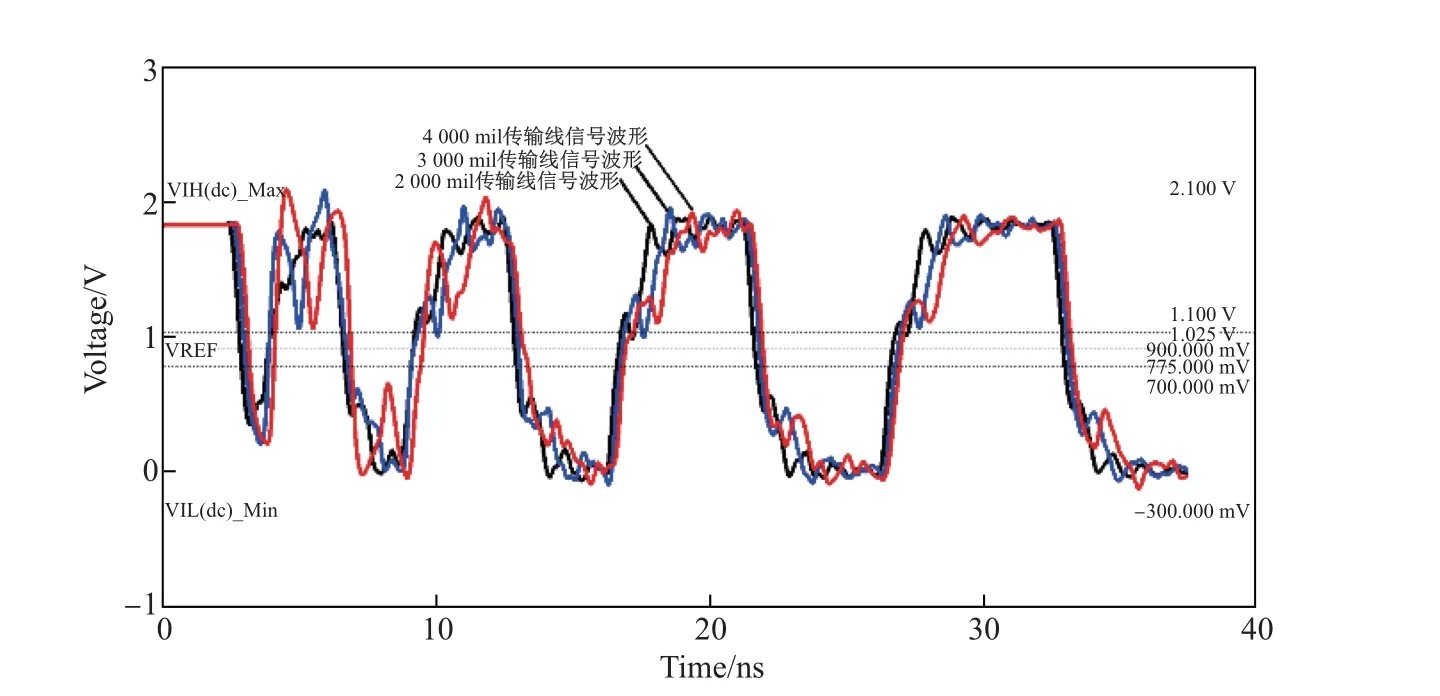

Cadence 計算阻抗為47.825 7 ?,獲得仿真波形如圖5 和6 所示.圖5 和6 中VIH(high input voltage)代表最高輸入門限電壓,VIL(low input voltage)代表最低輸入門限電壓,VREF(voltage reference)代表輸入基準電壓.由圖5 可見,在沒有其他空間干擾的情況下,4 000 mil 傳輸線已經不能保證信號電平達到信號的門限電壓,而在2 000 與3 000 mil 的傳輸線波形中,信號的過沖已經達到了信號的最大門限電壓.

圖5 傳輸線長度與信號反射仿真波形(脈沖序列)Fig.5 Transmission line length and signal reflection simulation waveform (pulse sequence)

由圖6 (仿真序列101100111000111100001111100000) 可見,進行脈沖序列仿真時,3 000 mil 傳輸線信號過沖已經達到門限電壓最大值,信號下沖也剛好達到了VIH(ac)高電平的下限值,存在較大的信號誤碼風險,同時也證明了理論計算Lmax的正確性.但在800 MHz 頻率下,雖然更短的傳輸線可以提供較好的信號電平,但2 000,3 000,4 000 mil 傳輸線均出現了比較嚴重的信號過沖與信號振蕩,在這種情況下,采用合理的阻抗匹配方式對保持信號質量有著重要意義.

圖6 傳輸線長度與信號反射仿真波形(仿真序列)Fig.6 Transmission line length and signal reflection simulation waveform (simulation sequence)

2.2.2 阻抗匹配方案設計

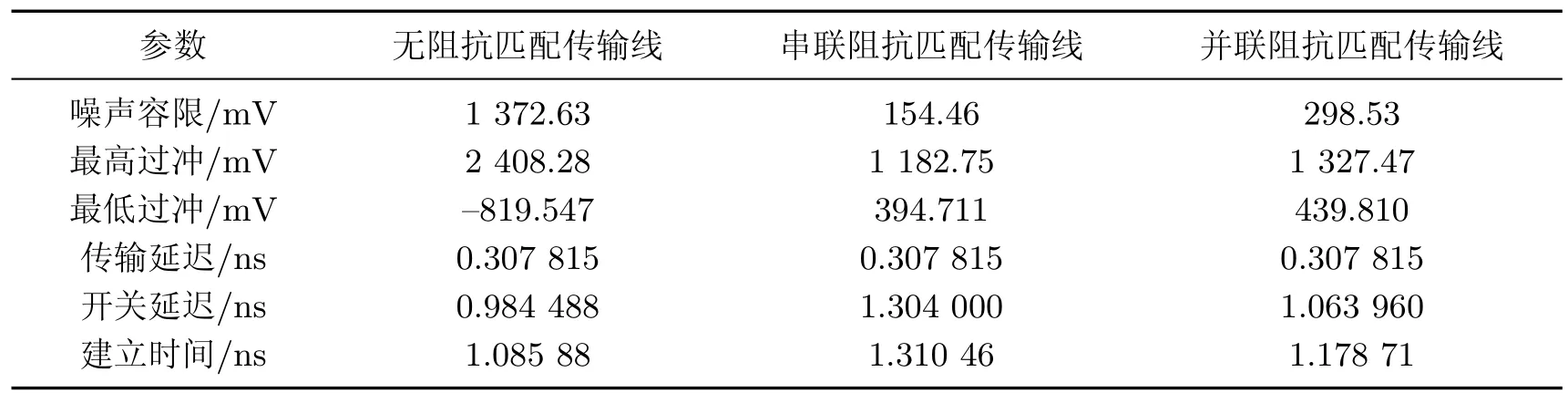

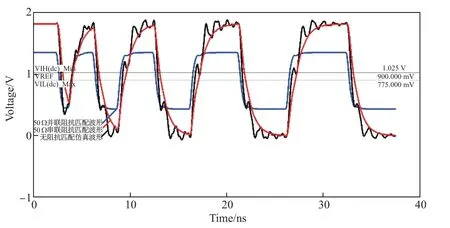

解決信號振蕩與過沖的方法主要有各類傳輸線的阻抗匹配方案,在仿真情況下,采用的阻抗匹配電阻均是50 ?.如圖7 所示,在800 MHz 頻率下,串聯阻抗匹配與并聯阻抗匹配對傳輸信號質量均有改善.根據2.1 節的分析,串聯阻抗匹配在削弱信號過沖的同時也削弱了信號強度.根據表3,并聯阻抗匹配相對串聯阻抗匹配在信號的建立時間與噪聲容限方面均有較大的改善,各項性能均優于串聯阻抗匹配,因此高速單向點對點的傳輸線阻抗匹配最優方案是采用50 ? 并聯阻抗匹配方案.

表3 串、并聯阻抗匹配與無阻抗匹配仿真參數Table 3 Series,parallel impedance matching and impedance matching simulation parameters

圖7 串、并聯阻抗匹配與無阻抗匹配仿真波形Fig.7 Simulation waveform of series,parallel impedance matching and impedance matching

2.3 并聯阻抗布局設計

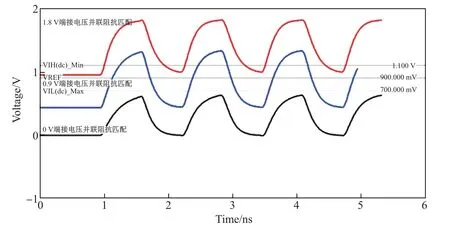

并聯阻抗匹配設計涉及端接電壓值的設計,端接電壓能夠解決過長傳輸線導致的信號壓降問題,同時也能夠優化信號邊沿.但端接電壓的存在可能會導致信號占空比發生改變,影響信號質量.為獲得具有可復用性的方案,本工作通過仿真驗證并聯阻抗匹配方案中的端接電壓對信號質量改善的效果.

由圖8 可見,不同的端接電壓值會影響信號傳輸質量,導致信號的傳輸電平異常,影響信號的邊沿特性和占空比.在設計并聯阻抗匹配時,端接電壓值根據信號頻率與信號幅度綜合仿真確定,本方案中最佳端接電壓為0.9 V.

圖8 端接電壓與信號傳輸質量仿真波形Fig.8 Simulation waveforms of terminal voltage and signal transmission quality

2.4 現實方案設計優化

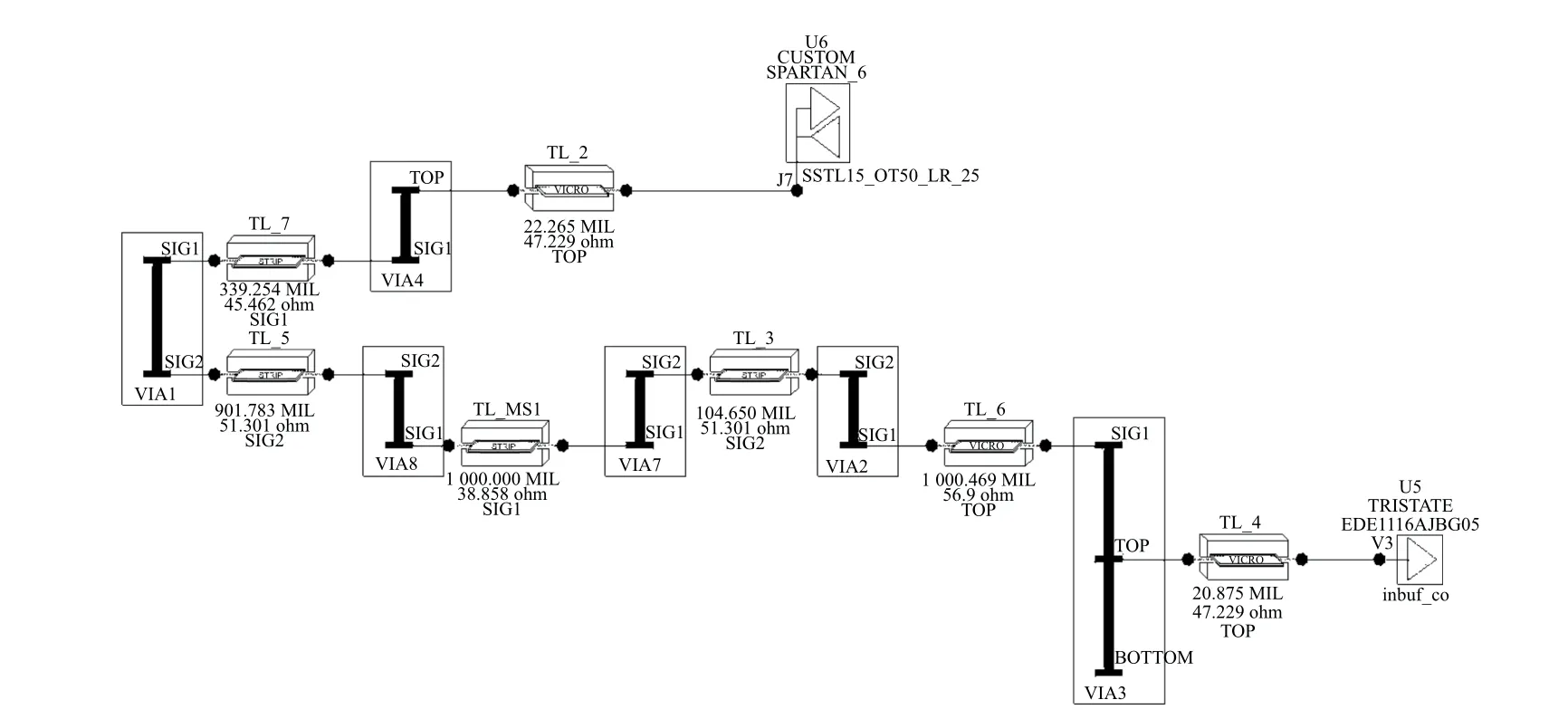

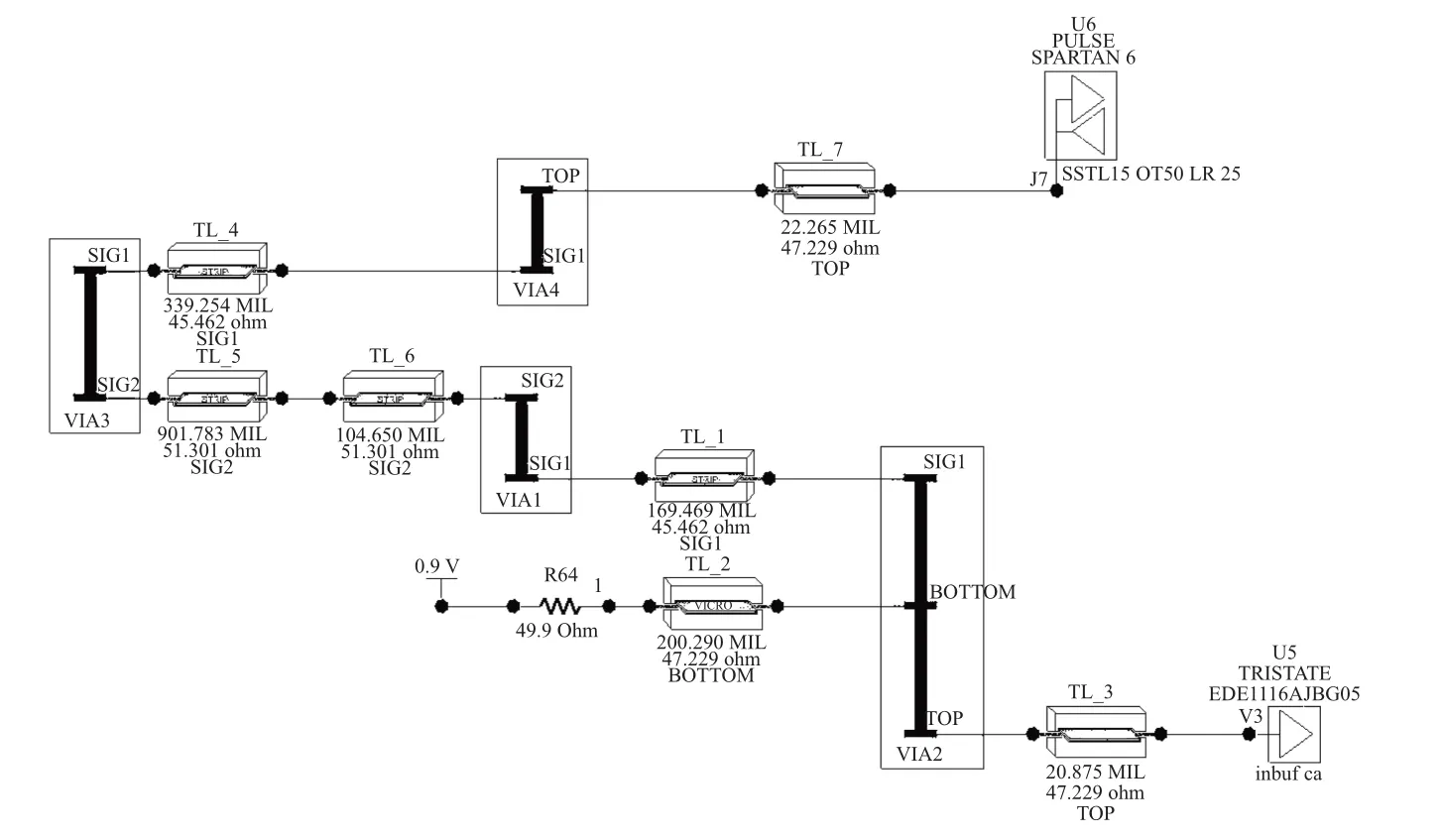

通過理論分析和建模仿真,本工作在高速單向點對點傳輸線設計中,采用0.9 V,50 ? 末端阻抗方案.對設計方案進行優化后,過孔的數量減少為4 個,傳輸線長度縮短到1 750 mil,端接電壓采用0.9 V VTT 基準電壓,匹配電阻為50 ?,采用的是末端并聯電阻匹配方案.信號輸入接口標準采用SSTL18.優化設計前后,利用Cadence Sigrity 對電路板進行拓撲提取對比設計優化差異,如圖9 和10 所示.

圖9 優化前傳輸線拓撲結構Fig.9 Transmission line topology before optimization

圖10 優化后傳輸線拓撲結構Fig.10 Transmission line topology after optimization

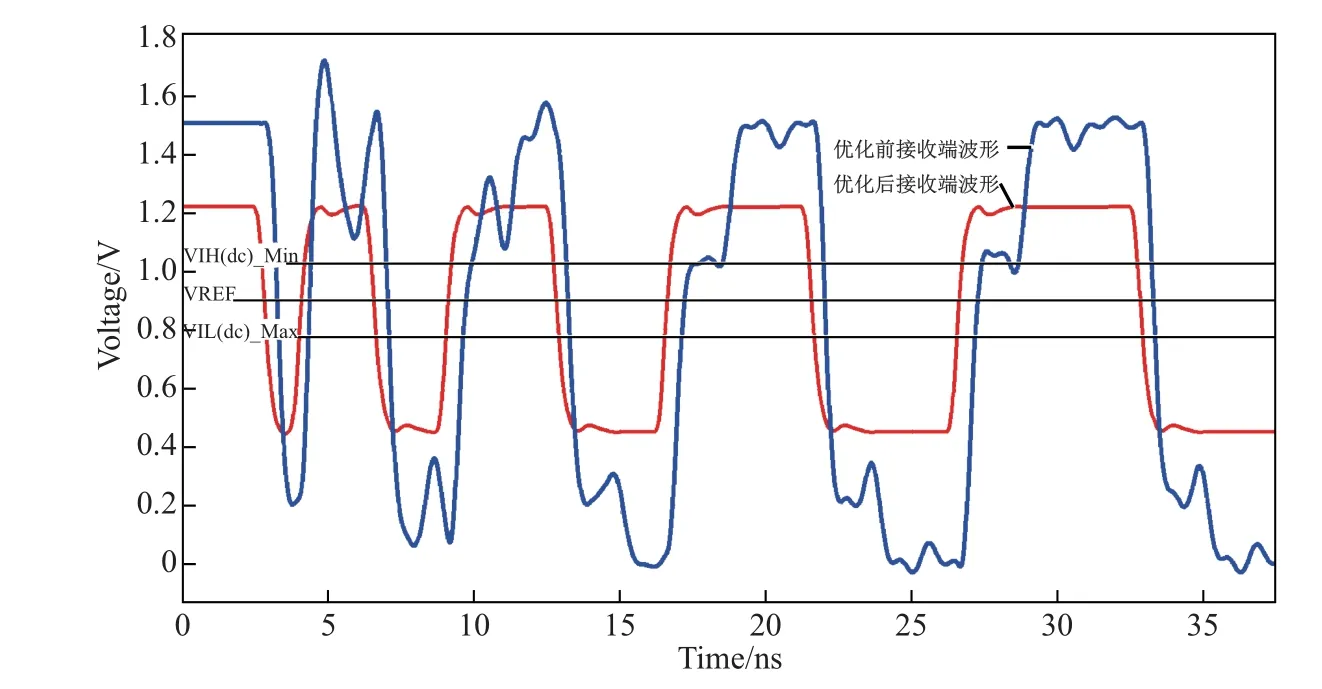

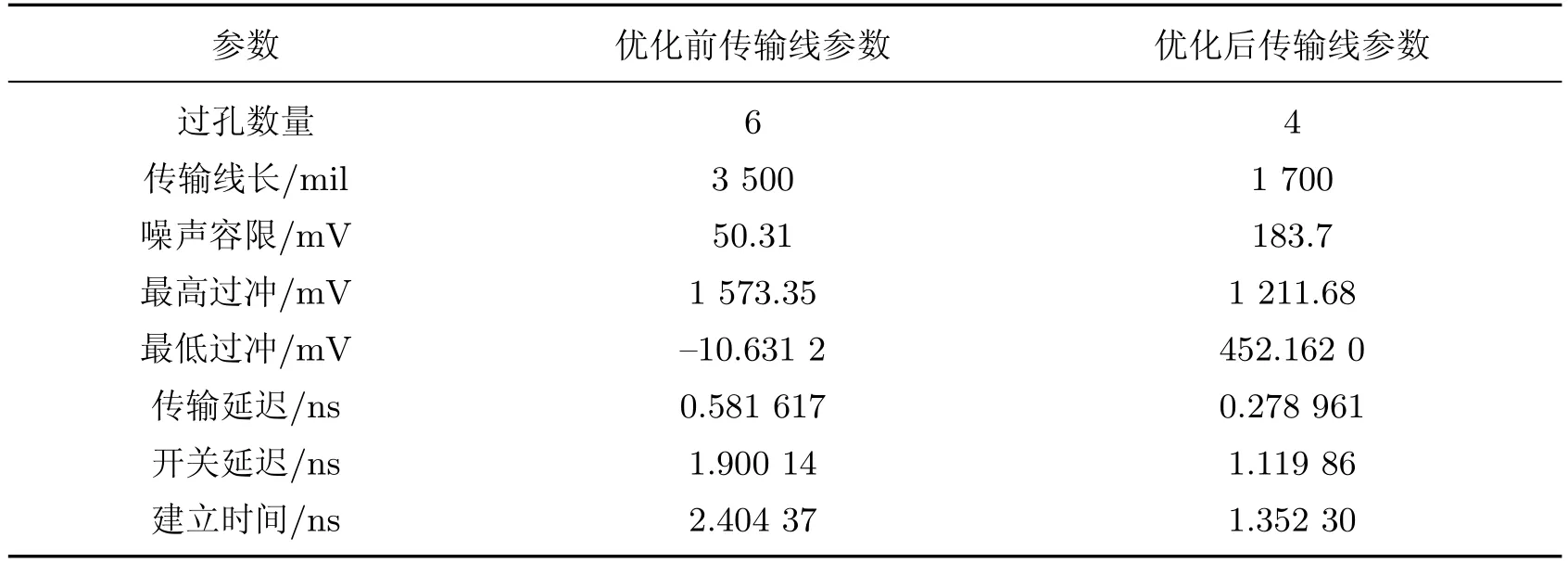

由圖11 和表4 看可見,在800 MHz 頻率下,相較于優化前的傳輸線波形,傳輸線信號質量有明顯的改善,信號振蕩明顯改善.優化后信號最高過沖電壓為1.2 V,最低過沖電壓約為0.45 V,波形信號沒有出現明顯的振蕩與過沖.優化后,信號傳輸穩定,信號邊緣明顯,從信號的上升時間、信號幅值、傳輸延遲等參數上看,優化效果非常明顯,均滿足DDR2 的設計標準[16].

圖11 傳輸線優化前后信號波形Fig.11 Signal waveforms of transmission line before and after optimization

表4 布局布線優化前后仿真參數對照Table 4 Simulation parameter comparison before and after layout and routing optimization

3 結束語

本工作針對實際應用中出現的信號反射和信號過沖現象,對原有單向傳輸線模型進行了總結與推導.通過理論推導計算最優值,對原有設計進行了優化,同時通過仿真驗證了高速單向點對點傳輸線設計中的匹配電阻值、長度、過孔數量以及布局布線中器件放置位置等設計要點,提出了一套具有復用價值的方案.本設計方案能夠有效簡化原有設計方案,提升設計性能,節約設計開支,在工業領域有著重要的應用價值.本工作所研究的高速點對點單向傳輸線理論與設計優化方案已應用于某型高速FPGA 控制器產品中.