基于CSPI傳輸協(xié)議的自適應均衡器設計

趙 斌, 張裕樺, 王 照, 徐楓程*

(1. 華南理工大學 電子與信息學院,廣東 廣州 510640;2. TCL華星光電技術有限公司,廣東 深圳 518107)

1 引 言

由于TFT-LCD顯示在尺寸、分辨率和刷新率方面的飛速發(fā)展,大量信號的快速傳輸要求使得高速串行傳輸逐漸取代傳統(tǒng)的并行傳輸。CSPI是一種點對點高串行速傳輸協(xié)議,在超高清顯示(UHD)中有著優(yōu)秀的表現(xiàn)[1]。然而隨著高分辨率(e.g. 8 K)和高刷新率(e.g. 120 Hz)面板需求的出現(xiàn),使得串行通道的數(shù)據(jù)傳輸速率急速上升。由于趨膚效應和介電損失的存在,高速數(shù)據(jù)在通過信道(e.g. FR-4)時,不可避免地出現(xiàn)幅值衰減和碼間干擾(ISI)等問題。為了解決這種與頻率強相關的信號損失問題,發(fā)送器Tx(Transmitter)使用預加重技術[2-3](Pre-emphasis)提前對可能遭受損失的頻段進行增強,接收器Rx(Receiver)使用均衡器技術[4-5](EQ)對接收信號中已損失的頻段進行補償。通常來說,二者的增益值是由人根據(jù)信號眼圖質量手動進行更改的。在TFT-LCD調試中,PVT(Process Voltage Temperature)的存在使得相同產品不同個體的最優(yōu)增益值有差別[6]。因此在大規(guī)模制造時,自適應調節(jié)將替代手動調節(jié)。

在系統(tǒng)層次,針對Rx的自適應設計方法可以被分類為兩種:前饋均衡器(FFE)和決策反饋均衡器(DFE)。FFE占用面積和能耗較小,然而由于缺少反饋,均衡器增益也將施加于噪聲,系統(tǒng)的信噪比(SNR)變差。DFE可以改善SNR問題,但操作速率被反饋環(huán)延時所限制[7]。在信號處理層次,均衡方式可以被分類為兩種:連續(xù)信號均衡和離散信號均衡。連續(xù)信號均衡的實現(xiàn)獨立于時鐘恢復機制之外,不受其影響[8]。離散信號均衡的實現(xiàn)需要恢復時鐘信號參與采樣,有高速處理能力。因采樣時鐘信號是由高速串行信號恢復所得,則由于高頻衰減問題,恢復時鐘本身的精確性難以確保,均衡器工作不穩(wěn)定[9]。本文提出把偽隨機二進制序列(PRBS)作為訓練數(shù)據(jù),使用DFE,并以離散信號均衡的方式進行自適應調整的均衡器設計。在Rx至Tx方向架設單向低速通道,在初期無法獲得較為精確的時鐘信號時告知Tx提升預加重增益,由此解決離散信號均衡方式中恢復時鐘不精確帶來的問題。

2 信道特性

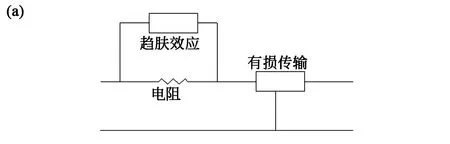

為了量化信道對信號的幅值衰減作用,必須先對信道本身的特性有所了解。圖1為傳輸模型。

圖1 (a) 傳輸模型;(b)有損傳輸模型;(c)趨膚效應模型。

在信道(e.g. RG-58,F(xiàn)R-4)上的信號損失取決于信號的頻率和信道的長度,高頻下?lián)p失函數(shù)由式(1)表示[10]:

(1)

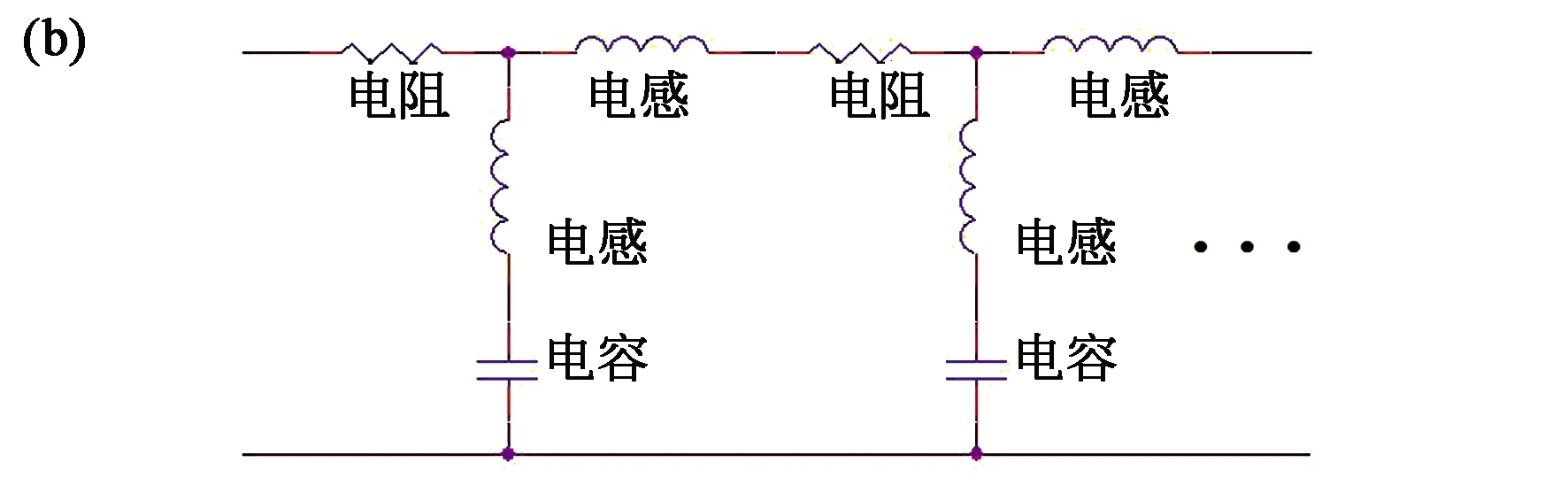

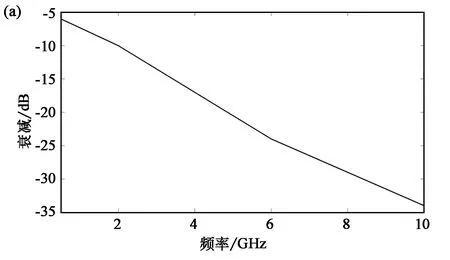

其中Loss(f)表示損失函數(shù),k表示趨膚效應系數(shù),l表示信道長度,f表示信號頻率。信號在信道長度為3 000 mil的FR-4板上的衰減如圖2(a)所示。對于工作頻率在1.5 GHz的信號,衰減為8 dB。如圖2(b)所示,此時眼圖質量差,Rx端不足以準確還原信號。

圖2 (a) 3 000 mil FR-4下的信號衰減;(b)1.5 GHz工作頻率下的眼圖。

3 自適應均衡器設計方案

3.1 自適應均衡器架構

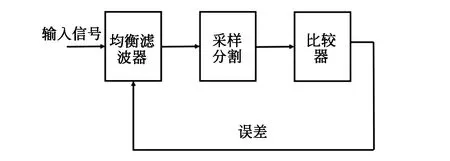

自適應均衡器的總體設計如圖3所示。均衡濾波器起到高頻增益的作用;采樣分割負責將經過增益的信號轉化為標準二進制代碼輸出[11];比較器通過比較實際輸入與理想值,計算誤差。比較器控制反饋回路更新濾波器增益。

圖3 自適應均衡器架構圖

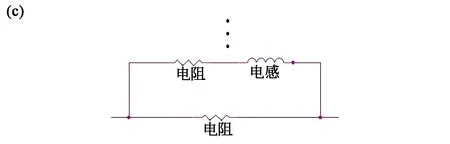

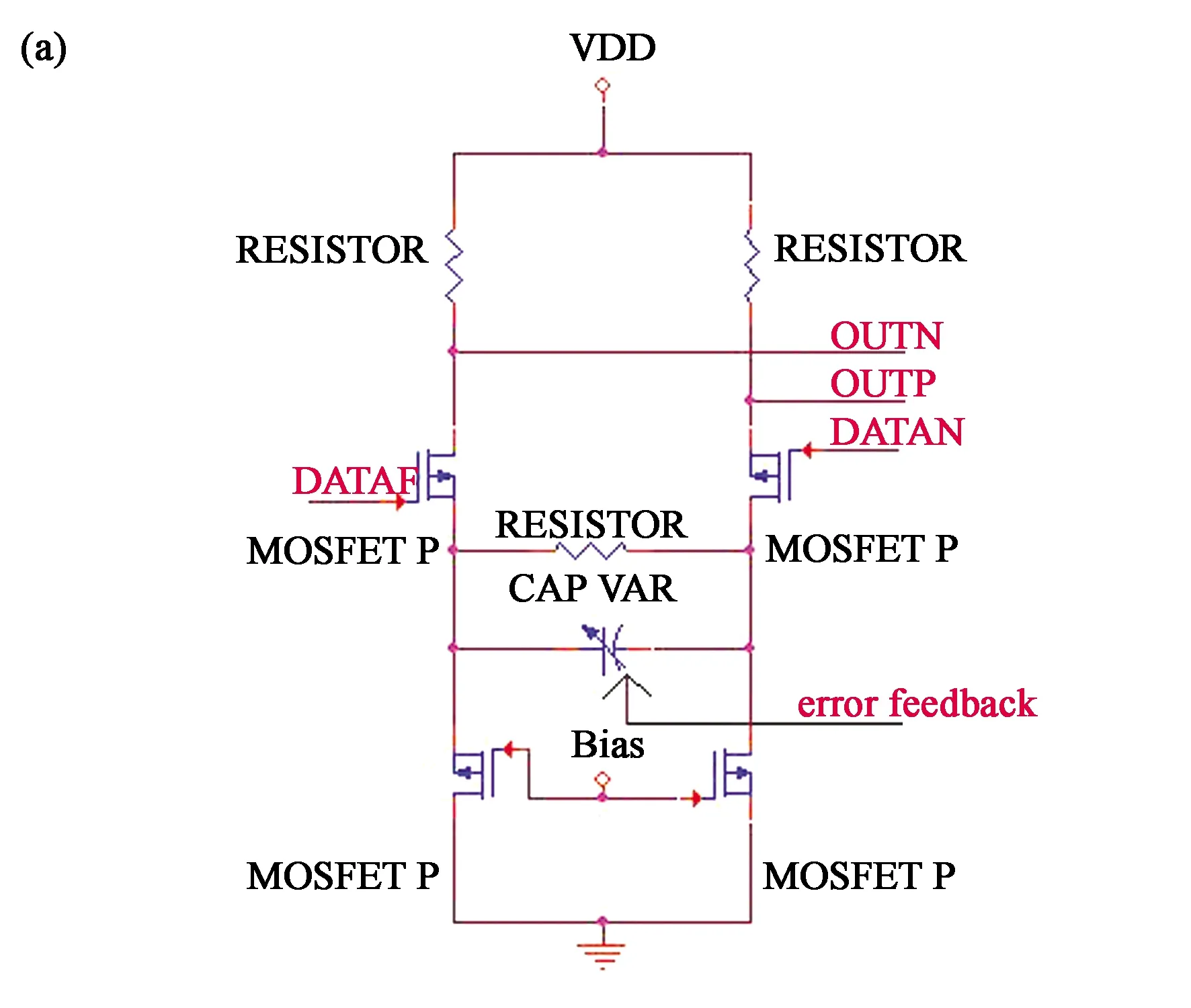

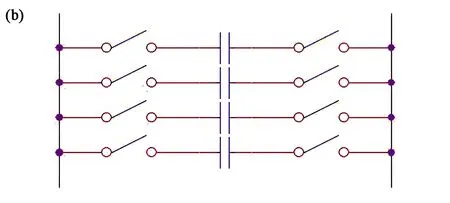

3.2 均衡濾波器

圖4(a)為均衡濾波器,為受到衰減的高頻信號提供增益。為了獲得更大的帶寬與增益,采用串聯(lián)多個均衡濾波器的做法。圖4(b)為電容陣列(即圖4(a)中的可變電容部分),根據(jù)反饋誤差轉換的檔位決定接入電路的電容值。本文采用4 bit~16檔位可選機制,每一個檔位補償1 dB增益。

圖4 (a) 均衡濾波器;(b) 電容陣列。

3.3 采樣與分割

采樣時鐘信號由Tx端鎖相環(huán)模塊產生,抵消差分信號耦合。信號眼圖的中央進行采樣,并保持采樣結果一段時間直到分割器完成工作。分割器作用與鑒幅器原理相同,使得信號具有較陡峭的上升下降沿,方便比較器獲得精確的比較結果。

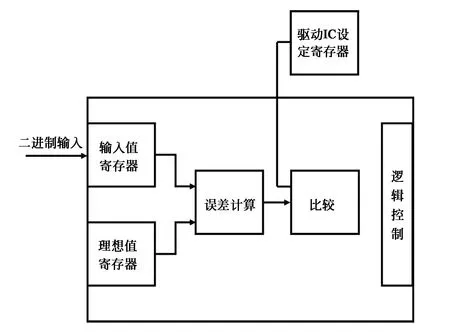

3.4 比較器

圖5 比較器框圖

比較器實際為一個數(shù)據(jù)處理單元,如圖5所示。在進行自適應調整期間,Rx接受的數(shù)據(jù)均為PRBS碼,碼型已經由生成多項式決定,因此在理想值寄存器中可存入Tx送出數(shù)據(jù)的理論值。在計算得到實際輸入與理想輸入的誤差后,比較器向驅動IC設定寄存器查詢誤差閾值。若誤差超過設定閾值,則向均衡濾波器發(fā)出增加增益檔位的需求;若沒有超過,也會發(fā)出增加檔位需求,同時將該檔位記錄為可用檔位。

4 基于CSPI的應用

4.1 系統(tǒng)結構

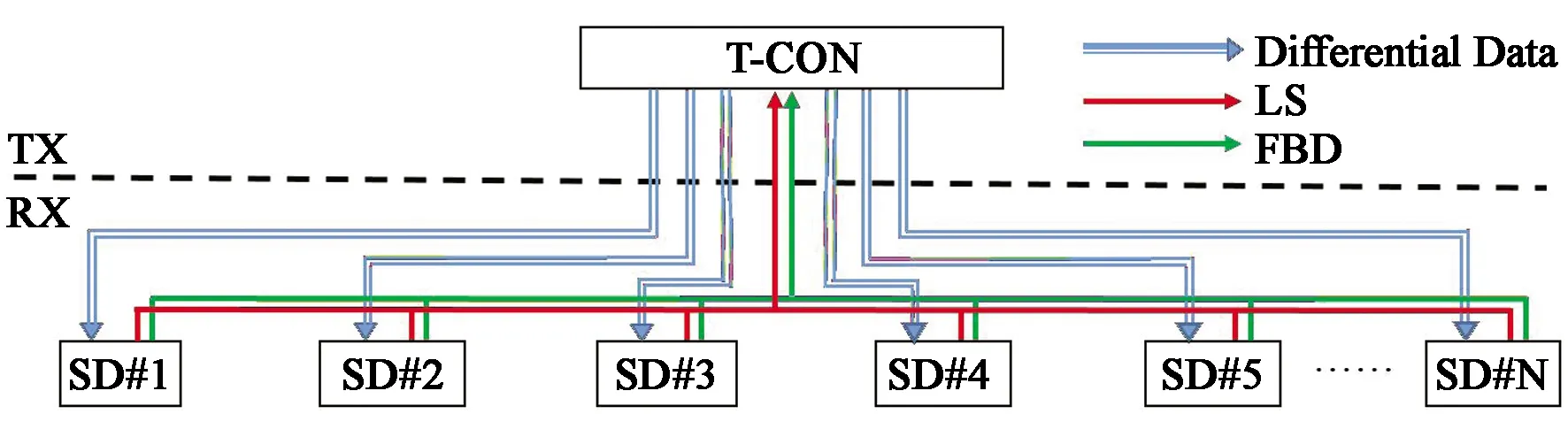

基于CSPI協(xié)議的系統(tǒng)架構圖如圖6所示,自適應設計位于源驅動芯片(Source IC)Rx端。在系統(tǒng)開機時,時序控制器(Tcon)Tx端通過差分信號線DATA P/N向Source IC傳輸訓練協(xié)議,source IC依次進行自適應調節(jié)。在調節(jié)過程中,source IC通過LS信號線與Tcon完成預加重(Pre-emphasis)和均衡器(Equalizer,EQ)的協(xié)同調節(jié),通過FBD-Link信號線告知Tcon當前EQ狀態(tài)。當所有source IC完成自適應調節(jié)后,系統(tǒng)進入正常顯示模式。

圖6 基于CSPI的系統(tǒng)架構圖

4.2 系統(tǒng)自適應調節(jié)機制

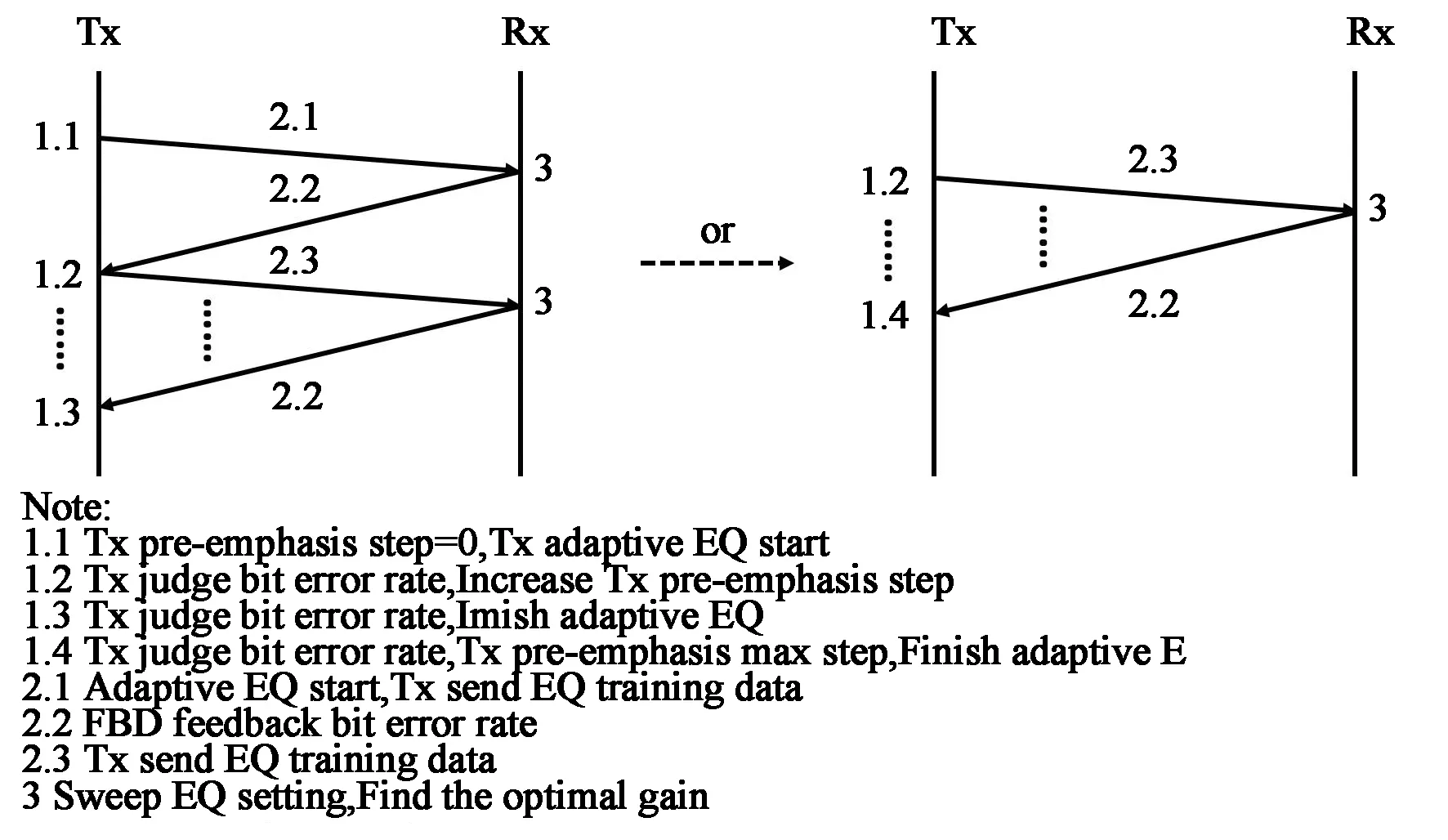

系統(tǒng)自適應調節(jié)機制如圖7所示。系統(tǒng)的自適應調節(jié)包含Tcon到source IC以及source IC到Tcon兩種數(shù)據(jù)發(fā)送機制。根據(jù)發(fā)送數(shù)據(jù)的主體,系統(tǒng)自適應調節(jié)機制又分為訓練機制和回傳機制。

圖7 系統(tǒng)自適應調節(jié)機制

4.2.1 訓練機制

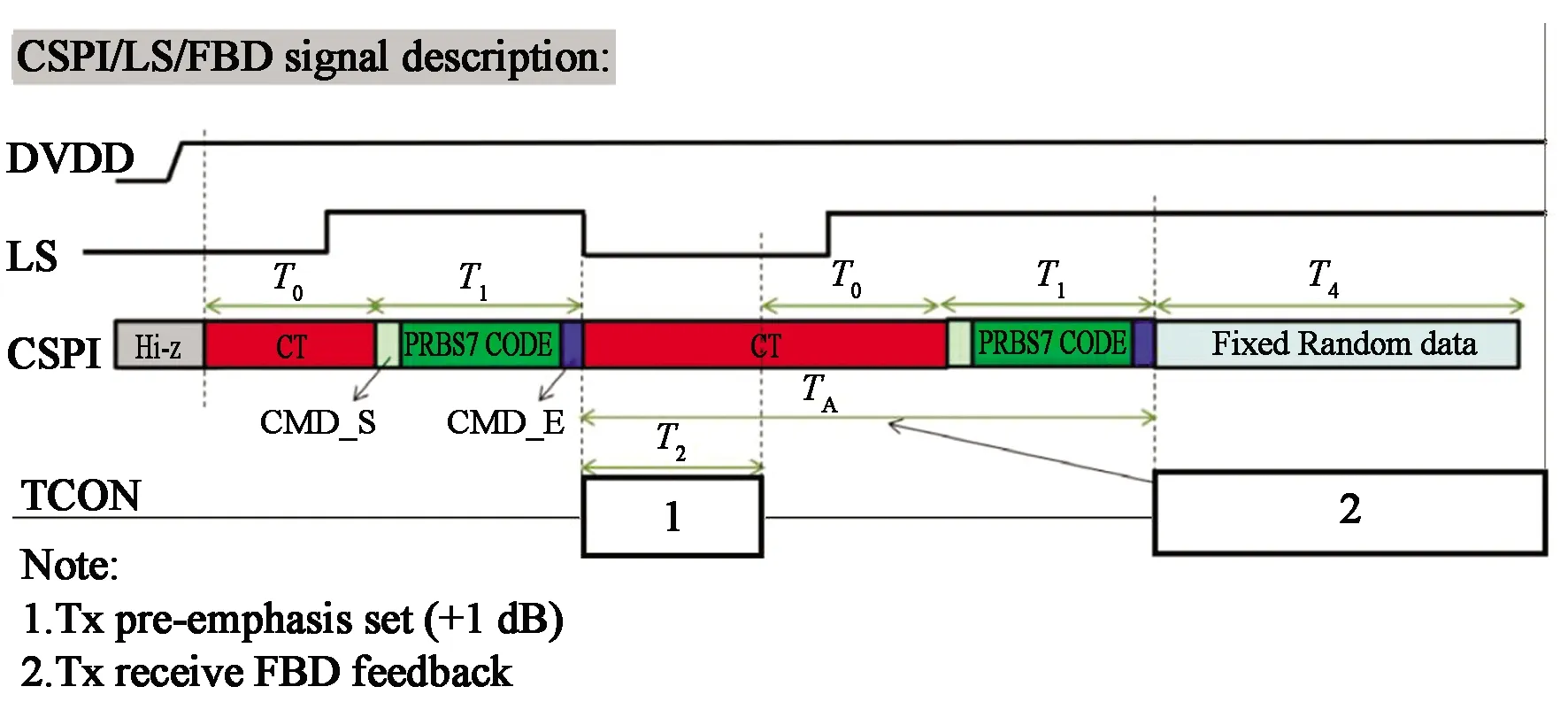

圖8是自適應調節(jié)訓練機制。開機時Tcon通過差分信號線發(fā)送CT信號給所有source IC,使其建立內部時鐘[1]。成功后,LS信號被拉至高電位,Tcon發(fā)送CMD_S信號通知source IC準備接受PRBS碼,source IC通過PRBS訓練找到最佳EQ設定。如果source IC無法找到任何最佳設定或突然受到外部干擾導致Rx接收狀態(tài)失鎖[1],則將LS拉至低電位,通知Tcon增加預加重,同時重新發(fā)送CT。source IC將重復之前步驟直到找到最佳EQ,此時source IC通過FBD-LINK告知Tcon現(xiàn)在的設置檔位。Tcon向下一顆source IC重復以上步驟。

圖8 訓練機制

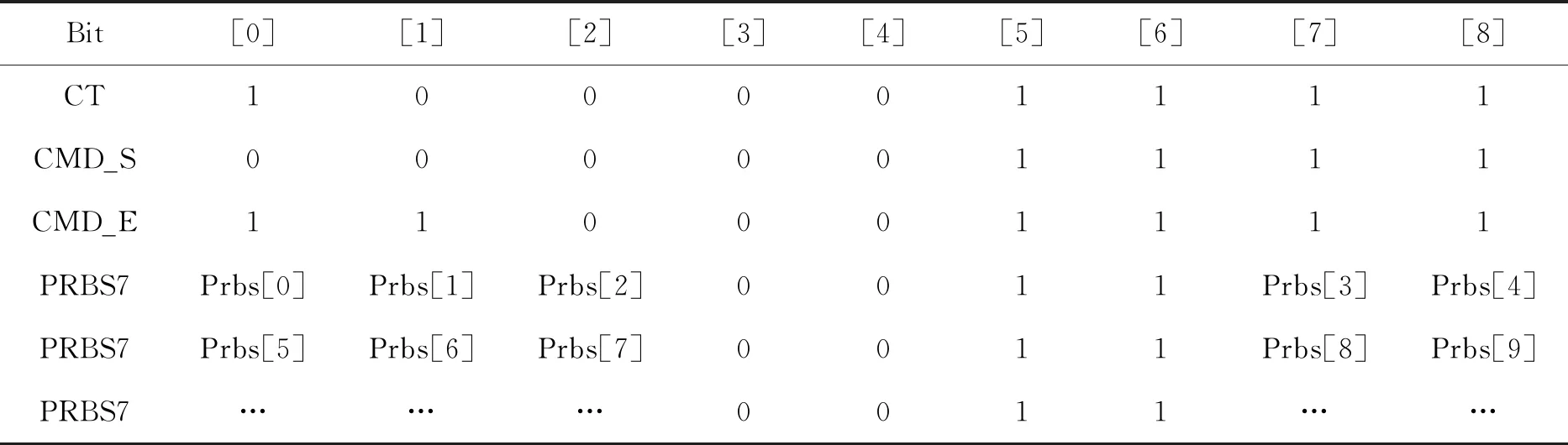

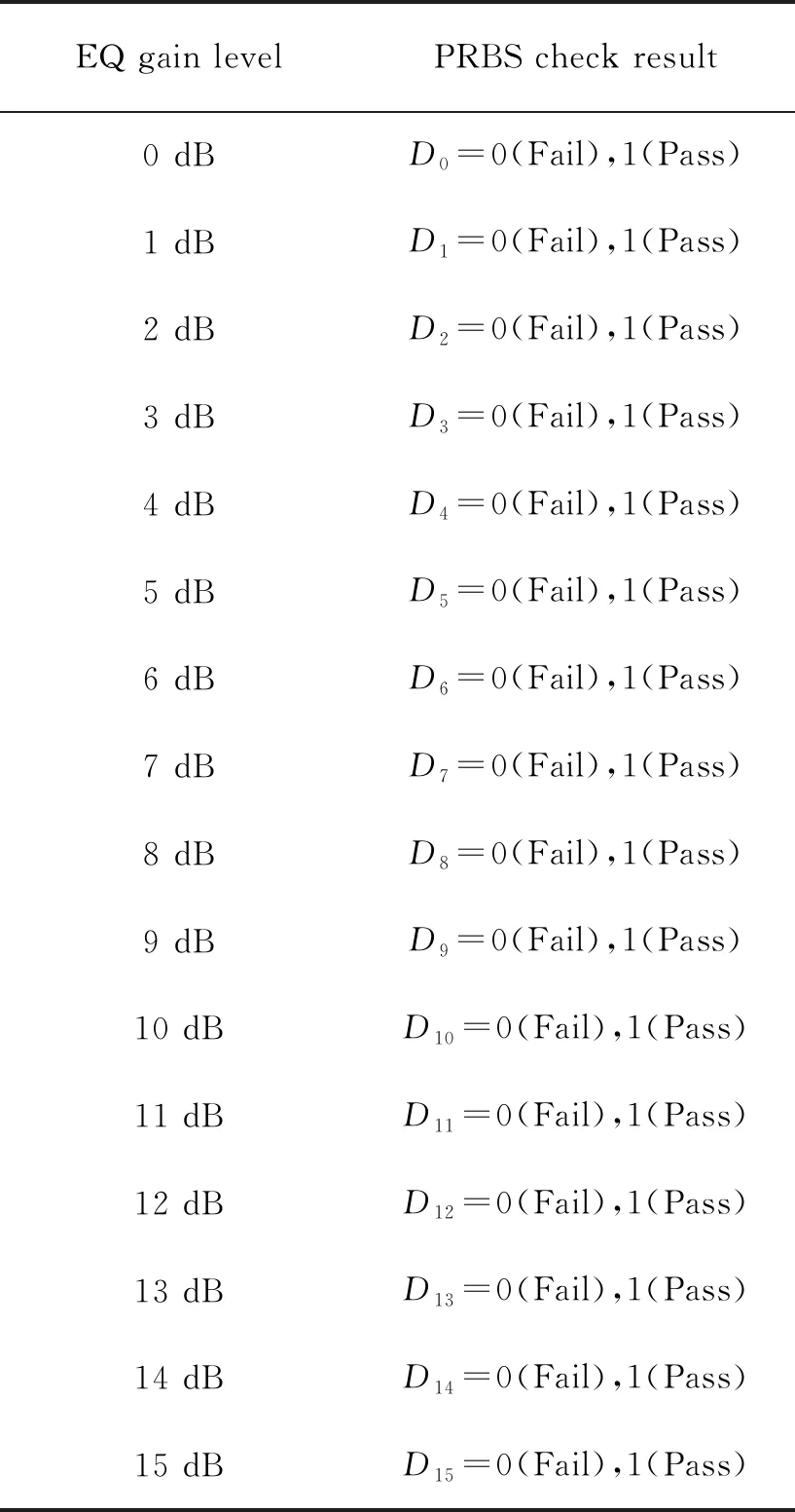

訓練碼內容如表1所示。由于LS與FBD-LINK存在多個子機復用的情況,如表2所示,對于協(xié)議中各段代碼的時間長度有最小值的要求, 這樣可以保證source IC在訓練和回傳時留有時間裕量,提高系統(tǒng)的穩(wěn)定性。其中,T2僅與Tx端相關,無最小值要求。

表1 訓練碼

表2 訓練碼最小時間要求

4.2.2 回傳機制

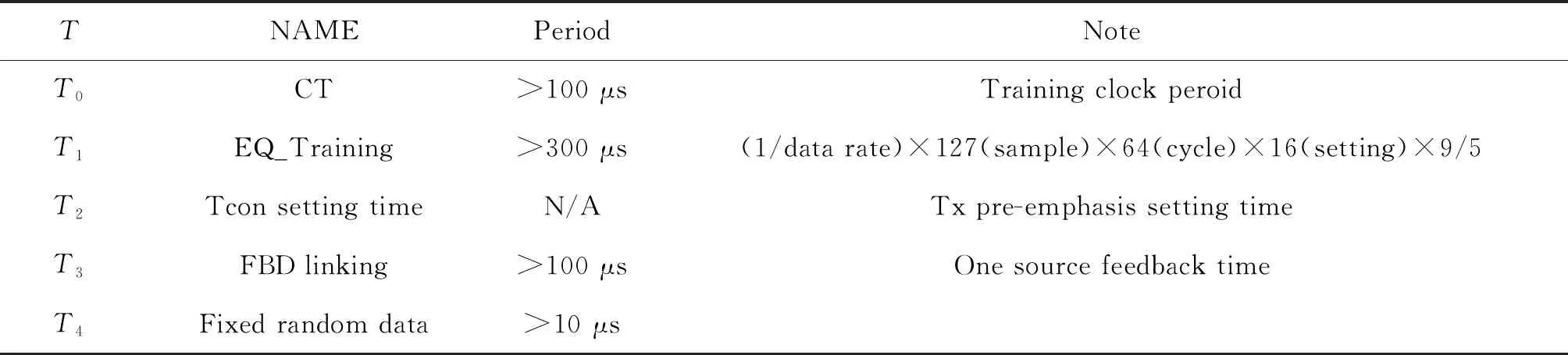

如圖9所示,source IC通過FBD-LINK信號線向Tcon回傳當前EQ設定的機制。FBD-LINK回傳協(xié)議由idle、preamble、header、data、end組成。

圖9 FBD-LINK回傳機制

表3 回傳碼

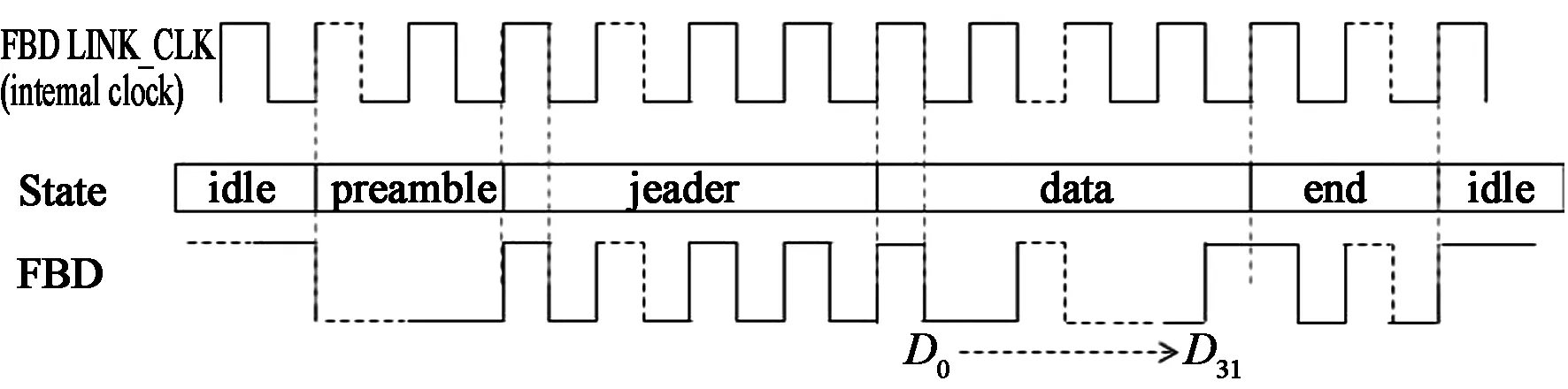

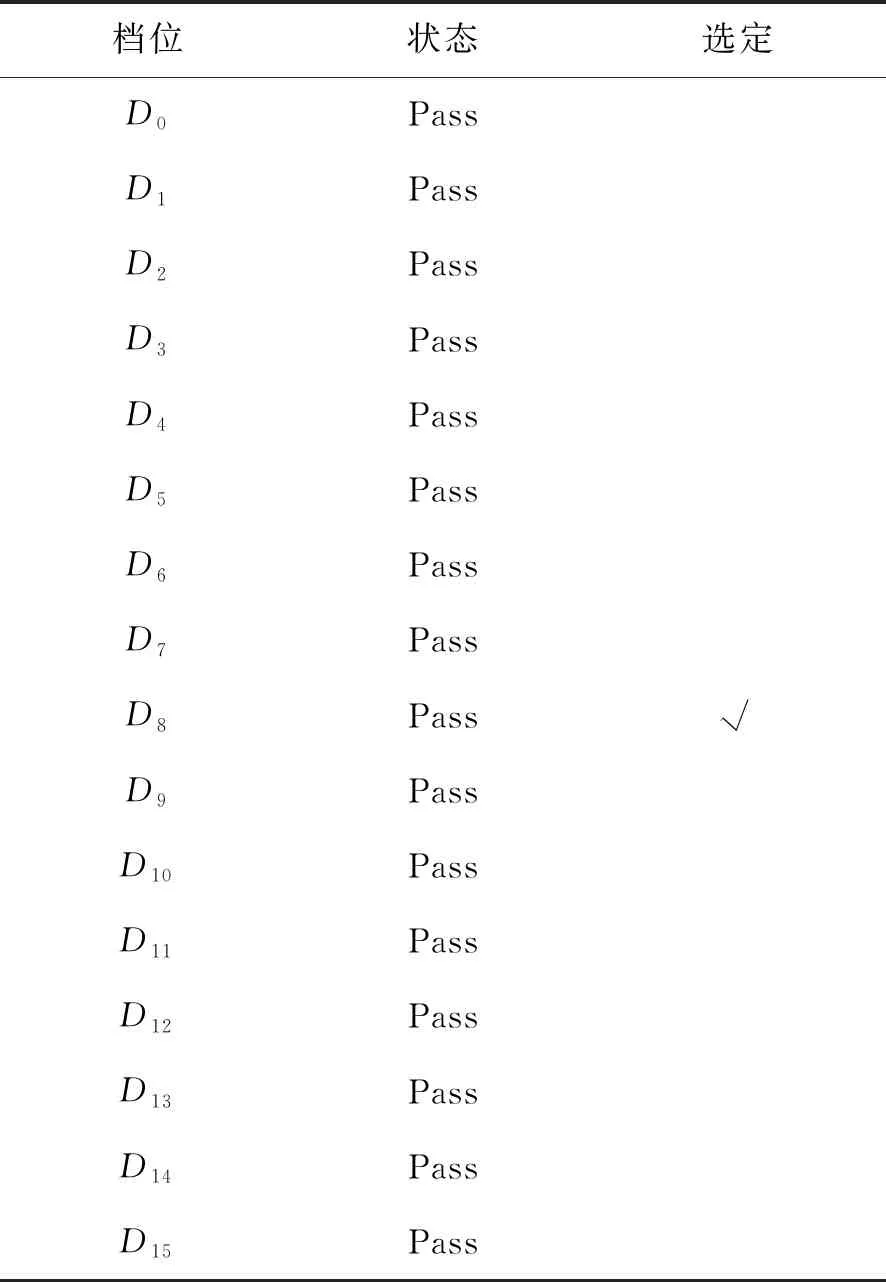

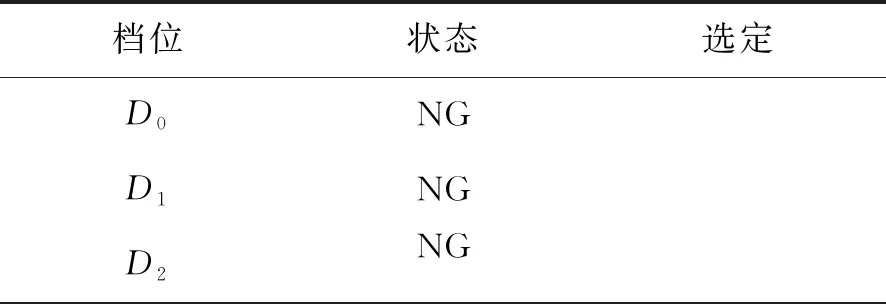

如表3所示,header、data與end采用曼徹斯特編碼方式。由于這3個部分可能存在長時間電平不跳變的情況,使用具有自定時功能的曼徹斯特編碼可以防止同步時鐘的丟失以及低頻直流漂移造成的比特錯誤。Data部分內容決定EQ設定。在32位Data中,前16位用于表示可用EQ設定,17~20位用于表示最終的EQ設定,其余位無內容,默認為0,用于滿足FBD最小時間要求。此處,我們選擇將可用EQ設定中的中位數(shù)作為最終檔位,因為增益與信號改善效應的關系可概括成二次項系數(shù)為負的二次函數(shù),通常情況下中位數(shù)檔位最接近拐點。注意,當預加重值與EQ值都為最大值仍不能滿足要求時(即無合適檔位可選),source IC將默認設置為第8檔位。此時表明僅從信號本身進行加強已無法彌補信道帶來的損耗,需要同時優(yōu)化改善信道設計。如表4所示,Data的0~15位每一位對應EQ增益的一個檔位。0為不通過(Fail),1為通過(Pass)。

表4 Data與EQ聯(lián)系

FBD-LINK有兩個作用:(1)幫助判斷自適應機制是否正常工作。在實際系統(tǒng)中,無法對IC內部的Rx端對經過AEQ后的信號進行測量。因此需要借助FBD-LINK的回傳機制來判斷系統(tǒng)設計的有效性。若Tx端接收不到回傳值或者接收到的回傳值內容不符合設計原理要求,則證明系統(tǒng)設計失效。(2)下一顆D-IC自適應調節(jié)的使能。LS為多子機復用,使用同一根LS信號線的source IC無法同時進行EQ訓練,否則存在總線競爭。因此,對于one-by-one訓練的系統(tǒng)來說,F(xiàn)BD-LINK起到告知Tx當前IC已完成訓練需要啟動下一顆IC訓練的作用。

5 實驗結果與分析

如圖10所示,分別選取信號走線最短和最長的兩端D-IC進行FBD-LINK回傳信號讀取。根據(jù)系統(tǒng)設計原理,A端信道傳輸距離最短,信號衰減低,F(xiàn)BD-LINK返回的EQ設定中,較小的檔位也能通過,通過的檔位數(shù)較多,最后在通過檔位中選取中位數(shù)作為EQ設定。B端信道傳輸距離最長,信號衰減高,F(xiàn)BD返回的EQ設定中,只有一定增益以上的檔位可以通過,通過的檔位數(shù)較少,最后在通過檔位中選取中位數(shù)作為EQ設定。

圖10 PCB板量測

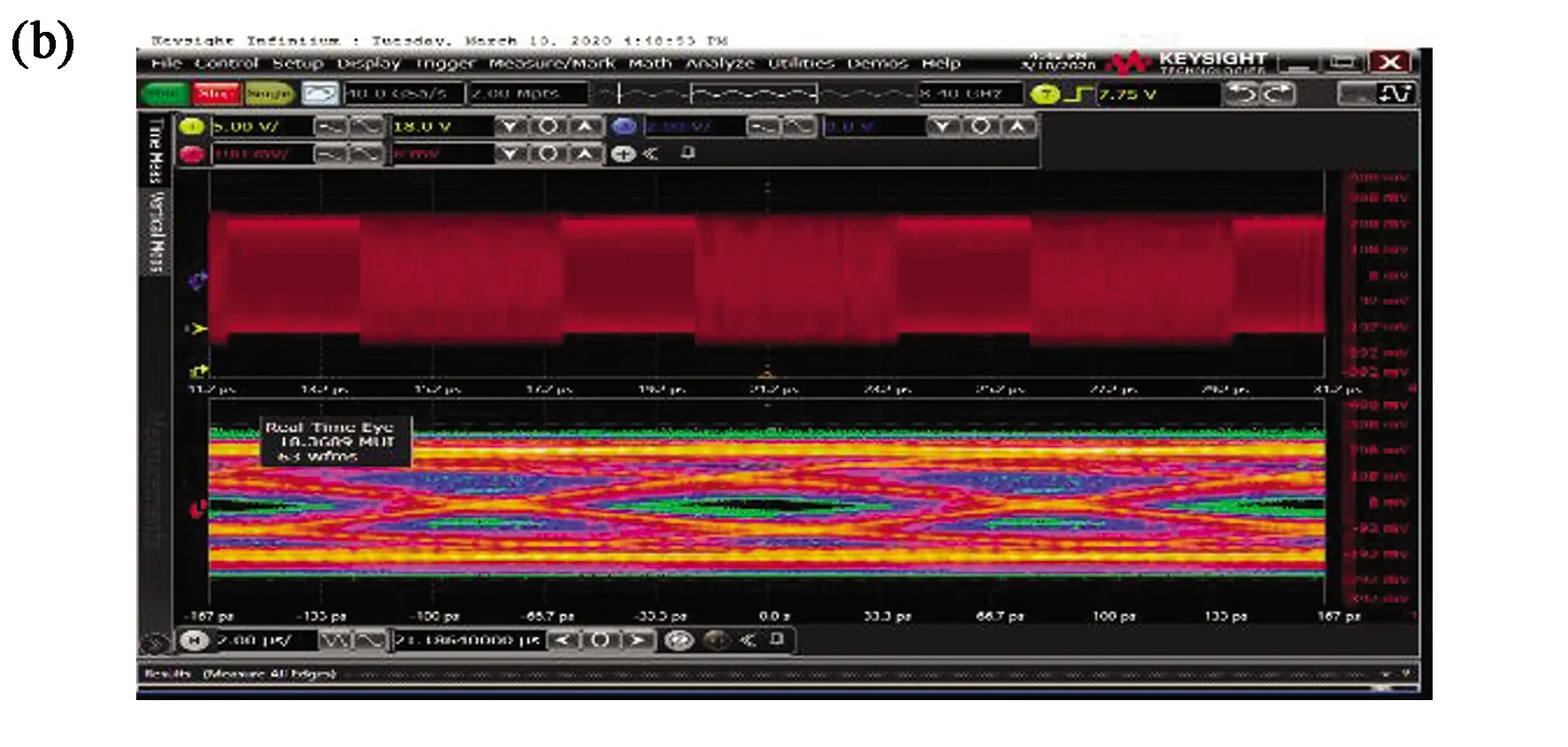

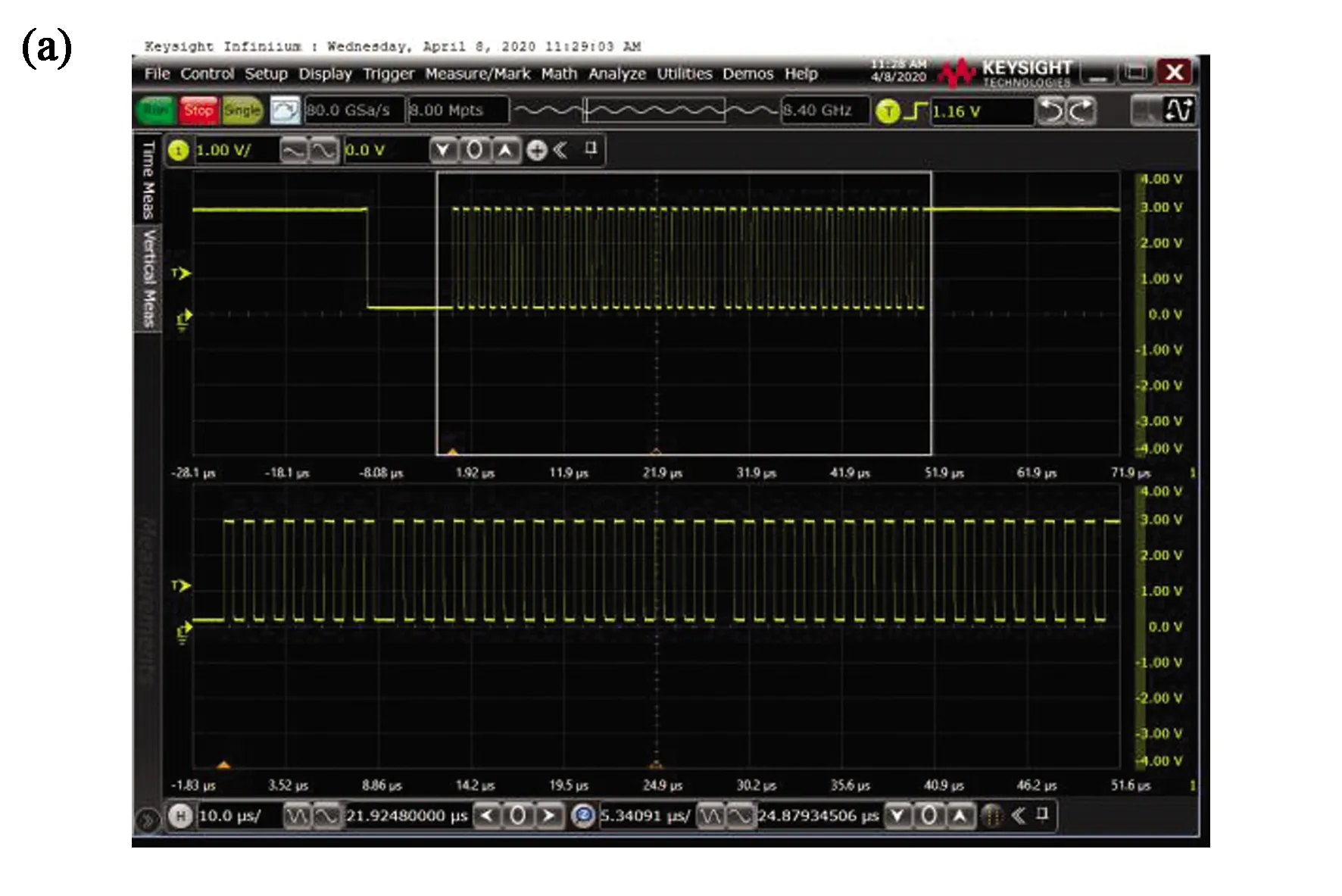

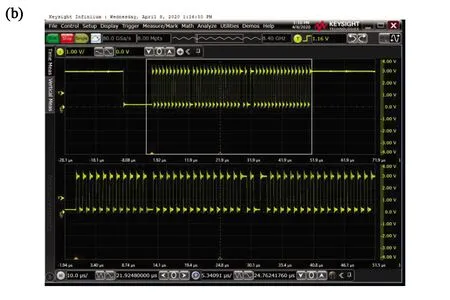

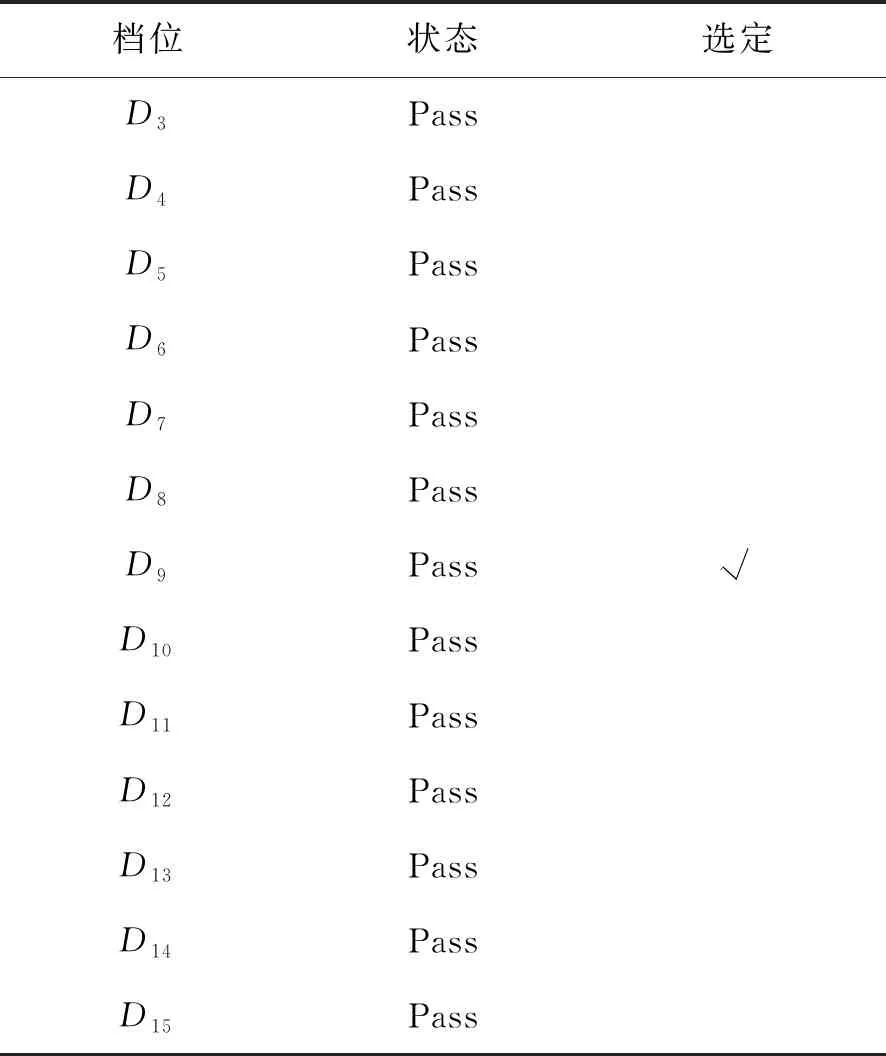

圖11(a)、(b)分別為D-IC A和B位置量測的FBD反饋信號。將其中Data的內容轉化為表5與表6。A端所有檔位通過,設定值為第9檔。B端4~16檔通過,設定為第10檔。實測檔位選擇符合設計理論,證明自適應均衡器工作正常。

圖11 (a) D-IC A FBD信號量測;(b) D-IC B FBD信號量測。

表5 A端EQ檔位狀態(tài)及選擇

表6 gB端EQ檔位狀態(tài)及選擇

續(xù) 表

6 結 論

本文提出一種基于CSPI協(xié)議的自適應均衡器設計。在Rx設計層面,DFE的引入消除了噪聲帶來的影響,離散信號處理的均衡方式改善了反饋引入后的延時效應。在系統(tǒng)層面,加入FBD-LINK機制以解決對信號采樣時采樣時鐘精確性的問題。最后在實驗中通過檢查Tx端的回讀值證明了系統(tǒng)的有效性。該設計補償了高頻信號的衰減,對于Rx端準確恢復高速信號有重要意義。