解鎖下一代制程工藝的鑰匙

晶體管數量和摩爾定律

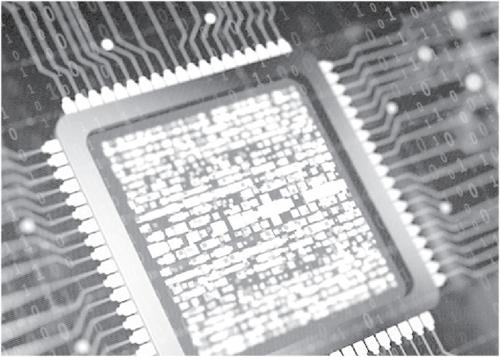

我們都知道,一顆芯片的性能強弱,以及整合功能的多寡,在很大程度上就取決于單位面積內的晶體管數量。晶體管數量越多,往往就意味著更強的性能和更豐富的功能。以麒麟9000為例(圖1),這顆5GSoC在臺積電5nm制程工藝的幫助下,在指甲蓋大小的芯片面積里就塞進了高達153億個晶體管。

換句話說,如果一顆S oC(包含其他領域的半導體芯片)可以在相同面積里塞進200億甚至更多的晶體管,其性能自然可以更近一步,而這也恰好印證了摩爾定律的描述——“當價格不變時,集成電路上可容納的元器件的數目,約每隔18 個~24個月便會增加一倍,性能也將提升一倍”。

然而,就好像我們往氣球里注水,一旦超過某個閾值,等待它的就只有被撐爆的命運。一顆芯片的單位面積上可以容納多少數量的晶體管,自然也存在一個閾值上限,而影響這一指標的關鍵因素就是制程工藝,以及其背后的晶體管技術(圖2)。每當摩爾定律遭遇困境,總會有新的技術及時救場。10年以前,FinFET拯救了一次摩爾定律,而摩爾定律能否繼續前行就得看GAA FET的實際表現了。

芯片廠商的分類

在進行具體討論之前,我們需要了解當前芯片廠商的分類。根據廠商的定位和性質,它們大致可以分為Fabless(無廠半導體公司)、Foundry(代工廠)和IDM(集成器件制造商)三大類。

晶體管技術的迭代歷史

我們可以將晶體管理解為一種類似于“水龍頭”的電子器件,主要用于控制電流(水流)的大小以及開關。由于晶體管對電流的控制是通過對柵極施加一個電壓,從而在通道內部產生一個電場,用來調節源極和漏記之間電流的大小,所以它的全稱是“場效應晶體管”(即FET,Field Ef fectTransistor)。

判定一個水龍頭優劣的重要指標就是對水流的管控能力,決定FET場效應晶體管(下文簡稱晶體管)效率的重要因素同樣是柵極對通道的控制能力。

平面型晶體管的物理瓶頸

在過去的很長一段時間里都是平面型晶體管的天下,它在通電后,電流會從Source(源極)流入Drain(漏級),而Gate(柵極)就相當于閘門(圖6),主要負責控制兩端源極和漏級的通與斷。在電流通過柵極時會出現耗損,表現形式為更高的發熱和功耗,而耗損的程度則取決于柵極的寬度,柵極越窄,功耗越低,柵極越寬功耗越高。

一般來說,晶體管柵極的最小寬度(柵長),就是我們念叨的XXnm工藝中的數值。比如28nm,就代表管的柵長就是28,每一次制程工藝的迭代,本質上就是不斷降低晶體管柵極寬度的過程。

問題來了,平面型晶體管受制于物理結構,它只能在閘門的一側控制電流的接通與斷開,而且它的柵極寬度不可能無限制的縮窄,當寬度接近20nm時,柵極對電流的控制能力將出現斷崖式下降,業內將其稱為“溝道長度變短導致的所謂短溝道效應”,從而出現嚴重的電流泄露(漏電)現象,最終讓芯片的發熱和耗電失控。

鰭式場效應晶體管參與救場

為了解決平面型晶體管柵極寬度的物理瓶頸,一種名為FinFET(Fin Field-Ef fectTransistor)的鰭式場效應晶體管技術參與救場。

顧名思義,FinFET最大的特色就是將晶體管的結構從平面變立體,對柵極形狀進行改制,閘門被設計成類似魚鰭的叉狀3D架構,位于電路的兩側控制電流的接通與斷開,大幅度提升了源極和柵極的接觸面積,減少柵極寬度的同時降低漏電率,讓晶體管空間利用率大大增加(圖7)。同時,由于FinFET的源極和漏極是在柵極做好之后直接在鰭上外延生長(Source-Drain Epitaxy),在柵極的阻斷下不會出現擴散層,因此不會再出現平面型晶體管要命的短溝效應問題。

問題又來了,當制程工藝跨過5nm門檻后將會出現一系列新的問題。比如,隨著柵極寬度的進一步縮小,很難再像過去那樣在一個單元內填充多個鰭線,而鰭式場效應晶體管的靜電問題也會嚴重制約晶體管性能的進一步提升。換句話說,FinFET在5nm時代就已逼近極限,想生產更具能效比的3nm和2nm工藝,需要下一代晶體管技術救場。

全柵場效應晶體管迎戰未來

FinFET的接班人,是一種名為“GAAFET”(Gate-All-AroundField-EffectTransistor)的晶體管技術,它有2個中文譯名,分別為“全環繞柵極晶體管”和“全柵場效應晶體管”,本文我們采用第2個譯名。

需要指出的是,在即將到來的3 nm工藝時代,GAA FET還不是剛需,因為臺積電曾表示過旗下的3 n m制程技術將沿用FinFET的擴展和改進版本,較之現有的5nm(N5)性能可提高50%,功耗降低30%,晶體管密度提高1.7倍。當然,我們也不排除臺積電未來會推出改用GA A FET技術的3nm+工藝。但是,當制程工藝進入2 n m時代后,Fi n FE T 就必須告別歷史舞臺了,而晶體管技術也將進入GAA FET的天下。

全環繞柵極晶體管是一種比FinFET更復雜的晶體管結構(圖8),它的柵極可從各個側面接觸溝道并實現進一步微縮,就靜電學而言它被認為是一種“終極CMOS器件”,其閾值電壓可以低至0.3V,3nmGA A FET較之3nm FinFET能以更低的待機功耗實現更好的開關效果(圖9)。

GA A FET全環繞柵極晶體管根據源極與漏極之間通道的長寬比不同,分為納米線結構以及納米片結構兩種(圖10),后者使用更寬和更厚的片來改進靜電特性和驅動電流。三星即將量產的3nmGA A就將采用納米片結構,而官方對外宣稱的技術英文名為Multi-Bridge Channel FET(MBCFET,多橋通道場效晶體管),有消息稱臺積電未來的2nm GA A也會采用這種納米片的結構。

換句話說,都是3nm GAAF E T,在不同的納米線/片結構,以及鰭的數量、間距、溝道等因素的影響下可能會拉開較大的性能差距。這就好像英特爾10nm FinFET工藝無論是晶體管密度還是電氣性能都遠超三星/ 臺積電10 n m 一樣,一顆處理器芯片只有挑選同期最好的GA A FET工藝,才能獲得更出色的性能底蘊。

更復雜的制造難度

雖然GA A FET取代FinFET已成業內共識,但現階段影響其量產普及的因素還有不少,其中最關鍵的就是更復雜的制造流程,良品率和成本難以控制。在晶圓的生產過程中,蝕刻垂直側壁上的器件最是困難,需要引入更新的半導體材料,使用EUV進行多次蝕刻,還需解決可能出現的隱藏缺陷,比如納米片之間的殘留物、納米片的損壞或納米片本身相鄰的源→漏極區的選擇性損壞、溝道釋放需要單獨控制片材高度、拐角侵蝕和溝道彎曲等(圖11)。

小結

總之,GAA FET將成為延續摩爾定律的一副良藥,雖然它現階段還面臨諸多問題,但趨勢終歸是不可逆的。在不遠的將來,我們將看到三星和臺積電在GA A FET晶體管技術上的搏殺,而英特爾參與到這場戰爭的時間節點就要晚一些了。當然,我們更期待的,則是中芯國際可以早日搞定EUV光刻機和GAA FET相關技術,在高端代工市場分得一杯羹。