基于FPGA 的圖像邊緣保護高斯濾波算法實現

康 宇,趙冬青,上官鵬,儲成群

(1.中北大學電子測試技術國家重點實驗室,山西太原 030051;2.北京控制與電子技術研究所,北京 100032)

在圖像的生成與傳輸過程中,由于圖像生成的工作環境、傳感器材質、電子元器件特性、以及電路架構等各種原因,極易引入各種各樣的噪聲[1]。噪聲降低了獲取圖像的質量,極大地增加了圖像識別的難度,于是解決圖像噪聲成為了圖像處理的一大要務。其中,高斯噪聲由于其產生的普遍性成為圖像處理必須解決的問題。高斯噪聲屬于高頻噪聲,噪點在圖中表現為與周邊像素點梯度大的特性,這一特性雖然為濾除高斯噪聲提供了便利,但由于圖像的邊緣點一樣擁有該特性,僅僅通過梯度很難區分噪點與邊緣點。濾除與周邊像素點梯度大的像素點,將同時濾除圖像邊緣點,造成圖像邊緣的平滑,使得圖像邊緣特征信息缺失,降低了圖像在識別過程中的識別率。基于中值濾波與均值濾波對高斯噪聲不敏感的特性,針對高斯噪聲一般的處理方法,仍使用高斯濾波[2]。

隨著集成工藝的不斷進步,FPGA 器件也在不斷發展,其可配置、功耗低、易于實現流水和并行結構的特點,提高了圖像處理速度,能夠滿足現代圖像處理對高可靠性與實時性的要求[3-4]。由于高斯濾波最佳平滑系數的確定因圖而異,很難有定論,目前自適應確定平滑系數的算法復雜度較高,很難在FPGA上實現實時圖像處理,造成目前FPGA 實現的高斯濾波算法有局部或整體性的過度平滑問題,導致圖像邊緣信息缺失,造成圖像邊緣模糊。

通過結合高斯濾波與動態閾值計算,劃分圖像邊緣與離散噪點,以避開對平滑系數的計算,減少了計算量的同時也使圖像的邊緣信息得以保護,從而在FPGA 運算的實時性前提下提高圖像濾波效果。

1 高斯濾波器及其改進方法的算法原理與仿真

1.1 高斯濾波器的算法原理

高斯濾波本質上是一種通過正態分布確定權重的低通線性平滑濾波器,相比其他線性濾波器,如均值濾波器、中值濾波器,高斯濾波器的權重由空間距離因子控制[5],在窗口中,距離待處理像素點越遠的像素點權重越低,距離待處理像素點越近的則權重越高,對待處理像素點的影響力就越大,傳統高斯濾波的數學表達式如下式所示[6]:

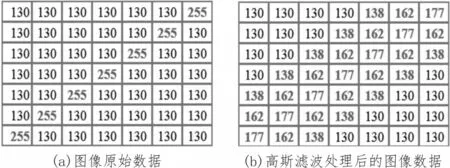

由于高斯濾波在考慮圖像空間因子的同時沒有考慮圖像的梯度因素,這導致高斯濾波作為低通濾波器將濾除圖像的高頻信息,如圖1 所示,在傳統高斯濾波中,圖(a)邊緣細線將被當做噪聲進行高斯濾波處理,大大降低了邊緣與周邊像素點的區分度,從而模糊了圖像的邊緣信息。檢測并保護圖像的高頻信息將獲得相比傳統高斯濾波更完整的邊緣信息。

1.2 改進高斯濾波器的算法原理與仿真

圖1 高斯濾波圖像邊緣數據對比圖

基于上文所述,高斯濾波本質上屬于基于圖像空間因子的平滑濾波,如引入傳統高斯濾波缺失的梯度因子,就將大幅度改善傳統高斯濾波破壞圖像邊緣信息的問題[7],在一副圖像中,除圖像最外側像素點外,任何一個像素點都擁有8 個梯度值與4 個梯度方向,梯度求取原理圖如圖2 所示。

圖2 四方向八梯求取示意圖

如圖2 所示,八方向梯度計算方法為:

如圖2 所示,求取平均梯度共需要4 個方向的8 個梯度值,其中平均梯度的求取方法如下:

根據式(5)即可求取3×3 掩模的平均梯度,其中∑I指八方向梯度總和。求取3×3 掩模的平均梯度,通過和最終求得的閾值比較,判斷該點是否為噪點,求取梯度閾值必須先求取整幅圖像模板的梯度均值與像素點梯度均值的方差,而整幅圖像模板的梯度均值與像素點梯度均值方差的求取方法則如下式所示:

其中,P代表整個圖像梯度的均值,M×N代表整幅圖像的像素數,σ代表像素點梯度與圖像全局平均梯度之間的方差。在圖像數據中,70%的像素點梯度均值數據在(P-σ,P+σ) 之間,僅0.3%的數據在(P-3σ,P+3σ)之外,可以認為(P-2σ,P+2σ)之內的數據為圖像邊緣點,大于(P-3σ,P+3σ) 的數據皆為噪聲,對該點進行高斯權重濾波,通過以上運算,即可通過梯度閾值的方法判斷噪點,從而形成對圖像邊緣保護的功用,以及精準去噪的功能[8]。

2 改進高斯濾波器的仿真測試與結論

2.1 圖像的客觀評價參數

圖像的客觀評價方法可分為全參考圖像質量評價方法、半參考圖像質量評價方法和無參考圖像質量評價方法,全參考圖像質量評價方法是目前使用最為廣泛,最為成熟的評價方法。因此采用全參考圖像質量評價方法進行圖像質量評價,通過均方誤差(MSE)與峰值信噪比(PSNR)評價方法,分別從圖像與原始圖像的近似程度與信息和噪聲的最大功率比值兩個方面入手,盡可能多角度、客觀地評價圖像質量[9]。

2.2 基于改進高斯濾波器的仿真結果

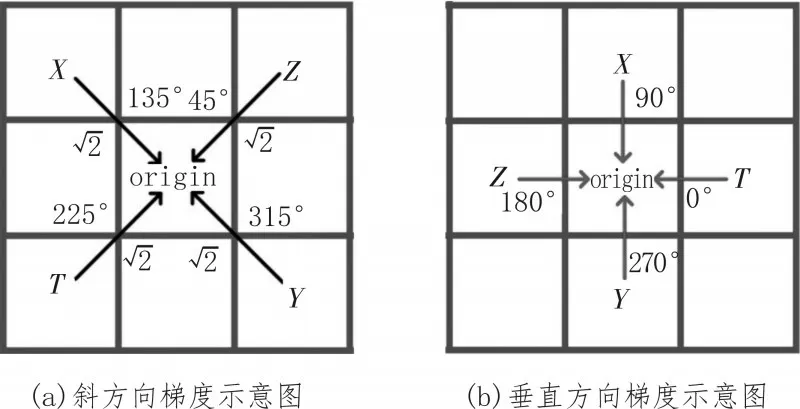

通過Matlab 仿真可得傳統高斯濾波與改進高斯濾波效果圖。如圖3、4 所示,主觀上相比傳統高斯濾波,改進高斯濾波器得到的圖像明顯擁有更好的邊緣特征與細節,而傳統高斯濾波在濾波過程中明顯造成了圖像邊緣的模糊現象。

圖3 原圖下的濾波效果對比圖

圖4 30%高斯噪聲下的濾波效果對比圖

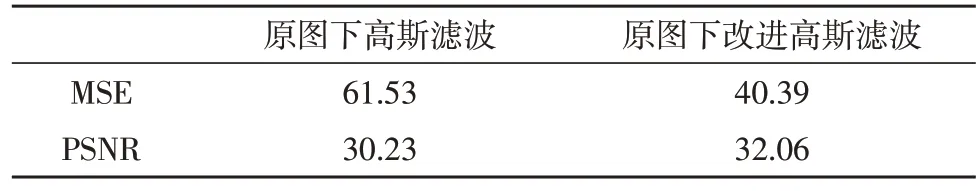

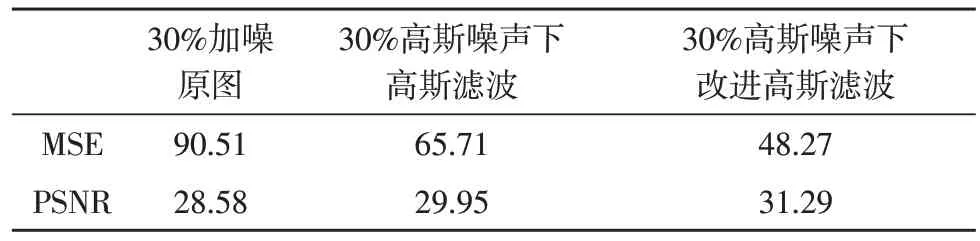

客觀評價體系下,通過對比由改進高斯濾波算法得到的圖像與常規高斯濾波算法得到的處理圖像,如表1、表2 所示,在原圖與添加30%高斯噪聲的環境下,MSE 分別減少34%、26%,PSNR 分別提升6%、4%,所得數據對比如表2 所示。

表1 原圖下圖像客觀評價數據對比表

表2 30%高斯噪聲下圖像客觀評價數據對比表

3 改進高斯濾波器的FPGA實現

3.1 改進高斯濾波算法的RTL級電路圖

由于實現的圖像采集是實時性的,所以對圖像處理有對實時性的要求。圖5 為該改進高斯濾波器的rtl級視圖,為保證實時性,流水線處理是高速設計中比較常見的設計步驟,且整個數據流的數據處理是單向操作[10],若將上述算法變為順序執行,就將以如下流程進行:①cmos 傳感器壞點矯正;②圖像的高斯濾波模板創建;③利用3×3 模板求取模板梯度均值;④通過各模板梯度均值求取方差并求得閾值;⑤按與閾值的比較結果套用高斯模板權值輸出或者不進行處理;⑥將輸出數據輸出至緩沖區,整合成為新的圖片。其中閾值求取模塊共需要使用4個乘法器與一個開平方ip 核。

3.2 前置壞點矯正模塊

CCD/CMOS 圖像傳感器上的像素點存在問題、缺陷,在視頻監控畫面上呈現為黑色或者白色,稱為壞點[11]。由上文可知,噪點檢測算法是基于壞點校正后實現的,如不預先進行壞點檢測,壞點對周邊像素點的高梯度將大幅度影響全局梯度閾值的選取,降低檢測準確率,造成大面積噪點誤判,從而降低對邊緣信息的保護效果。

3.3 像素矩陣的行緩存與濾波掩模生成方法

如圖6 所示,第一行為傳感器發送而來的串行數據,而第二行與第三行皆為移位寄存器,移位寄存器大小視圖像傳感器行周期而定,當數據進入移位寄存器的同時也進行取數,于是當第三行數據開始進入第一個移位寄存器的時候,便出現了1.1、2.1、3.1像素點同時輸出的情況,實現了生成模板的功能[12-13]。

圖5 改進高斯濾波算法RTL級電路圖

圖6 掩模的FPGA設計原理圖

如圖7 所示,通過9 個寄存器存儲兩個移位寄存器的輸出與串行輸入值,則第三行第三個像素點像素值輸入時將得到第一個3×3 矩陣。當第三行第四個數據輸入時,第二列寄存器將賦值給第三列寄存器,隨后第一列賦值給第二列,第三列存入圖中最左側的第一排,隨后將重復如上步驟,直到最后一個像素點輸出完畢為止[14]。

圖7 3×3寄存器取數示意圖

3.4 梯度閾值求取的FPGA實現

FPGA 實現梯度閾值的求取總共需要求取兩個值,一個是圖像整體的梯度幅度均值,一個是當前圖像像素點對全局梯度均值的方差。求取圖像整體平均值,要先記錄第一個壓入移位寄存器的像素值為初始值,隨后三排輸出的第一個像素點與初始值做差,并將所有差值的和存儲于一個寄存器,最后將該寄存器中的差值和求取平均值,再與初始值相加,即可獲得圖像的整體平均像素值,將整體平均像素值帶入到第二幅圖像的計算中即可用于求取圖像的方差[15]。方差的基本求取方法如式(5)所示。求取開根號值的方法選用xilinx公司的square_root ip核進行處理。

3.5 掩模濾波的FPGA實現

通過對梯度閾值的比較,得出該像素點為噪點,則通過高斯權重濾波的方式進行處理,如圖8 所示。

圖8 高斯濾波權值模板

通過對高斯濾波公式的分析,可以用近似的權值表示空間因子對像素點的影響權重,FPGA 實現高斯濾波權值模板的公式如下[16]:

式(8)的分子中每一變量代表在3×3 模板中像素點像素與該點權重的乘積,通過如上運算即可得到模板的最終高斯濾波結果。

3.6 FPGA實現改進高斯濾波的資源占用情況

如表3 所示,此方案的FPGA 占用資源較少,擁有較大的改進與升級空間,滿足了設計初衷,實現了改進高斯濾波的FPGA 實現。

表3 改進FPGA高斯濾波算法資源占用情況表

4 實驗結果

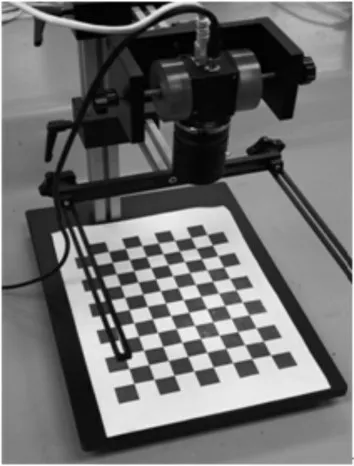

該測試系統主要由賽靈思公司的6 系FPGA XC6SLX45-CSG324 驅動CMOS 傳感器進行圖像的采集與處理工作,系統通過FPGA 產生的驅動信號驅動CMOS 傳感器采集圖像,通過圖像處理模塊處理后,根據PIXCLK(像素時鐘)、FRAMEVALID(幀有效信號)、LINEVALID(行有效信號)傳輸給上位機軟件成像,還原出處理后的圖像信息,實際測試平臺如圖9 所示。

圖9 測試平臺搭建圖

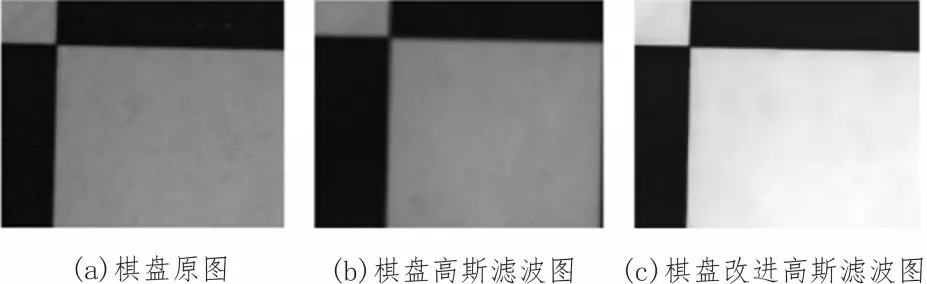

取圖像原圖,如圖10 所示,放大后與采集到的改進高斯濾波處理過的一幀圖像以及常規FPGA 處理的圖像對比。

圖10 未經處理的圖像原圖

圖11 測試結果對比圖

如圖11 所示,可見實際測試結果基本符合仿真結果,圖像邊緣相比常規FPGA 高斯濾波得到的圖像得到了保護,且完成了圖像實時性處理輸出的目標。

5 結論

該文實現了一種基于FPGA 的改進型高斯濾波器,該算法于上位機需較長的實現時間,要求主機有較強的運算能力。采用FPGA 實現該算法,大大提升了該算法的運行速率,保證了FPGA 實時圖像處理能力,并將梯度因素引入到高斯濾波中來,成功經過圖像處理實時輸出了視頻流。

且經過對比發現,基于FPGA 的改進高斯濾波算法得到的濾波后圖像相比傳統FPGA 高斯濾波擁有更好的邊緣細節。但該算法用于較為復雜的大圖像時,可能會遇到全局閾值沒有典型性的問題,隨著圖像大小和復雜度的提高,全局閾值或被拉到較為不合理的數值,大大降低了全局閾值對圖像邊緣的保護效果,另外,如果對信噪比過低的圖像采用此濾波方法將導致噪聲被放大的情況。如采用圖像分割濾波技術,將圖像分區塊求取閾值單獨處理,或將得到更好的濾波效果,這也是下一步應著重研究的改進辦法。