導航接收機中鑒頻鑒相器的設計

張治國,黃海生,李 鑫,黨 成

導航接收機中鑒頻鑒相器的設計

張治國,黃海生,李 鑫,黨 成

(西安郵電大學 電子工程學院,西安 710121)

導航接收機;鎖相環;鑒頻鑒相器;死區;低噪聲

0 引言

導航接收機的靈敏度、首次定位時間等性能,直接影響著衛星通信的質量,信號捕獲與跟蹤能力決定了系統的整體性能。鎖相環(phase locked loop, PLL)頻率綜合器,作為導航接收機中的關鍵模塊之一,為接收機產生本振信號,再與衛星信號混頻后,將其下變頻成中頻信號[1]。同時,PLL的相位噪聲也將隨本振信號傳輸到下一級電路,降低了中頻信號的載噪比,使得對衛星信號跟蹤能力的魯棒性減小[2]。鑒頻鑒相器(phase frequency detector, PFD)能對參考信號和環路反饋信號的頻率和相位誤差進行檢測,并源源不斷地為PLL環路提供檢測結果,使得PLL輸出頻率為參考頻率的倍,且相位同步,即產生穩定的本振信號。而PFD的死區,是產生PLL噪聲的主要原因之一,理想的PFD具有無死區、低噪聲的特點,但在實際應用中,死區帶來的抖動和噪聲,使得PFD的延時不匹配,周期性的時鐘信號在過零點時偏離了理想位置,以及PFD自身的噪聲影響,極大地惡化了頻譜的純度及鎖相環系統的性能[3]。

文獻[4]采用單相時鐘結構,設計了無反饋路徑的PFD,減小了功耗,提高了工作頻率,然而忽略了在高頻信號的周期遠小于復位信號的周期的情況下,會降低PFD的鑒相范圍,限制了鑒相曲線的線性度。文獻[5]使用基于時鐘乘法器的PFD,通過在延遲線的輸出信號與參考信號間建立延時誤差,控制機制作用于延遲線以減小誤差,進而消除靜態相位偏移,但由于電路增加了乘法器,增大了三位時間,導致防死區脈沖過大,延長了鎖定時間。文獻[6]通過對比三種類型的PFD性能,最終采用了基于觸發器的PFD,該結構使用較少的晶體管數量,減小了功耗,縮小了死區時間,但由于電路輸出阻抗較小,限制了增益,降低了電路的驅動能力。本文基于以上多種類型的PFD電路的優點,在傳統的PFD結構基礎上,改進了復位電路,加入了脈沖寬度可調節的延時單元,對電路性能進行優化,并對設計的主要指標進行了仿真與對比。本文設計了4種不同的復位延時,可根據輸入頻率的變化,選擇合適的復位延時,實現了較高的工作頻率和較低的噪聲特性,而且邏輯門電路采用共源共柵結構,提高了電路增益,可以適應工藝帶來的誤差,提高了可靠性。

1 PFD的工作原理

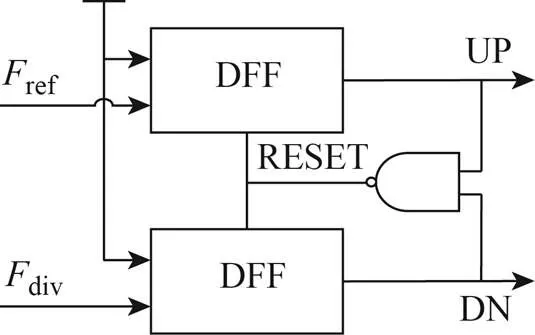

圖1 傳統的PFD電路圖

2 PFD電路設計

2.1 傳統的鑒頻鑒相器

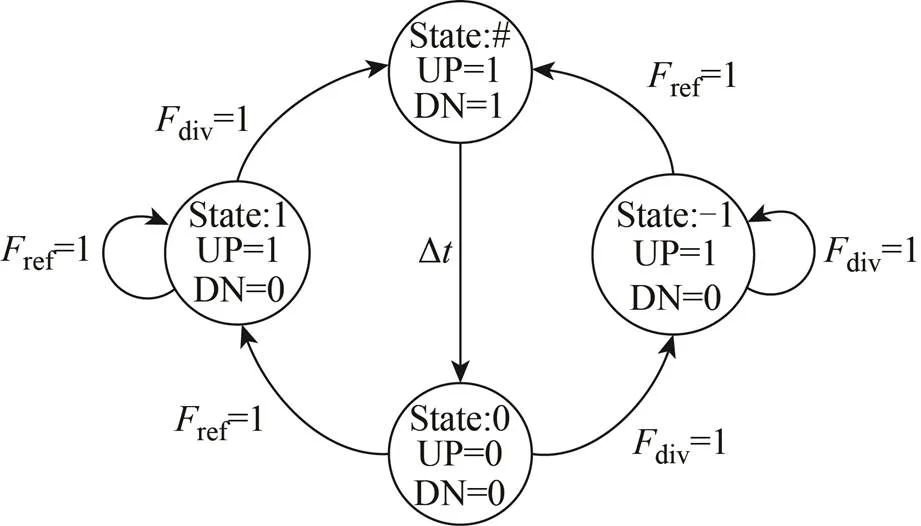

理論上,PFD電路輸出有三種情況:狀態(State)0,UP=0,DN=0;狀態1,UP=1,DN=0;狀態-1,UP=0,DN=1;UP=1,DN=1是一個過渡狀態,傳統的PFD狀態轉移圖如圖2所示。

圖2 PFD狀態轉移圖

這類三態型PFD的工作原理,是產生兩個非互補輸出信號的異步狀態。因為將圖1中的UP和DN信號相減得到的PFD輸出,輸出電壓的平均值與相位差呈線性關系,所以該類型PFD的線性工作范圍較寬,靈敏度較高、線性度較好。為了消除“死區”效應,在觸發器的復位端和與非門輸出端之間加入了延時單元。

2.2 改進的鑒頻鑒相器

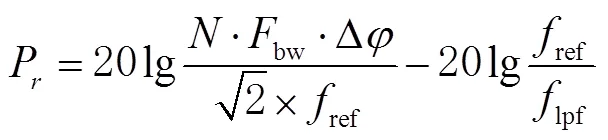

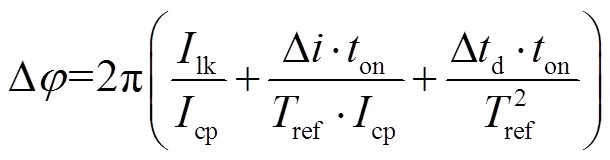

通過對常用的傳統結構的PFD的性能分析,在保留傳統PFD鑒相靈敏度高、線性度較好的基礎上,希望所設計的PFD具有無“死區”、鑒相精度高、工作頻率高的特點。在低頻電路中,由于金屬氧化物半導體(metal-oxide-semiconductor, MOS)管和其他電子元件的非線性特性,導致一些電荷通過寄生電容發生泄露,進而在電路中轉化為參考雜散。其參考雜散的表達式[8]為

式中:為電荷泵的輸出電流;為電荷泵的泄露電流;為輸入參考時鐘的周期;和分別為電荷泵的失配電流和失配時間Ton為復位時間。由于這些參數直接受到電荷泵的影響,所以,對于PFD而言,可以通過減小PFD的復位時間來實現降低參考雜散的目的。基于以上分析,圖3為改進后的PFD電路。

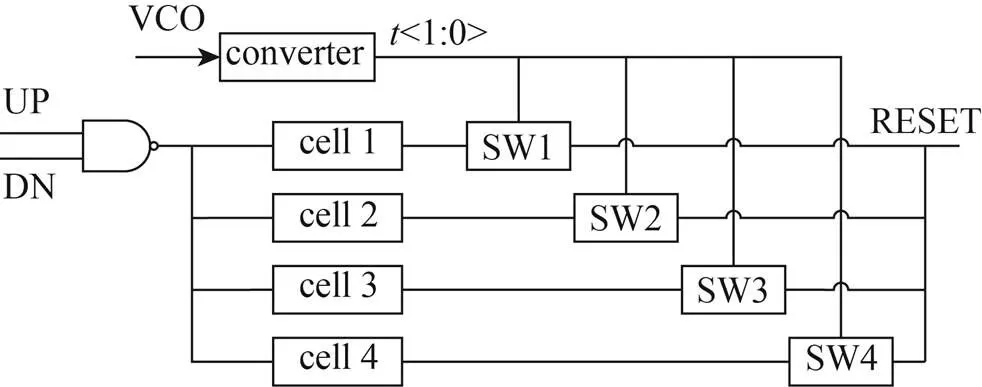

2.3 可調延時單元

理論上只要UP和DN的信號足夠寬,電荷泵總會被有效開啟。而脈沖寬度依賴于復位信號的延時。在頻率范圍較寬的情況下,脈沖信號需要一個合適的范圍[9]。如果脈沖信號較寬,則會增加鎖相環鎖定時間;如果脈沖信號較窄,則無法消除死區效應。在低頻信號輸入時,相對較寬的脈沖信號可以有效地消除死區效應;在高頻信號輸入時,如果繼續使用較寬脈沖信號,那么脈沖寬度將大于反饋信號頻率周期,使得PFD無法繼續跟蹤相位[10]。所以本文采用一種脈沖寬度可調節的延時單元,可調延時單元的目的是合理地控制PFD的復位時間,不僅可以有效地消除PFD的死區時間,同時也會不過量地增加電荷泵的工作時間[11]。根據頻率信號輸入范圍,分別通過四路不同的緩沖器,產生4種不同的脈沖寬度。將VCO的輸出頻率范圍分為4段:2.30~2.60,2.55~2.85,2.80~3.10,3.05~3.40 GHz。當VCO輸出頻率處于該范圍時,頻率-電壓轉換器(converter)控制復位信號經過傳輸門后[12],選擇不同的脈寬,來達到消除死區的目的。

圖4 可控延時單元結構圖

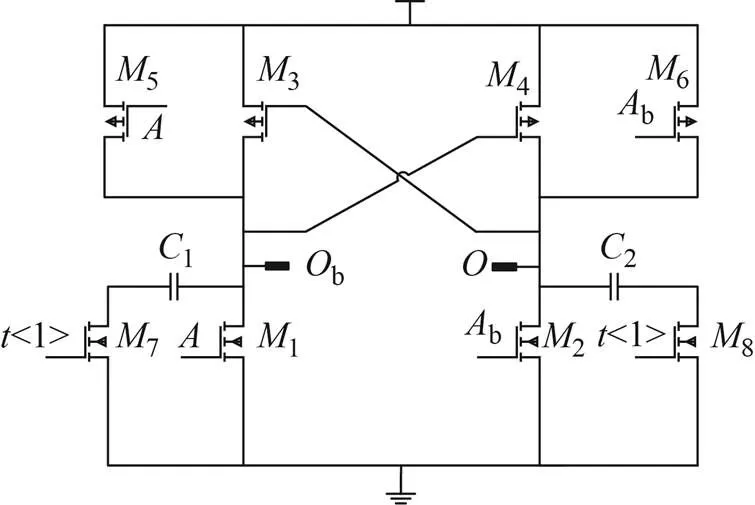

圖5為門延時電路結構。

圖5 門延時電路結構圖

3 仿真結果

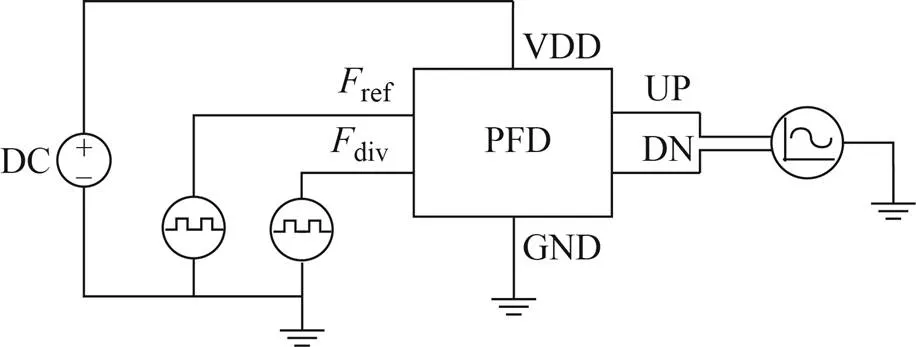

圖6 PFD測試電路

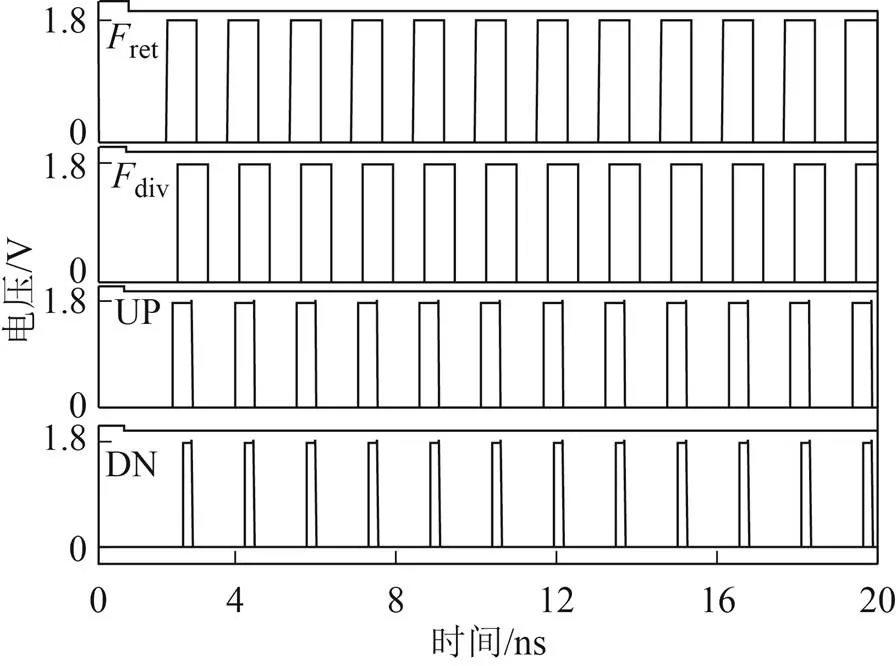

圖7 PFD的時序分析

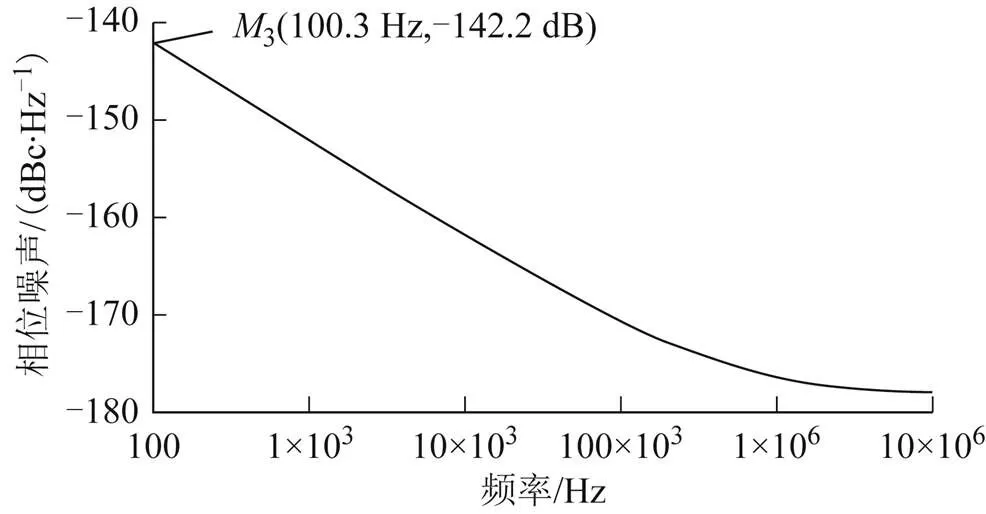

圖8 相位噪聲仿真圖

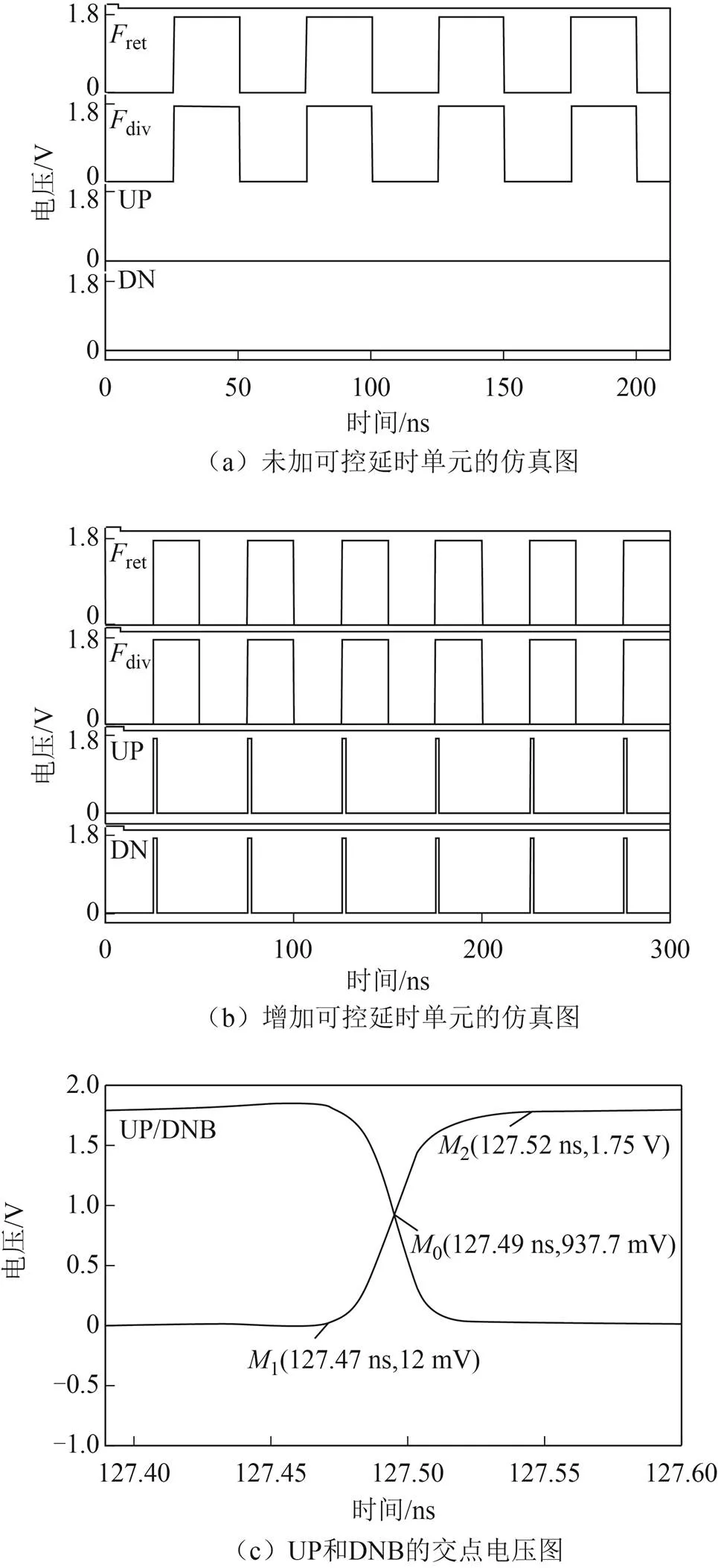

圖9 相位差為60°時的仿真圖

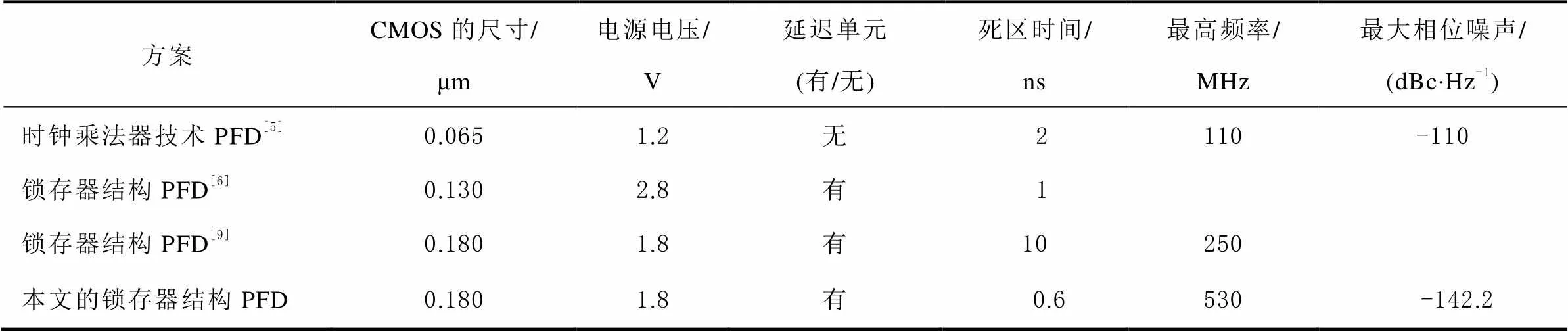

表1列舉了本文與近年來相關論文中PFD的主要指標的對比數據,本文提出的基于鎖存器結構的可調節延時單元PFD,在1.8 V電源電壓下,最小的死區時間為0.6 ns,最高工作頻率為530 MHz,最大相位噪聲為-142.2 dBc/Hz,皆優于文獻[5-6, 9]的各項指標,凸顯了本文在電路設計方面的特色。綜上所述,在同等工藝水平下,本文提出的PFD電路在主要指標上具有一定的明顯優勢。

表1 PFD主要指標對比

4 結束語

本文設計了一種應用于導航接收機的鑒頻鑒相器電路,通過改進復位電路,實現了四種復位延遲,可以適用于較寬范圍內的輸入頻率,并且有效消除了鑒相死區。仿真結果表明,在保證鑒頻鑒相器功能正確的前提下,電路的輸出波形對稱,且達到了低噪聲的效果,可以應用于導航接收機的頻率合成器中,能有效提高電路的穩定性。

[1]于越. 應用于衛星導航頻段鎖相環頻率綜合器的設計[D]. 桂林: 桂林電子科技大學, 2019.

[2]張久民, 段吉海, 徐衛林, 等. 一種寬動態范圍低失配的電荷泵[J]. 微電子學, 2020, 50(1): 84-89.

[3]王嘉齊, 黃海生, 李鑫, 等. 一種應用于射頻接收機的電流舵電荷泵設計[J]. 重慶郵電大學學報(自然科學版), 2019, 31(4): 524-530.

[4]HE Yi, CUI Xiaole, XUE Dongmei. An improved fast acquisition PFD with zero blind zone for the PLL application[C]//The Institute of Electrical and Electronic Engineers (IEEE). Proceedings of IEEE International Conference on Electron Devices and Solid-State Circuits. Chengdu: IEEE, 2014: 1-2[2020-06-18].

[5]WANG Yuwen, YE Fan, REN Junyan. A DLL based low-phase-noise clock multiplier with offset-tolerant PFD [C]//The Institute of Electrical and Electronic Engineers (IEEE). Proceedings of the IEEE 10th International Conference on ASIC. Shenzhen: IEEE, 2013:1-4[2020-06-18].

[6]ANUSHKANNAN N K, MANGALAM H, DHARANI V A, et al. Comparison and analysis of various PFD architecture for a phase locked loop design[C]//The Institute of Electrical and Electronic Engineers (IEEE). Proceedings of IEEE International Conference on Computational Intelligence and Computing Research. Enathi: IEEE, 2013: 1-4[2020-06-18].

[7]孫境余, 王春雷, 侯力梅, 等. CMOS鎖相環中鑒頻鑒相器的研究[J]. 黑龍江大學自然科學學報, 2016, 33(3): 416-420.

[8]LI Sen, JIANG Jinguang, ZHOU Xifeng, et al. A low phase noise and low spur PLL frequency synthesizer for GNSS receivers[J]. Journal of Semiconductors, 2014, 35(1): 100-107.

[9]SHARMA A, SHARMA G K, KISHOR JOHAR A, et al. Design, Analysis and comparison of PFD architectures for fast locking frequency synthesizer[C]//The Institute of Electrical and Electronic Engineers (IEEE). Proceedings of Women Institute of Technology Conference on Electrical and Computer Engineering (WITCON ECE). Dehradun Uttarakhand, India: IEEE, 2019: 218-222[2020-06-18].

[10]薛顏, 楊霄壘, 周啟才, 等. 一款低抖動寬調節范圍鎖相環頻率合成器的設計[J]. 中國電子科學研究院學報, 2014, 9(1): 101-104.

[11]GULIHAR L, KRISHAN B. Low power with minimal delay phase frequency detector[J]. International Journal of Signal Processing, Image Processing and Pattern Recognition, 2016, 9(8): 243-252.

[12]SURAKAMPONTORN W, CHONBODEECHALERMROONG Y, BUNJONGJIT S. An analog sinusoidal frequency-to-voltage converter[J]. IEEE Transactions on Instrumentation and Measurement, 1991, 40(6): 925-929.

[13]SOFIMOWLOODI S, RAZAGHIAN F, GHOLAMI M. Low-power high-frequency phase frequency detector for minimal blind-zone phase-locked loops[J]. Circuits, Systems, and Signal Processing, 2019, 38(2): 498-511.

Design of phase frequency detector based on navigation receiver

ZHANG Zhiguo,HUANG Haisheng,LI Xin,DANG Cheng

(School of Electronic Engineering, Xi'an University of Posts and Telecommunications, Xi'an 710121, China)

In order to improve the accuracy and stability of the local oscillator frequency in navigation receivers, to avoid the drift of the local oscillator signal in the phase-locked loop circuit, the paper designed a phase frequency detector: based on China's Semiconductor Manufacturing International Corp. (SMIC) 0.18 μm Complementary Metal–Oxide–Semiconductor (CMOS) process, a dead-zone-free phase frequency detector with adjustable reset pulse width was given; and the reset pulse width was adjusted to achieve 4 different reset delay according to the feedback frequency signal of the voltage-controlled oscillator, which could effectively eliminate the phase discrimination dead zone while reducing jitter. Experimental result showed that: when the voltage was 1.8 V, the maximum operating frequency of the detector would be 530 MHz, with the maximum amplitude noise -142.2 dBc/Hz; and the frequency and phase discrimination function of this circuit could be correct with good frequency and noise characteristics, indicating the feasibility of the detector for the phase-locked loop circuit of navigation receivers.

navigation receiver; phase-locked loop; phase frequency detector; dead zone; low noise

P228

A

2095-4999(2021)02-0035-06

張治國,黃海生,李鑫,等. 導航接收機中鑒頻鑒相器的設計[J]. 導航定位學報, 2021, 9(2): 35-40.(ZHANG Zhiguo, HUANG Haisheng, LI Xin, et al. Design of phase frequency detector based on navigation receiver[J].Journal of Navigation and Positioning, 2021, 9(2): 35-40.)

10.16547/j.cnki.10-1096.20210206.

2020-07-01

國家自然科學基金-地區科學基金項目(61661049)。

張治國(1994—),男,陜西寶雞人,碩士研究生,研究方向為模擬集成電路。

黃海生(1964—),男,陜西西安人,碩士,教授,研究方向為專用集成電路與系統設計。