一種基于FPGA的步進電機控制系統的設計*

邱靖超劉新妹殷俊齡楊冰

一種基于FPGA的步進電機控制系統的設計*

邱靖超1,劉新妹1,2,殷俊齡1,楊冰1

(1.中北大學信息與通信工程學院,山西 太原 030051;2.中北大學電子測試技術國防科技重點實驗室,山西 太原 030051)

基于FPGA技術設計了一種對步進電機的控制系統,通過對三種加、減速算法的分析與研究,采用HDL(Hardware Description Language)硬件描述語言編寫了步進電機運動控制程序,并且通過Modelsim軟件仿真驗證了控制系統的可行性,最終實現了系統的軟硬件設計。結果表明本步進電機控制系統能滿足課題需求,并可擴展到實現多路步進電機的閉環控制等方面。

FPGA;步進電機;脈沖控制;梯形加減速算法

隨著數字電子技術的迅猛發展,步進電機及其脈沖控制和高精度的特點已被廣泛應用于運動控制系統,且要求也越來越高[1]。基于FPGA對步進電機簡單的控制包括電機的啟動、運行以及停止等動作,也可進行位置和速度的控制[2]。本設計就是基于FPGA的對電機的速度、位移、方向等做精確控制的系統設計。

步進電機最常用的速度控制方法是運用單片機產生控制信號[3],實際工程應用中,由于各種電機驅動參數不同,就需要設計不同的驅動器,而傳統的控制方法操作模式復雜,制作成本也較高[4]。步進電機控制采用單片機和DSP芯片作為其核心,常以定時器的方式產生控制脈沖[5],因此占用可觀的系統資源[6],脈沖頻率更是為微控制器所限制。本設計基于FPGA(現場可編程門陣列)實現參數可配置的步進電機驅動控制系統,采用FPGA作主控芯片,為課題中實現對兩相混合式步進電機的控制,充分發揮FPGA在編程、I/O資源豐富、計算速度快(并行)等方面的優勢[7]。

1 步進電機控制理論簡介

1.1 步進電機及工作原理

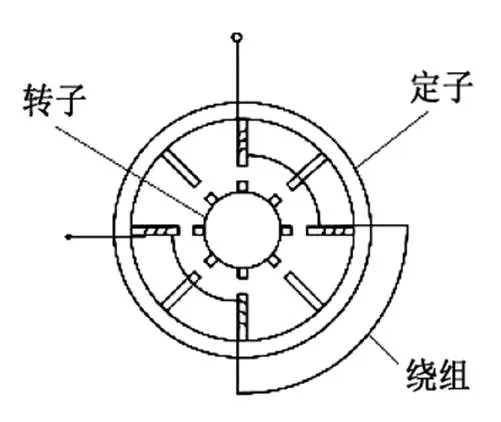

步進電機是將電脈沖信號轉化為角位移或線位移的數字式開環控制元件[8],在進行加減速時,通過控制單位時間內輸出的脈沖數來改變其脈沖頻率[9]。脈沖信號的頻率和脈沖數能決定步進電機的轉速和停止的位置。工作原理是利用電子電路,將直流電變為分時供電的多相時序控制電流,用這種電流為步進電機供電,步進電機才能正常工作。步進電機按結構可以分為反應式步進電機、永磁式步進電機、混合式步進電機等,其中最廣泛使用的使兩相混合式步進電機,其內部結構如圖1所示,主要由定子、定子繞組、轉子組成。

步進電機的基本參數有空載啟動頻率、步距角和精度。空載啟動頻率即步進電機在空載情況下能夠正常啟動的脈沖頻率,其中步距角表示控制系統每發一個步進脈沖電機所轉到的角度,由以下公式確定[10]:

s=180°/r(1)

式(1)中:為定子相數;r為轉子齒數。

圖1 步進電機內部結構(一相繞組)

本設計使用兩相混合時步進電機的轉子齒數為50,該種步進電機的基本步距角為1.8°。一般步進電機的精度為步距角的3%~5%,且不累計。

1.2 加減速控制算法(曲線)及特性

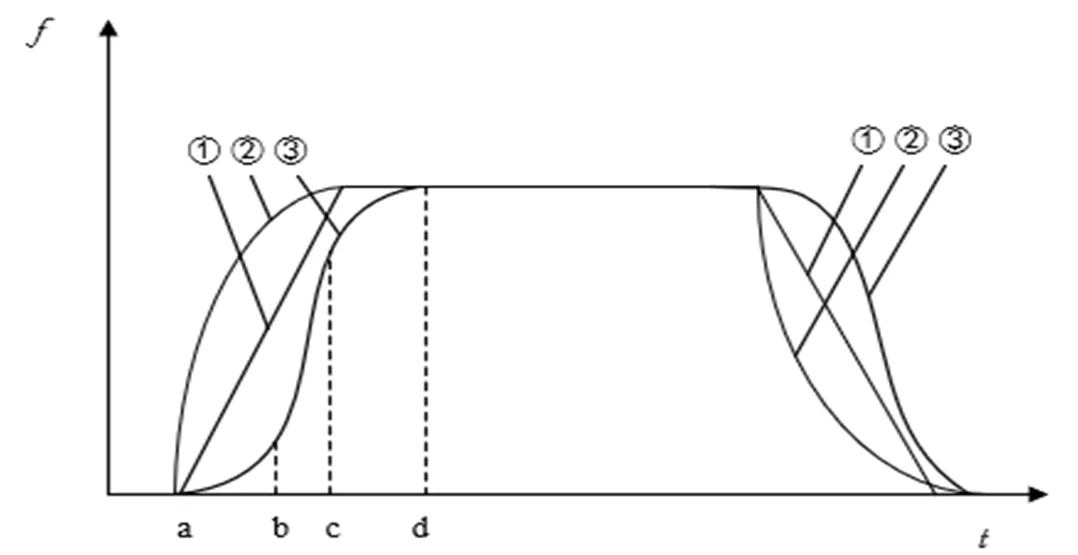

在數控系統中按控制算法分類加、減速控制曲線主要有梯形曲線、指數曲線和S形曲線等三種[15],其特性曲線如圖2所示。

圖2 三種加減速控制曲線圖

圖中曲線①所示梯形加減速控制曲線數學方程式為:

s()=0+(2)

式(2)中:s()為進給脈沖頻率;0為加減速起始進給脈沖頻率;為加速度。

如果設c為指令脈沖頻率,則當s()≠c時,系統可根據加速度進行加速或減速控制。

梯形加減速控制特點為:在加減速起點和終點存在加速度突變,速度過渡不夠平滑,但由于算法簡單,仍得到廣泛應用。

圖中曲線②所示指數加減速控制曲線數學方程式為:

式(3)中:為加減速時間常數。

對于式(3),開始加速時(=0),設起始進給脈沖頻率0=0;當→∞,將進入勻速運行階段;如果減速降頻開始,設輸入指令脈沖頻率為0,則起始進給脈沖頻率等于原指令脈沖頻率,即0=c。

指數型加減速控制特點為:指數型與梯形相比,平滑性好,運動精度高,但在加減速的起點仍然存在加速度突變且實現算法比較復雜,占用過多的CPU資源,對處理器平臺要求過高[16]。

S曲線加減速控制曲線。

如圖2所示,S曲線加減速控制特點為:以加速階段為例,S曲線加減速控制可劃分為加加速段(ab)、勻加速段(bc)和減加速段(cd)。S曲線法能保證加速度的變化是連續的,從而可避免柔性沖擊。但S曲線加減速控制要實現多階段和自動加減速控制,參數調整不易,算法實現較為復雜,因此S曲線加減速控制多用軟件來實現。

2 基于FPGA的步進電機控制器的設計

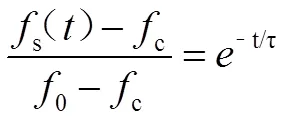

本設計的控制系統由FPGA、步進電機驅動模塊和步進電機本體三部分構成。

2.1 系統硬件設計

步進電機控制系統結構硬件框圖如圖3所示。FPGA選用Altera公司的CycloneⅣ系列的EP4CE6E22C8N芯片為核心,利用串口通信,把上位機的命令傳遞給FPGA,FPGA通過電機驅動芯片A3977控制步進電機。A3977是一種新型的專門用于雙極性步進電機的微步進電機驅動集成電路,它主要的設計功能包括:自動混合模式電流衰減控制,pwm電流控制,同步整流,低輸出阻抗的DMOS電源輸出,HOME輸出,休眠模式以及易實現的步進和方向接口等。FPGA與A3977之間通過數字IO進行步進電機驅動控制,A3977對電機的驅動由其內部的雙DMOS管組成H橋實現,將12 V加載到電機上實現驅動控制。

2.1.1 通信模塊

FPGA與上位機之間通過串口(UART)轉USB進行通信,芯片采用PL2303將標準的UART協議轉換為USB協議,在計算機安裝驅動后,便是一個虛擬串口實現UART的傳輸。UART的數據傳輸不需要時鐘,只要兩條信號線分別進行數據收發。UART最終通過USB接口與計算機連接,建立起虛擬串口通信。

圖3 硬件設計框圖

2.1.2 驅動模塊

驅動器用于將FPGA發送的電脈沖信號轉換為角位移。本設計使用42BYGH34-04A型號電機,FPGA與A3977的數字IO接口的連接如圖4所示。

圖4 FPGA與A3977的數字IO接口圖

其中,STEP是驅動步進電機的脈沖信號。該信號的上升沿發起一個步進動作,即步進電機“邁”一步。而步進電機“邁”一步的步幅則由MS[1∶0]決定。DIR是步進電機方向控制信號;EN是步進電機工作使能信號,該信號拉低,STEP、DIR和MS[1∶0]信號的控制才有效。RESET是驅動芯片A3977復位信號,低電平有效。正常工作時,該信號需要拉高。MS[1∶0]是步進分辨率選擇,即“步幅”的設定。HOME是回響脈沖。對應不同的步進分辨率,HOME脈沖的周期數不同。例如,MS[1∶0]=2′b11時,每32個STEP產生一個響應HOME脈沖。

2.2 系統軟件設計

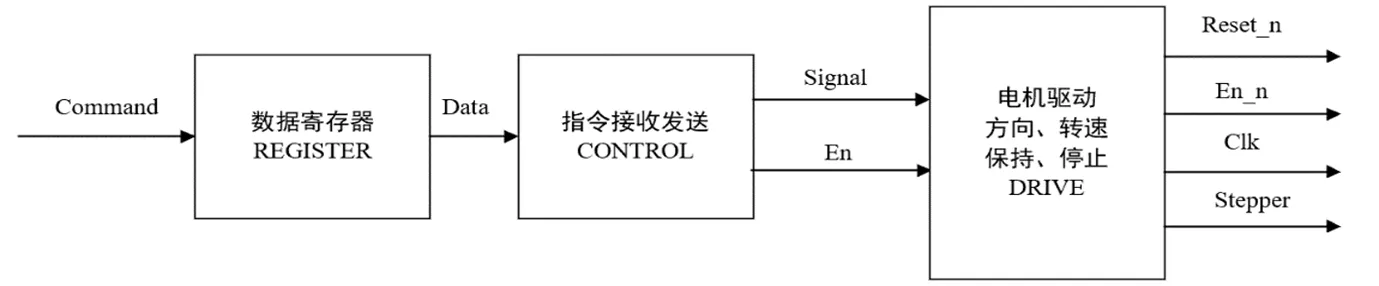

本設計采用QuartusⅡ平臺,運用Verilog語言自頂向下進行FPGA程序設計;主要分為數據寄存器、指令控制器和電機啟動三個模塊(模塊劃分及接口如圖5所示),人機交互界面采用labview軟件設計。從上位機發出的方向,步數等指令先傳給數據寄存器,當外部驅動指令發出后,由指令接收發送模塊將數據傳遞給電機驅動模塊。模塊DRIVE接收到信號后,控制步進電機的啟停、方向和轉速等。

2.2.1 步進電機控制模塊

步進電機控制模塊需要實現的功能主要有正反向、加減速、步數、啟動和停止。雖然設定STEP處于不同的頻率,從而控制步進電機的轉速,但步進電機從停止到目標頻率通常有一個加速過程,從目標頻率到停止也有一個減速過程。步進電機有一個啟動頻率的概念,可以直接驅動步進電機從停止到低于啟動頻率的某個頻率,不需要任何加速。因此,控制步進電機從啟動頻率(一般比啟動頻率低一點)加速到目標頻率,減速也是從目標頻率減到啟動頻率,然后步進電機停止運行。

圖5 軟件模塊和接口設計

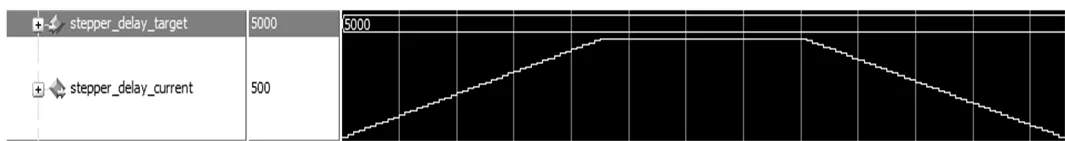

首先判斷步進電機驅動的目標頻率stepper_delay_tar-get與當前頻率stepper_delay_current的值是否一致,若一致,則不作任何加速、減速操作,保持當前速度運行;若目標頻率高于當前頻率,則執行加速;若目標頻率低于當前頻率,則執行減速。

在加速或減速控制開啟狀態下,分頻計數邏輯每10 ms產生一個高脈沖,用于切換當前的速度。這個10 ms的定時值可以根據實際電機驅動情況調整,對于勻速加速而言,步進電機從啟動頻率到目標頻率需要經過個中間頻率(的值越大,步進電機運轉得越穩定,越不容易堵轉或失步)。而定時10 ms,就是要保證步進電機在每個中間頻率都停留10 ms。在電機穩定的加速或減速運轉與耗費的時間之間尋求一個平衡。每10 ms,步進電機的速度都會加速或減速固定的頻率值,本設計中設定為“100”,例如,從500 Hz 加速到5 000 Hz,依次經過的頻率點為500 Hz、600 Hz、700 Hz……4 900 Hz、5 000 Hz。當加速或減速到目標頻率時,加速和減速控制結束。

2.2.2 通信模塊

本模塊功能是接收從PC機向FPGA控制模塊發送的步進電機控制信號,由3個功能模塊組成,分別是波特率模塊speed_setting.v,實現串口波特率的控制;接收模塊my_uart_rx.v,該模塊通過解析uart_rx信號獲得串口數據字節;發送模塊my_uart_tx.v,該模塊將從上位機接收到的數據發送出去。

3 實驗仿真與驗證

本文采用勇敢的芯SF-CY4開發板進行仿真與實驗驗證,FPGA型號為EP4CE6E22C8N,系統時鐘為50 MHz,周期為20 ns,驅動板芯片為allegro公司的A3977,供電電壓為12 V。軟件平臺為QuartusⅡ13.1,使用Quartus自帶的仿真軟件Model-sim對FPGA的輸出波形進行功能仿真,由以下幾步完成。

3.1 編寫testbench仿真測試.v文件

為了驗證以上邏輯設計是否成功,在下載到開發板觀察現象之前通過編寫激勵文件,并將其保存到工程對應的testbench文件夾下。

3.2 運行仿真

設置好仿真腳本后,選擇Tools→Run Simulation Tool→RTL Simulation進行功能仿真,如圖6所示。

圖6 開啟功能仿真

3.3 仿真結果與分析

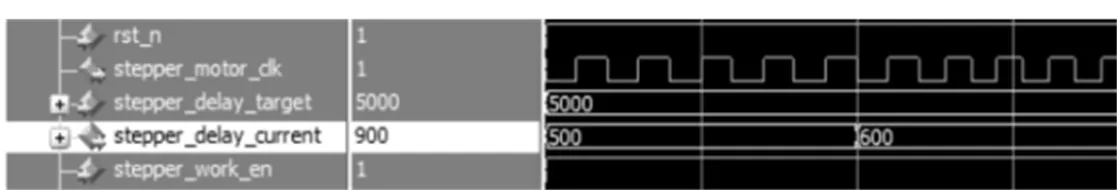

設定步進電機的起步頻率為500 Hz,目標頻率為5 000 Hz,仿真運行,在ModelSim圖中rst_n為復位信號;stepper_work_en信號是步進電機的使能信號;stepper_delay_ current和stepper_delay_target分別為步進電機驅動脈沖的當前頻率和目標頻率;stepper_motor_clk信號是步進電機的前進脈沖。當復位信號rst_n為高電平且stepper_work_en信號也為高電平時,步進電機進入運行狀態,圖中rst_n和tepper_work_en信號都為1,stepper_motor_clk信號的一個上升沿就引起電機一個步距角的轉動。前仿真波形如圖7所示。

圖7 前仿真波形

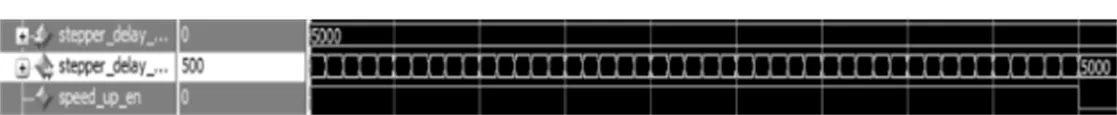

程序中設置的脈沖數為1 215,分頻系數為45,在Model-sim中仿真的結果如圖8所示。

圖8 加速過程分頻

因時間間隔相等,都為100 Hz(10 ms),從500 Hz加速到5 000 Hz,一共有45個速度等級,因此分頻數是45;頻率為500 Hz時脈沖數為5(500/100 Hz),脈沖為600 Hz時脈沖數為6(600/100 Hz),以此類推,當頻率增加到4 900 Hz時,脈沖數為49,總的脈沖數為5+6+7+…+49=1 215。

加速階段中,脈沖頻率每隔100 Hz增大一次,每個頻率的保持時間為10 ms,因為每個單位時間內增加的脈沖頻率也為100 Hz,所以脈沖數加1,即對應圖中左邊部分脈沖數為6,右邊部分脈沖數為7。加速脈沖波形如圖9所示。

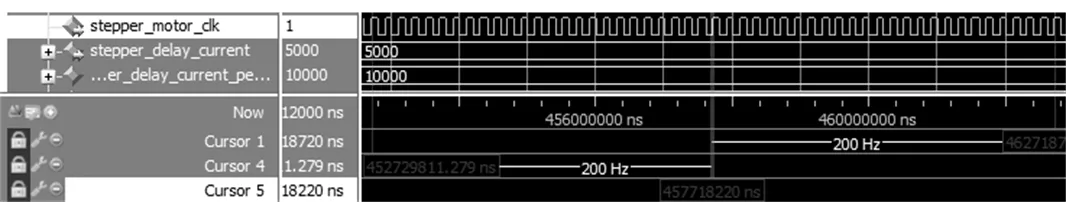

勻速階段中,當脈沖頻率增加到了5 000 Hz時,脈沖寬度一定,頻率不變,單位時間內的脈沖個數不再發生變化,每100 Hz的時間里脈沖個數為50。

圖9 加速脈沖波形

勻速脈沖波形如圖10所示。

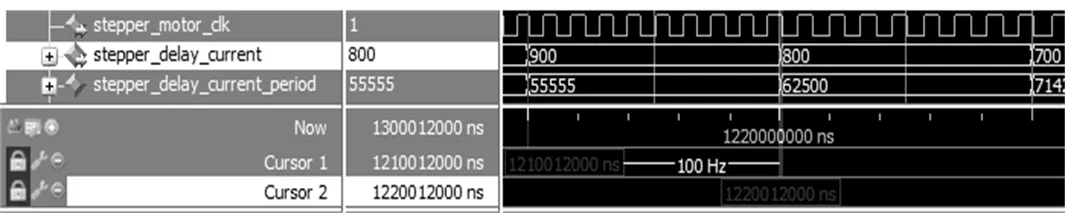

圖10 勻速脈沖波形

減速階段中,脈沖頻率每隔100 Hz降低一次,每個頻率的保持時間為10 ms,因為每個單位時間內減小的脈沖頻率也為100 Hz,故脈沖數減1,即對應圖中左邊部分脈沖數為9,右邊部分脈沖數為8。減速脈沖波形如圖11所示。

圖11 減速脈沖波形

為了更為直觀地觀察輸出波形的變化,通過把輸出數據格式改為模擬的自動模式,即可看到FPGA輸出的脈沖波形為梯形,如圖12所示。

圖12 梯形加減速仿真波形

4 結論

在加速階段步進電機驅動當前的脈沖信號stepper_ delay_current頻率逐漸增大,在勻速階段維持不變,減速階段逐漸減小。其中,每隔一定的時間,脈沖頻率增大一次,每次增加100 Hz。一個脈沖步進電機產生固定的位移,在加、減速階段由于頻率的變化,步進電機的轉速也會變化,單位時間內的位移會發生變化,并且可看出整體設計符合預期。通過以上對仿真波形的分析,脈沖頻率的大小按照勻加速—勻速—勻減速這一規律變化,整個輸出波形為一個等腰梯形,即步進電機的轉速也按照這一形式變化,仿真結果與本設計相符,基于FPGA實現了步進電機的梯形加減速控制。

5 結語

本文針對步進電機控制系統的要求,采用FPGA設計了各個功能模塊,并采用Verilog語言編程,進行了功能仿真和時序仿真。結果表明,各個功能模塊邏輯清晰、合理,系統穩定性良好,各項指標符合設定要求。利用FPGA并行控制的特點,在本設計上的基礎上可以實現多路步進電機的閉環控制,具有可移植性高、適用性廣的特性。

[1]楊永清,吳學杰.基于ARM和FPGA的多通道步進電機控制系統[J].裝備制造技術,2017(3):177-180.

[2]劉東征,吳學杰.基于FPGA的步進電機控制芯片設計[J].工業控制計算機,2011(4):71-72.

[3]張雷.基于FPGA步進電機開環驅動設計[D].哈爾濱:黑龍江大學,2013.

[4]潘濤,程耕國.步進電機控制器的FPGA實現[J].現代電子技術,2009(1):148-150.

[5]方旭,吳學杰,黃鴻國.多通道步進電機控制系統的設計[J].儀器儀表與分析檢測,2014(3):1-4.

[6]楊永清.基于STM32和FPGA的多通道步進電機控制系統設計[D].成都:西南交通大學,2014.

[7]AVEY J.An FPGA-based Hardware Accelerator for Iris Segmentation[D].Ames:Iowa State University,2018.

[8]YU J,KANG H M,WANG Y S,et al.A control system of t-hree-axis stepper motor based on the FPGA[C]//International Conference on Mechatronic Sciences,Electric E-ngineering and Computer.Shengyang:IEEE,2013:3334-3337.

[9]ATES H E.Design and realization of a step motor driver with micro-stepping capability[D].Ankara:Middle East Technical University,2011.

[10]李信鋒.兩相混合式步進電機矢量控制和位置伺服算法研究[D].深圳:深圳大學,2015.

[11]叢爽,李澤湘.實用運動控制技術[M].北京:電子工業出版社,2006.

[12]李金洪.步進電機FPGA變速控制系統設計[J].電子制作,2015(18):15-16.

TN79

A

10.15913/j.cnki.kjycx.2021.08.004

2095-6835(2021)08-0011-04

山西省科技廳重點研發項目(編號:201903D121058)資助

邱靖超(1992—),男,工學碩士生,主要研究方向為電子測試技術、FPGA與嵌入式系統開發等。

〔編輯:張思楠〕