基于對偶單元法的三維集成微系統電熱耦合分析*

曹明鵬 吳曉鵬? 管宏山 單光寶 周斌 楊力宏 楊銀堂

1) (西安電子科技大學微電子學院, 西安 710071)

2) (電子元器件可靠性物理及其應用技術重點實驗室, 廣州 510610)

隨著三維集成微系統集成度和功率密度的提高, 同時考察電設計與熱管理的多場耦合分析勢在必行.本文面向三維集成微處理器系統, 通過改進的對偶單元法(dual cell method, DCM)實現了系統的快速電熱分析.該方法通過引入泄漏功率、材料系數隨溫度的耦合, 相比于傳統有限元法在更新以及組裝本構矩陣上有更大的優勢.仿真驗證表明, 本文所采用的算法相比傳統有限元法仿真速度提升了約30%.在考慮了材料系數以及泄露功率熱耦合因素后, 系統熱點溫度相對于考慮耦合前上升了20.8 K.最后采用本文所提出算法對三維集成微處理器系統進行布局研究, 比較了硅通孔陣列常規布局和集中布局在處理器核心下方兩種布局方式對上下層芯片熱點溫度的影響, 研究了功率不均勻分配對兩種布局的影響.

1 簡 介

目前三維集成技術是延續摩爾定律引領集成電路發展走向后摩爾時代的有力解決方案[1].三維集成微系統具有高集成度、微小型化、低功耗、高可靠性和高效率等優點, 在邏輯計算處理、成像傳感和光集成等方面具有廣闊的應用前景.但是三維集成技術同時導致了微系統內單位面積上產生的熱功耗急劇增加.以處理器芯片為例, 目前CPU的功耗密度達到了100 W/cm2以上[2], 功率密度的增加和功率的不均勻分布共同導致了嚴重的熱問題.而這些熱問題反之對諸如泄露電流、電遷移、信號和電源完整性等電設計提出了諸多挑戰.其中泄漏功率是目前處理器性能的最重要限制因素之一, 對于65 nm 及更先進的工藝節點, 泄漏功率占總功率的10%以上[3].泄漏功率與溫度呈指數關系, 因此泄漏功率將導致處理器發熱并進一步增加泄漏功率本身.隨著溫度的變化, 在傳熱過程中材料的熱導率會發生改變, 從而對熱點溫度產生影響[4].綜上所述, 對高功耗三維集成微系統在設計初期進行電熱耦合分析在確保系統可靠性方面具有至關重要的作用.

有限元法(finite element method, FEM)由于在復雜幾何形狀、材料建模方面具有極好的適應性和精度, 因此常被用于電熱耦合的分析研究[5?11].為了使該算法更適于三維集成微系統分析, 在算法改進方面開展了諸多研究工作.Lin 等[12,13]提出了一種芯片級泄漏感知方法, 采用交替方向隱式法結合芯片功率、工作頻率和電源電壓之間的各種電熱耦合, 預測芯片熱分布.該方法采用了等距網格,這雖然提升了計算速度, 但也同時導致精度下降.北京大學的Pi 等[14]提出了一種快速的3D-IC 熱管理全芯片規模數值模擬方法, 該法同時考慮了橫向和縱向散熱的緊湊型熱阻網絡, 充分分析了硅通孔(through silicon via, TSV)、微凸塊和再分布層中的高導熱路徑.然而該研究所用的熱阻網絡無法獲得十分準確的溫度場, 并且未考慮溫度帶來的耦合因素.Chai 等[15]開發了徑向點插值法, 并對TSV 陣列進行了電熱耦合特性研究, 提高計算效率并降低了存儲成本, 加快了基于TSV 的3-D IC的電熱設計.但是這項工作目前僅集中在TSV 模型上, 還無法對整個三維微系統進行分析.Wang等[16]提出了一種動態線性泄漏電流感知的全芯片熱估計方法.該算法將非線性熱模型轉換為多個局部線性熱模型, 并設計了一種自適應降階法以提高效率.但線性泄露電流僅能運用于瞬態仿真迭代,無法在穩態迭代中使用.

針對以上研究中存在的問題, 本文提出了一種能夠快速計算電熱耦合的改進對偶單元法(dual cell method, DCM).該方法在考慮了泄漏功率、材料系數與溫度的耦合關系的前提下, 將整體本構矩陣分解為常數矩陣和溫變矩陣的乘積, 使得在每次溫變迭代過程中只需計算溫變矩陣.對比傳統FEM 中的單元傳熱矩陣, 改進DCM 的溫變矩陣擁有更低的階數, 在計算量和整體矩陣的組裝上有著顯著優勢.通過仿真驗證了在相同自由度下, 改進DCM 比傳統FEM 具有更快的計算速度.最后面向三維集成微處理器系統基于改進的DCM 對其進行了電熱耦合分析, 并根據分析結果進行布局優化指導, 對三維集成微系統的設計優化具有一定的參考價值.

2 改進的DCM 算法

2.1 DCM 原理

對偶單元法是一種基于傳統FEM 發展的代數方法, 通過FEM 的網格剖分, DCM 可以不通過微分方法而直接根據問題的物理場以及基本的幾何和拓撲概念定義數值方案, 從而該算法更適用于實現快速計算[17,18].DCM 首先通過網格剖分得到初始單元, 并根據規則構造對偶單元.之后通過單元對應關系及本構關系分別構造拓撲矩陣和本構矩陣, 最后組成線性方程組進行求解.

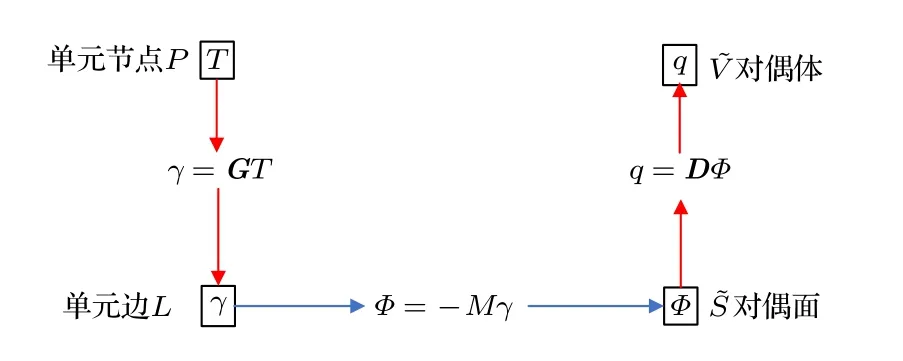

DCM 求解傳熱問題的計算流程如圖1 所示,單元節點上的溫度T通過拓撲算子矩陣G表示成單元邊上的溫差γ.然后通過本構關系利用溫差計算出對偶面上的熱通量Φ, 最后再將熱通量通過拓撲算子矩陣D轉化成對偶體上的整體發熱量q.

圖1 DCM 求解傳熱問題流程圖Fig.1.Flow chart of DCM solving heat transfer problem.

如圖2 所示, DCM 根據四面體單元的重心、4 個面的重心和6 個邊中點的連線構建對偶空間[19,20].在單個四面體中, 每條邊對應著一個對偶面, 如e2 對應S2, 每個頂點對應三個對偶面, 如A對應S2,S3,S6.在單個頂點接觸的所有四面體中, 對應該點的所有對偶面構成對偶單元.

對于傳熱問題的研究, 首先定義節點溫度列陣T, 獲得以節點溫度之間的差值作為邊ei的溫差列陣.溫差列陣γ可表示為

同時兩個節點間的溫差γ也可以由單元溫度梯度g和邊向量L表示:

根據傅里葉定律, 熱通量Φ的表達式為

其中k為熱導率;J為熱流密度;表示對偶面的面積向量, 方向垂直于對偶面.結合(1)式、(3)式和(4)式可得四面體內部對偶面的熱通量矩陣Φ為

圖2 對偶單元構建過程Fig.2.The process of dual unit construction.

其中P為為邊矩陣的分塊陣;M為傳熱問題的本構矩陣.

對于整體網格來說, 將所有對偶面上的熱通量相加即為整體節點載荷列陣q:

D為拓撲矩陣G轉置的負矩陣即D=?GT.結合(1)式、(5)式和(6)式可得整體傳熱方程為

2.2 改進的DCM 耦合分析

隨著功率密度不斷增加, 芯片的整體溫度不斷上升, 所以對溫度上升導致的耦合分析變得至關重要.

由下式可知泄漏功率與泄漏電流成正比, 其中泄漏電流Ileak分為亞閾值泄漏電流Isub和柵極泄漏電流Igate:

其中柵極泄漏電流Igate對溫度并不敏感.

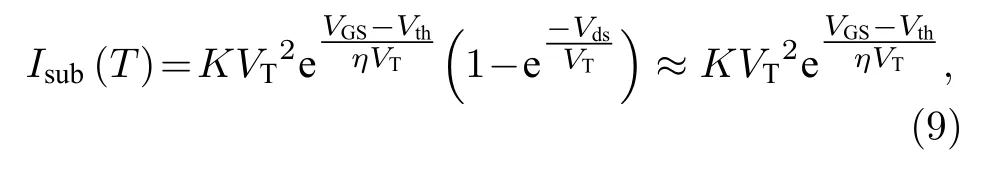

對于BSIM 4 的MOSFET 晶體管模型, 其亞閾值電流公式為(Vds?Vt)

其中K和η為相關工藝參數;VT為熱電壓, 與溫度成正比;Vth為閾值電壓.

另外, 材料的熱導率是與溫度相關的函數, 同時材料的溫度變化可以通過溫度的插值函數表示,可得熱導率公式如下:

其中cn為插值系數, 具體數值參考文獻[4,10].

引入耦合項Isub(T) ,k(T) 后, (7)式的整體傳熱方程可改寫為與溫度相關的形式:

由(11)式可知, 在每次溫度迭代計算時, 需要重新計算每個單元的本構矩陣M(k(T)) 和載荷列陣q(Isub(T)) 并重新組裝.對于DCM, 每個單元本構矩陣M為6 × 6 的矩陣, 相比于有限元4 × 4的傳熱矩陣K計算量更大, 組裝時間更長.因此本文對DCM 的整體傳熱方程做了進一步的改進.(5)式中的本構矩陣M(k(T)) 可以分解為

由(1)式可知在一個四面體單元中通過任意三條邊的溫差γ1,γ2,γ3可以計算得到另外三條邊的溫差.同時由(3)式可知, 求解列矩陣g3×1所需要的條件為矩陣L滿秩, 所以只需要三個互不相關的邊向量即可表示列陣g3×1

為了滿足本構矩陣M的維度, 溫差列陣γ可以由三個溫差與三個0 元構成, 邊矩陣L可由三個邊向量和3 × 3 的零方陣表示:

此時矩陣P為有效數據減少為9 個.梯度陣g可表示為

最終可得整體傳熱方程為

基于野外調查,按代表性植被的分布在三處邊坡中選取草本植被、草灌植被、草灌喬植被各兩個樣地,樣地大小按1 m2(草本植被)、10 m2(草灌植被)和100 m2(草灌喬植被)設置,以S形在同一樣地內采取5個樣品。采集0~10 cm土層原狀土,裝入鋁盒內帶回實驗室,風干后,沿土壤自然結構面人工剝成直徑為10~12 mm的小土塊,并剔除土中的植物根系及小石粒。

算法的整體耦合迭代流程如圖3 所示, 首先根據劃分的網格信息計算拓撲矩陣GS和G, 根據給定的初始溫度計算初始狀態下的亞閾值泄漏電流和熱導率, 并帶入計算本構矩陣Pk(T) 和節點載荷q(Isub(T)).下一步將本構矩陣和載荷帶入傳熱方程計算出該迭代步的溫度場分布Tnew.根據計算的溫度場更新本構矩陣和節點載荷, 并帶入傳熱方程計算新的溫度場分布, 直到兩步迭代的結果小于設定的迭代截止精度tol.

圖3 迭代算法流程圖Fig.3.Flow chart of Iteration scheme.

3 模型驗證與分析

本節采用改進的對偶單元法研究三維集成微處理器系統在耦合情況下的溫度分布, 討論不同I/O 端口和TSV 陣列布局對疊層芯片熱點溫度的影響.圖4 所示為參考三星DRAM 和Intel i7 處理器芯片構成的兩層堆疊微系統結構示意圖[21].兩層芯片的尺寸均為10 mm × 10 mm, 襯底的尺寸為20 mm × 15 mm, 熱沉的尺寸為40 mm ×35 mm.芯片層的厚度為100 μm, 帶C4 凸塊的TIM 層厚度為100 μm, 帶微凸塊的TIM 層厚度為40 um.初始溫度和環境溫度為293 K, 熱對流系數為100 W·m–2·K–1.DRAM 和處理器的版圖布局如圖5 所示, 其中DRAM 被分為8 個Bank 區,處理器芯片由4 個Core 構成(從左到右分別記為Core1, Core2, Core3, Core4).在DRAM 芯 片 的I/O 區域中均勻分布了16 × 80 個TSV.為了能直觀表征Core 區和Bank 區的溫度, 選取如圖5中所示的黑色虛線為觀察芯片溫度分布的基準線.根據DRAM 和處理器的典型工作狀態, 本文在仿真中將DRAM 的工作功率設為2.82 W, 處理器工作功率設36 W, 其中四個核的總功率為26.5 W,整個微系統泄漏功率占比為12%[3,21].

圖4 三維集成微處理器系統結構示意圖Fig.4.Schematic diagram of the three-dimensional integrated microprocessor system.

3.1 改進的DCM 準確性驗證

在保證精度的前提下為了降低仿真復雜度, 采用等效模型法對TSV 陣列進行了等效處理, 通過插值法獲得等效區域各向異性的熱導率[22].當處理器4 個核心功率均勻分布時, 處理器和DRAM芯片上觀察基準線上的溫度分布分別如圖6 所示.當不考慮電熱耦合時, FEM 求解得出的處理器和DRAM 芯片的熱點溫度分別為351.83 K 和346.64 K, DCM 求解得出的處理器和DRAM 芯片的熱點溫度分別為351.83 K 和346.63 K.改進的DCM 與FEM 獲得的溫度曲線幾乎完全吻合,有著良好的一致性.在考慮電熱耦合時, 發現用改進的DCM 與FEM 仿真得到的處理器芯片與DRAM 芯片的熱點溫度為分別為373.64, 374.07 K和365.87, 366.24 K, 改進的DCM 仿真相比于傳統FEM 誤差僅為0.53%和0.51%(仿真后溫度與初始溫度的差值進行誤差計算, 下文同), 其精度滿足應用要求.

圖5 工作區域分布圖 (a) DRAM 芯片; (b) Intel i7 處理器芯片Fig.5.Work area distribution map: (a) DRAM; (b) processor.

圖6 不考慮耦合與考慮耦合時芯片溫度分布 (a) DRAM; (b) 處理器Fig.6.Chip temperature distribution without considering coupling and considering coupling: (a) DRAM; (b)processor.

對比考慮電熱耦合前后的仿真結果, 發現在考慮電熱耦合因素之后兩個芯片的平均溫度均提高了約20 K.這是因為隨著工作溫度的上升, 芯片泄漏功率急劇增大, 這使得芯片發熱量進一步增大,形成溫度正反饋循環, 這是影響三維集成微系統工作溫度的主要因素.同時材料的熱導率會隨著溫度的升高而降低, 使得結構的導熱性能變差, 從而使得溫度再度升高, 因此在三維集成微系統的設計過程中, 綜合考慮電熱耦合對系統可靠性的影響是十分必要的, 否則存在低估系統工作溫度的風險.

表1 FEM 與改進DCM 的仿真時間對比Table 1.Simulation time comparison between FEM and improved DCM.

3.2 三維集成微系統的布局分析

圖7 兩種不同的TSV 陣列布局 (a) 常規布局; (b) Core-布局Fig.7.Two different TSV array layouts: (a) Conventional layout; (b) core layout.

在三維集成電路中, 由于具有高熱導率的TSV陣列是溫度傳導的重要路徑, 因此I/O 端口中的TSV 陣列常被作為重要的散熱手段, 而TSV 陣列的Core-布局方式通常被認為能夠有效的降低系統的熱點溫度[23].Core-布局的具體布局方式如圖7(b)所示, 即將DRAM 芯片中I/O 區域的TSV 陣列布局位置對應上層處理器芯片4 個Core 的位置.在以往的研究中采用Core-布局結構的上下層芯片功率相近, 使得兩層芯片的溫度變化連續, 因此能夠使得上下層芯片的熱點溫度同時下降[23,24].而本文所考察的微處理器系統工作狀態中處理器功率遠大于DRAM 的功率, 并且上下層芯片的熱點溫度相差接近8 K, 因此有必要重新評估Core-布局的可行性.

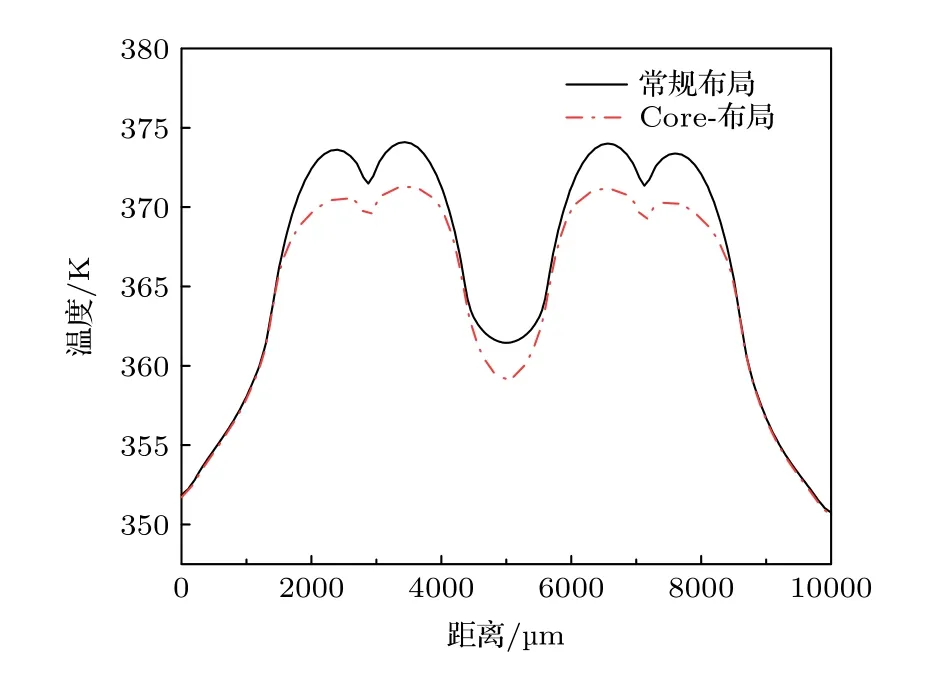

為了比較兩種布局的溫度分布, 首先將處理器的四個Core 功率設置為均勻分布, 采用改進的DCM 對兩種布局結構進行電熱耦合仿真分析.如圖8 所示采用Core-布局結構時, 處理器芯片的熱點溫度下降了2.20 K.而與此同時圖9 所示DRAM芯片的熱點溫度為370.93 K, 相比3.1 節仿真得到的常規布局熱點溫度上升了4.30 K.這是由于TSV陣列作為重要散熱路徑, Core-布局結構會將處理器高功率Core 區域產生的熱量傳導到下層, 使得處理器芯片溫度下降的同時讓DRAM 芯片的整體溫度上升.對比TSV 陣列常規布局的情況, Core-布局使得處理器芯片熱點溫度下降2.73%, 而使得DRAM 芯片的熱點溫度上升5.85%.考慮到高溫會導致DRAM 的晶體管電荷損失加快, 使得數據丟失.因此在選擇布局方式時, 需要綜合考慮處理器芯片的降溫情況與DRAM 芯片的升溫情況.

圖8 兩種不同TSV 陣列布局時處理器的溫度分布Fig.8.Temperature distributions of processors with two different TSV arrays.

圖9 Core-布局時DRAM 溫度分布圖Fig.9.DRAM temperature distributions in core-layout.

表2 不同功率分配時仿真時間Table 2.Improving simulation time of DCM and FEM with different power allocation.

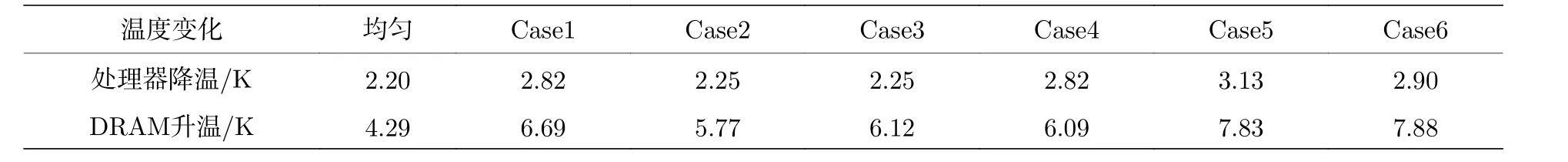

表3 不同功率分配下Core-布局相比于常規布局的芯片溫度變化Table 3.Chip temperature change of core layout compared with conventional layout under different power allocation.

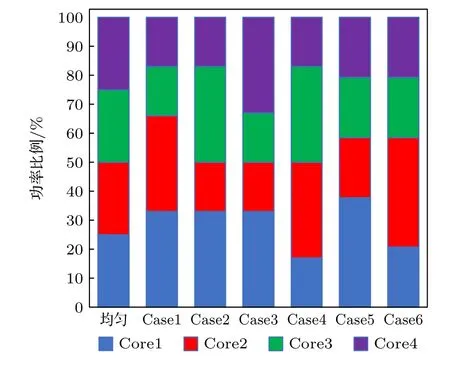

在實際工作中, 多核處理器芯片在執行事務時各個Core 會工作在不同功率下, 因此有必要結合不同的Core 功率分配情況, 對兩種布局結構的熱分布對功率配比的敏感度進行分析.圖10 給出了幾種典型的Core 功率分配情況, 4 個Core 的總功率值保持為26.5 W, 其中Case1 為大功率事務集中在單側兩個Core, Case2 為大功率事務交錯分布, Case3 為大功率集中在外側Core, Case4 為大功率事務集中在中間兩個Core, Case5 為外側單個Core 大功率工作, Case6 為內側單個Core 大功率工作.

基于本文所提出的改進DCM 對不同功率分配情況下的DRAM 和處理器芯片的熱點溫度進行了統計分析.幾種情況仿真時間如表2 所列, 在對兩種布局的仿真分析中, 改進的DCM 與傳統FEM相比仿真速度提升了約30%.

結合圖11 和圖12 的統計結果, 發現處理器芯片在內側核高功率的Case6 下熱點最高, 功率均勻分配時熱點溫度最低.DRAM 芯片在Case1 下的熱點溫度最高, 功率均勻分配時的熱點溫度最低.由此可見在Core 功率分布不均勻時會加劇熱點問題, 因此處理器工作時應盡量保持各核功率分布均勻能有效降低整個微系統的熱點溫度.同時發現單側兩個Core 處理大功率事務的Case1 以及單核處理大功率事務的Case5, Case6 情況下, 整個微系統的熱點溫度均會顯著升高, 因此在系統設計時應盡量避免這種情況.

圖10 典型Core 功率分配情況Fig.10.Typical core power allocation.

在不同功率配比的情況下, TSV 陣列Core-布局對比常規布局的處理器芯片降溫與DRAM 芯片升溫情況如表3 所列.可以看出當Core 功率不均勻分布時, Core-布局對處理器芯片的降溫效果與功率均勻分布時相比有提升, 同時也加劇了DRAM芯片的升溫.比較功率均勻分布與降溫最多的Case5, 處理器芯片降溫效果提升了42.27%, 而DRAM 芯片的升溫上升了82.52%.因此Core-布局在功率不均勻分布時, DRAM 芯片會受到更大影響.在設計三維集成微處理器系統時, 若要降低整體系統的熱點溫度, 在采用Core-布局時需要考慮到DRAM 芯片能工作在容限溫度內.若要降低DRAM 芯片熱點溫度, 則需要將TSV 陣列即I/O端口布局在遠離Core 的區域.

圖11 不同功率分配下處理器芯片最高溫度Fig.11.Maximum temperature of processor chip under different power allocation.

圖12 不同功率分配下DRAM 芯片最高溫度Fig.12.Maximum temperature of DRAM chip under different power allocation.

4 總 結

本文針對三維集成微系統的電熱耦合問題提出了一種改進的DCM 算法.基于三維集成微處理器系統對所提算法進行了仿真驗證, 并對微系統的布局設計、功率分配進行了分析討論.研究表明:本文提出的改進DCM 能快速準確地對三維集成微系統實現建模計算, 在分析電熱耦合問題方面具有顯著的時間優勢; 在考慮電熱耦合因素后, 微系統泄漏功耗上升, 材料熱導率下降, 熱點溫度對比耦合前上升約20 K, 表明了對三維集成微系統進行電熱耦合分析的必要性; 在微系統布局設計方面, TSV 陣列的Core-布局雖然能夠降低處理器芯片的熱點溫度, 但卻同時惡化了DRAM 芯片的熱點問題, 在Core 功率不均勻分配時影響尤為嚴重.因此在系統設計時, 要綜合考慮處理器和DRAM芯片的容限溫度來確定TSV 陣列布局方案.綜上所述, 本文提出的算法能快速分析三維集成微系統的電熱耦合問題, 實現系統熱點預測, 為微系統芯片布局設計提供理論指導.