一種高動態長偽碼信號的捕獲方法*

李 程

(中國電子科技集團公司第五十四研究所,河北 石家莊 050081)

關鍵字:PMF-FFT;折疊匹配濾波器;高動態;長偽碼捕獲

0 引言

衛星通信以其全天候、廣地域和高靈活性在軍民領域中均得以廣泛的應用。但是衛星通信系統鏈路環境較為復雜多變,特別是在高動態條件下,鏈路上的多普勒頻移導致信號的捕獲和跟蹤難度較大,這也一直是工程研究的熱點和難點。在低速通信中,常結合擴頻通信整體設計,這樣可以提升其抗干擾能力和高可靠性,降低實現難度。目前擴頻通信中較為成熟的捕獲算法有滑動相關算法、匹配濾波算法以及基于FFT的捕獲算法等,部分匹配濾波-快速傅立葉變換(Partial Match Filter Fast Fourier Transform,PMF-FFT)是最近研究的熱點,主要用于捕獲高動態長偽碼信號,其捕獲用時較短、捕獲頻偏范圍較寬。PMF-FFT算法多用FPGA實現,對邏輯資源和RAM資源消耗量也較大,特別是當擴頻信號的偽碼長度較長或多普勒頻偏過大時,會導致硬件資源占用過多而不可實現。本文論述一種PMF-FFT實現方法,通過非相干累積和匹配濾波器組的折疊,優化了資源使用率,實現了高動態長偽碼信號的捕獲。通過仿真和測試,捕獲概率為99%時,捕獲時間小于1 s。

1 PMF-FFT算法分析

假設信號碼長為N,多普勒頻差為?f,碼寬為Tc,若對此信號實現捕獲,此時的歸一化相關輸出值為[1]:

式中,r(k)為接收信號;c(k-n)為本地偽碼;?(φ)為接收相差。

當r(k)與c(k-n)對齊時,?(φ)=0,r(k)c(k-n)=1,則式(1)可表示為:

部分匹配濾波算法是將式(2)中長為N的匹配濾波器分成K段長為M的部分匹配濾波器(N=K×M),可得出:

對K段部分匹配濾波器輸出的相關值進行K點FFT運算,輸出結果中第k點的歸一化幅頻響應為:

若k點FFT結果取模之后的峰值大于判決門限,則捕獲成功,FFT估計的載波頻差為接收端需要補償的頻差值[2]。對固定的?f,比較這K個GPMF-FFT(k,?f)的函數值,可得捕獲的相關增益A(?f)。

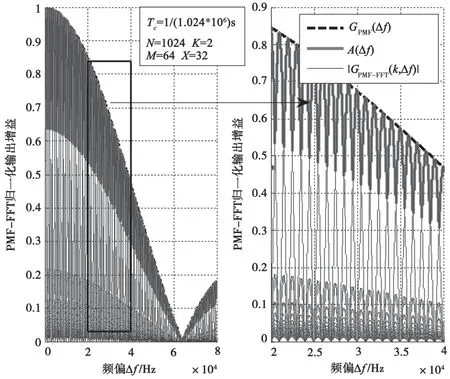

若擴頻信號信息速率Rb為1 kb/s,擴頻周期N為1 024,采樣因子K為2,M為128,則碼片速率Rc=1.024 Mb/s,碼片周期Tc=1/Rc,部分匹配濾波器級數X=KN/M=16,則在偽碼同步時,PMF-FFT算法的相關增益如圖1所示。

捕獲輸出的歸一化增益在0~8 kHz范圍內并沒有隨著頻偏的增加而急劇下降,在系統頻偏過大時,PMF-FFT算法不會因為相關增益過低導致相位漏檢,即系統的頻偏搜索范圍變大。由此可得,PMF-FFT算法能夠解決大頻偏問題。

在PMF-FFT捕獲算法中,部分匹配濾波器的長度需慎重考慮,不可過大或過小[3]。部分匹配濾波器的長度過大會導致捕獲帶寬變窄,長度過小會導致FFT點數過多,導致FFT計算量過大,資源占用和計算延時增加,因此須合理平衡匹配濾波器的長度和FFT點數。由式(5)可知,接收信號與本地偽碼的相關增益會受到部分匹配濾波器的頻率響應GPMF(k,?f)的影響。當頻偏很大時,相關增益衰減十分明顯。圖2是M=64,32階濾波器時PMFFFT輸出的相關增益。

從圖2可知,基于PMF-FFT的捕獲算法對頻偏的搜索范圍是有限的。因此在進行匹配濾波器長度設計時,要合理計算頻偏搜索范圍,同時保證正常捕獲。

算法處理流程如圖3所示。信號Rx經過預處理產生I、Q兩路信號,送入匹配濾波器組進行相關運算,每個濾波器組由相關器和M階累加器組成,I、Q兩路數據先相關再累加生成n個數據,將累加結果送入N(N≥n)點FFT模塊進行運算,將輸出結果與預設門限進行判決,若輸出結果高于門限,則表示成功捕獲[4],通過捕獲的相位位置計算可得出系統頻差。

圖1 PMF-FFT捕獲算法輸出增益

圖2 PMF-FFT輸出增益

圖3 算法處理流程

本文中擴頻信號偽碼長度為40 800,碼速率為2.5 Mc/s,頻偏范圍為±20 kHz。如圖4所示,經過仿真計算,若需捕獲概率大于99%,部分匹配濾波器長度為256,FFT點數為256。

圖4 基于PMF-FFT的捕獲仿真結果

下面給出具體的實現方法。

2 算法實現

2.1 PMF部分實現

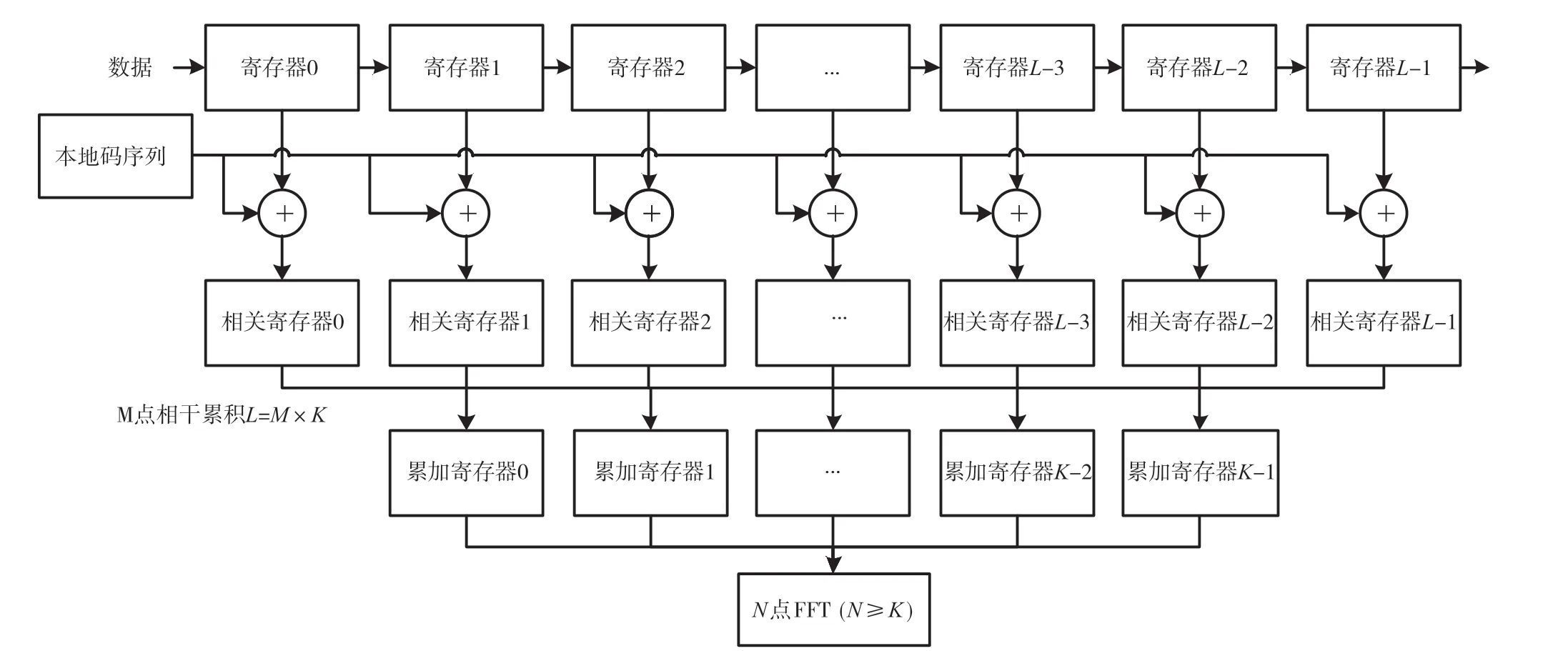

常規方法的部分匹配濾波器實現過程如圖5所示,處理過程需要L級數據寄存器、L級相關寄存器和K級累加寄存器。

部分匹配濾波器長度為256,FFT計算點數為256點,需要緩存的點數為256×256=65 536點,按照輸入數據2 bit量化,2倍采樣計算,若使用常規的PMF-FFT算法,其數據寄存器和相關寄存器使用量為524 288 bit。以Xilinx的XC7VX690T型號FPGA為例,其邏輯資源為693 120,已經占據其75%的邏輯資源,綜合資源使用情況,難以實現算法。

圖5 常規PMF實現流程

本文參考一種折疊匹配濾波器[5],如圖6所示,通過RAM資源與邏輯資源的優化互換,將待運算數據和碼字序列緩存于RAM中,將匹配濾波器組折疊,使用流水線思想,多級復用,使用高速時鐘處理低速數據,減少了近一半寄存器的使用。具體實現流程如圖7所示。

圖6 基于RAM的折疊匹配濾波器實現流程

圖7 RAM存取數據流程

例化8個寬度為512,深度為32的RAM,用于存儲輸入數據。在碼周期開始后,RAM地址由0開始,累加至31,每次讀出的數據既要用于相關運算,還需要將其低510 bit與上一地址高2 bit(0地址為輸入數據)拼接,再次寫入本地址中。實現在每個碼周期讀一次數據,更新一次數據。

例化8個寬度為256,深度為32的ROM用于存儲折疊的偽碼序列,ROM地址操作與RAM一致。地址變換的同時,ROM輸出本地偽碼與RAM輸出的緩存數據進行一次相關運算,將結果放入寄存器中進入流水線處理。由于延時固定,流水線會在不同時刻輸出對應點的累加結果,將其緩存后給FFT模塊使用,如圖8所示。

單倍采樣的碼時鐘為2.5 Mc/s,工作時鐘為150 MHz,倍數相差60倍。此種折疊匹配濾波器進行了32級折疊,考慮RAM讀寫和流水線處理延時,足以在60個時鐘周期內完成一次PMF運算。

2.2 FFT部分實現

FFT處理模塊需要對部分匹配濾波器輸出的256個樣點進行運算,由于工作時鐘為單倍采樣碼片鐘的60倍,而256點FFT的處理延時約為600個時鐘周期,因此需要多路FFT并行處理,采用10個FFT模塊同時工作,處理流程框圖如圖9所示。

經過累加輸出的256樣點數據通過寄存器進行緩存,通過數據選擇器依次輸入FFT模塊進行運算,對FFT輸出的數據取模值后與門限進行判決,當模值的峰值高于門限時,則成功捕獲,此時FFT峰值點位置的歸一化頻偏則為載波頻差,本算法載波頻差估計的范圍為:

即捕獲頻偏范圍為±4.88 kHz,分辨精度為:

即經過頻差補償后殘留的頻差最大值為38 Hz。

針對捕獲算法需要滿足初始高動態頻偏的方案設計如下:頻偏范圍-20~20 kHz,采用4路并行工作的方法,每個偽碼初始位置時進行一次捕獲,為實現可靠捕獲,進行3次捕獲運算,捕獲概率大于99.999 9%,最長捕獲時間小于1 s。

圖8 PMF模塊處理流程

圖9 FFT模塊處理流程

3 結語

PMF-FFT算法廣泛運用于高動態長偽碼擴頻信號的捕獲中,但是其資源占用量也相對較多。本文簡要分析了PMF-FFT的算法原理,從工程應用的角度闡述了一種優化的PMF-FFT實現方法,通過對部分匹配濾波器組長度的折疊,有效減少了對芯片邏輯資源的使用。本方法已經在工程項目中應用,性能良好,工作穩定可靠。