北斗三號射頻芯片中Σ-Δ調制器電路設計

董明月,黃海生,李 鑫,楊 毅

(西安郵電大學 電子工程學院,西安 710121)

0 引言

北斗衛星導航系統(BeiDou navigation satellite system,BDS)是我國著眼于國家安全和經濟社會發展需要,自主建設運行的全球衛星導航系統(global navigation satellite system, GNSS),北斗三號全球衛星導航系統即北斗三號(BeiDou-3 navigation satellite system, BDS-3)的開通,標志著我國完成了三步走的發展戰略。BDS射頻芯片是BDS應用的基礎,射頻芯片中鎖相環頻率合成器的作用是產生本振信號,鎖相環的輸出頻率如果出錯,會導致整個射頻芯片出現異常,故鎖相環產生的頻率信號準確與否,對射頻芯片十分關鍵[1]。由于環路的眾多指標均受鎖相環反饋部分的分頻器影響,而小數分頻器的使用,會出現小數雜散,降低電路性能。所以,本文研究設計加入Σ-Δ調制器,以解決小數雜散,但加入調制器后,不僅會產生結構寄生,還會使調制器的輸出頻譜噪聲變高,因此有必要設計加入成型處理的抖動電路,解決調制器產生的結構寄生及輸出頻譜噪聲變高的問題。

1 小數分頻器原理

1.1 鎖相環基本原理

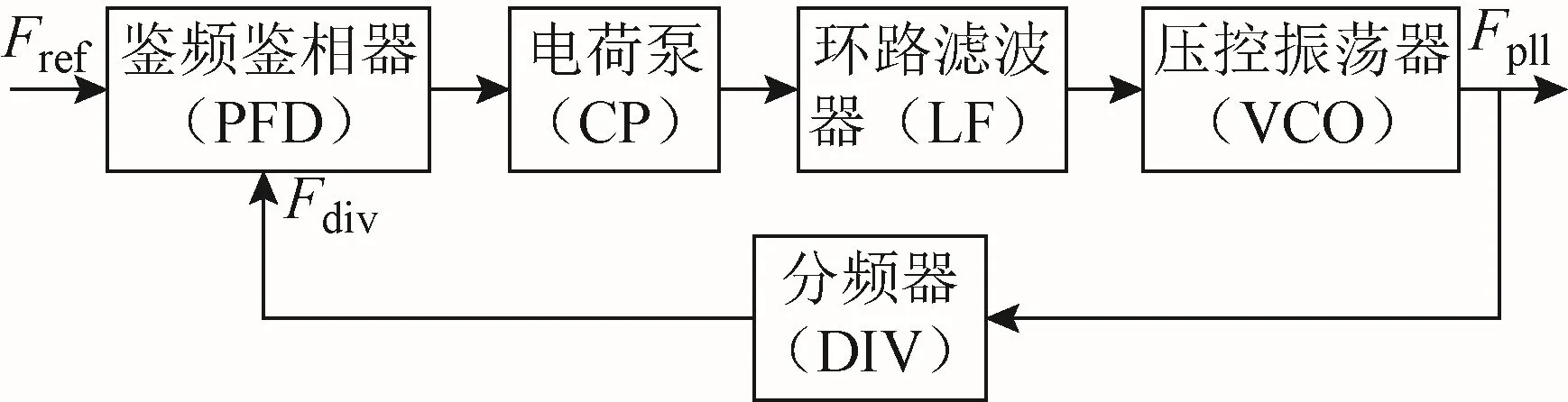

傳統鎖相環是由鑒頻鑒相器(phase frequency detector,PFD)、電荷泵(charge pump,CP)、環路濾波器(loop filter,LF)、壓控振蕩器(voltage controlled oscillator,VCO)和分頻器(divider, DIV)5個基本模塊組成的反饋系統,如圖1所示。

圖1 鎖相環結構

鎖相環電路的工作原理為:輸入的參考頻率與環路反饋給分頻器后的分頻結果,通過鑒頻鑒相器進行對比并產生脈沖信號,該信號將作用于電荷泵,完成對環路濾波器中的電容充放電,從而通過環路濾波器產生輸出電壓,對壓控振蕩器進行控制,進而產生鎖相環的最終輸出。由于BDS載波頻率與晶振頻率之間非整數倍關系,所以此處需要設計一個小數分頻器。表1列出了BDS-3B1I、B1C、B2a、B2b、B3載波中心頻率,與中頻頻率為3.996 MHz、輸入的參考頻率為16.369 MHz時對應的分頻比(取小數點后4位)。

表1 BDS-3載波中心頻率及對應分頻比

1.2 小數分頻器結構

數字電路在實現小數分頻時采用平均的方法,小數分頻器的每個瞬時是整數分頻,但這將導致分頻器輸出的瞬時頻率與參考頻率間存在相位差,致使PFD產生鋸齒形的相位誤差,誤差通過環路濾波后作用于VCO[2],使其輸出產生雜散。為了使小數分頻器的頻譜純度及性能盡可能好,需要處理小數雜散,Σ-Δ調制技術[3]是常用的處理小數雜散的方法。Σ-Δ調制技術通過在小數分頻鎖相環中加入一個Σ-Δ調制器,運用調制器自身特性,將小數雜散轉為量化噪聲[4],并將噪聲整形到高頻段,再利用鎖相環本身對輸入噪聲呈現的低通濾波性將其濾除。這種方法可以從本質上消除小數雜散帶來的影響,且易于實現。

Σ-Δ小數分頻器[5]的結構框圖如圖2所示。

圖2 Σ-Δ小數分頻器結構

Σ-Δ小數分頻器由N/ (N+ 1 )雙模分頻器、Ncount分頻器和Σ-Δ調制器三部分組成。其中,Mod為Ncount分頻器反饋給雙模分頻器的分頻模控制信號;Fvco為VCO的輸出頻率;Fpre為N/ (N+ 1 )雙模分頻器的輸出頻率;Fdiv為小數分頻器的整體輸出;Ndiv為調制序列與整數分頻比之和;Nsig、Σ-Δ分別為調制器輸出的調制序列;Nint和Nfra分別為預期小數分頻比的整數和小數部分。

Σ-Δ小數分頻器的工作原理為:輸入的小數值作用于Σ-Δ調制器后產生調制序列,調制序列通過與輸入的整數值求和后輸入到Ncount分頻器中,Ncount分頻器根據輸入的分頻比,對雙模分頻器的輸出頻率再進行分頻,進而產生小數分頻器的最終輸出頻率。

2 MASH 1-1-1型 Σ-Δ調制器

對Σ-Δ調制器進行如下分析:由于一階調制器[6]在鎖相環電路的應用過程中,雖能在一定程度上起到對量化噪聲的整形效果,但是低頻區仍存在量化噪聲,故在電路中一般不采用一階調制器,而是采用對其進行改進的調制器:將一階調制器級聯到馬什(MASH)型的Σ-Δ調制器,會將每級累加器產生的量化誤差傳遞到下一級,需要對量化誤差進行二次量化處理,即采用足夠多的級數,將量化噪聲完全推至高頻段的目的[7]。但是多級級聯的Σ-Δ調制器,需要等階數LF的匹配作用才能達到效果,LF設計復雜,且使用韋里洛格·得赫爾(Verilog HDL)實現的高階Σ-Δ調制器,占用的邏輯資源較多,因此并不是級數越多越好。在實際應用過程中,小數分頻鎖相環常以采用 4級以下的Σ-Δ調制器為主,但低級Σ-Δ調制器又不能將有用頻帶內的所有量化噪聲推到高頻段,故小數分頻鎖相環多采用3級級聯調制器[8],即為MASH 1-1-1型Σ-Δ調制器。

2.1 調制器結構寄生產生的原因

對于MASH 1-1-1型Σ-Δ調制器,在輸入小數值時,大部分的輸出序列均具有良好的隨機性,輸出序列頻譜曲線平滑;而對于某些特定值,調制器輸出序列頻譜則會表現出強周期性,具體表現為,在固定頻點處出現毛刺,這種現象被稱為調制器的結構寄生。

MASH 1-1-1型調制器的輸出序列,總有固定的周期性[9],可將 MASH 1-1-1型調制器看作一個有限的狀態機,其輸出結果的狀態跳轉由輸入值和現態決定,且輸出值在固定狀態間相互轉換。Σ-Δ調制器每一級最小周期的表達式如表2所示。

表2 Σ-Δ調制器每1級最小周期表達式

表 2中:M為量化器的模值;A為輸入值;m1[ 0]為第一級調制器的現態;m2[0]為第二級調制器的現態;GCD為求A與M最大公約數的運算符。由每一級最小周期的表達式可以看出,第二級調制器的最小周期L2受第一級調制器輸出值的奇偶特性影響,并與輸入值A以及量化模值M有關;第三級調制器的最小周期L3受第二級調制器輸出值影響。

基于表2進行分析:在三級調制器均不設初值且輸入值為奇數時,可以算得L2=L3=2L1,L1= 2a;當輸入值為偶數時,L2=L3=2L1,L1= 2a-b。由此得到調制器的輸出周期受輸入值A的影響較大,且輸入值為偶數的輸出序列較短,表現為高頻時固定頻點極高的頻譜線,即出現結構寄生現象。經過在先進設計系統(advanced design system, ADS)軟件上進行多次仿真發現,結構寄生在A=0.25時尤為明顯。

2.2 調制器結構寄生解決方案

MASH 1-1-1型調制器在輸入為偶數且各級不設置初值時,會出現結構寄生問題,鑒于其對射頻系統的影響,需采取一定的措施對調制器的結構寄生問題進行處理,如隨機性方案[10]。通過給調制器加入一個隨機的抖動,打破調制器的固有周期,此種方案通過給調制器外接抖動電路實現,電路較簡單。

3 抖動電路

3.1 抖動電路的成型處理

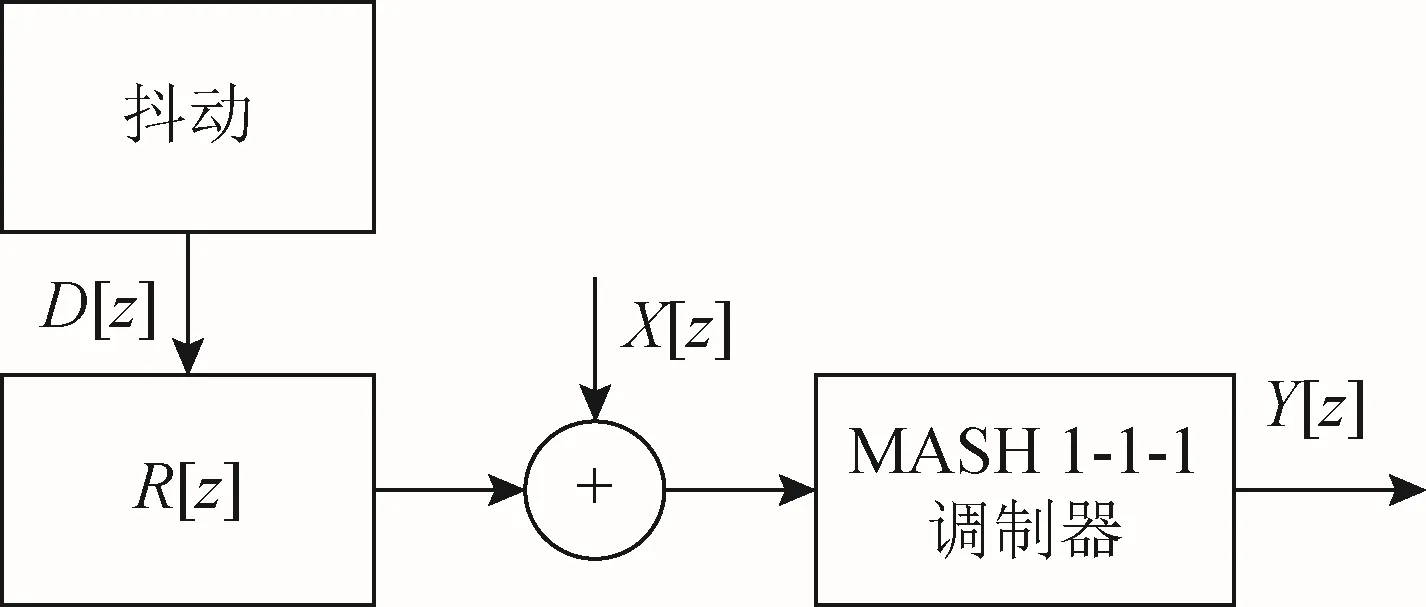

調制器結構寄生問題可通過加抖動解決,但偽隨機序列的加入,會導致調制器的輸出頻譜噪聲變高,為解決此問題,可通過對輸入的抖動做成型處理,結構圖如圖3所示。

圖3 抖動成型處理結構圖

圖3中:R[z]是成型處理電路;C為階數。傳輸函數為

根據 MASH 1-1-1調制器的傳遞函數[11]及式(4)可得,加入抖動和成型處理電路后的調制器傳遞函數Y[z]為

式中:X[z]為輸入數值;D[z]為經過成型處理后的抖動;Eq3(z)為量化噪聲。從式(5)可以看出,經過成型處理后的抖動D[z]類似于量化噪聲被整形到了高頻段。

3.2 新映射方法的采用

為了抑制抖動電路引入的帶內噪聲,需要對抖動電路做成型處理,R[z]的階數越高,越能抑制抖動電路引入的帶內噪聲,但是R[z]的階數過高,會導致其占用過多資源,因此在設計電路時,采用改變序列映射過程的方法,來實現抖動電路的成型處理。

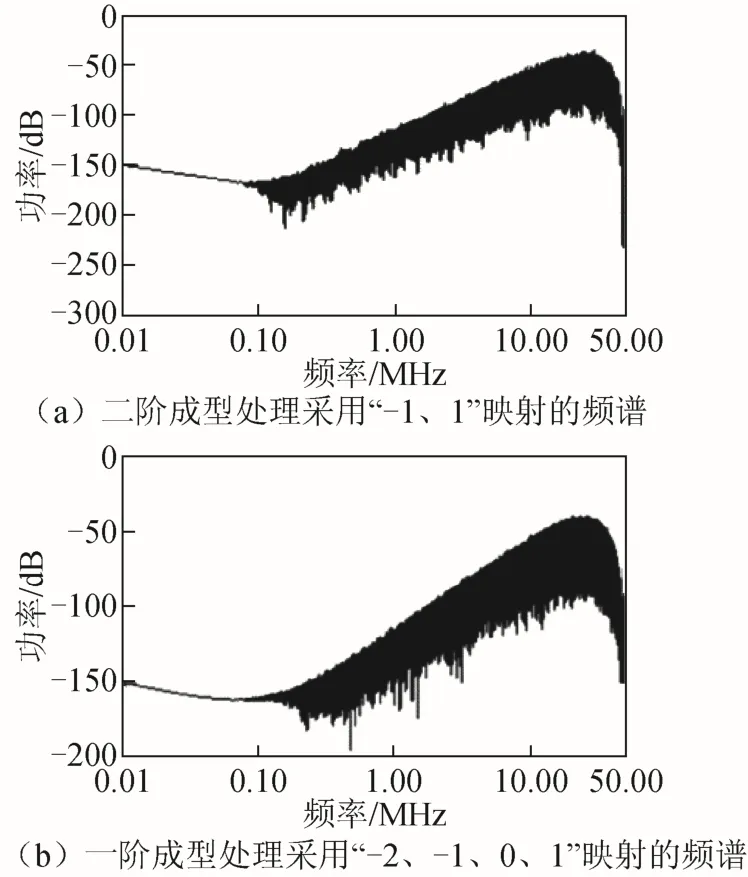

對抖動電路產生的m序列做成型處理的做法,是將m序列輸出的0和1映射成“-1、1”。現對映射進行改進,選取24階m序列中3個移位寄存器(Reg)的輸出,將其映射為“-2、-1、0、1”,然后采用一階R[z]做成型處理,改動示意圖如圖4所示。

圖4 采用新映射方法的抖動電路

采用小數分頻比為0.125 1、0.626 5、0.501 4和0.251 1對比新舊兩種映射方法。首先,將ADS軟件中的小數值設置為0.125 1、0.626 5、0.501 4和0.251 1,然后分別采用“-1、1”映射和“-2、-1、0、1”映射,對m序列二階成型處理和一階成型處理進行仿真,仿真結果如圖5至圖8所示。

圖5 小數為0.125 1時調制器輸出序列的頻譜

圖6 小數為0.626 5時調制器輸出序列的頻譜

圖7 小數為0.501 4時調制器輸出序列的頻譜

圖8 小數為0.251 1時調制器輸出序列的頻譜

從圖5至圖8可以看出,使用改進后的新映射方法,進行一階成型處理的結果與原映射方法進行二階成型處理的結果相比較,改進后的結果更好。

3.3 電路建模仿真

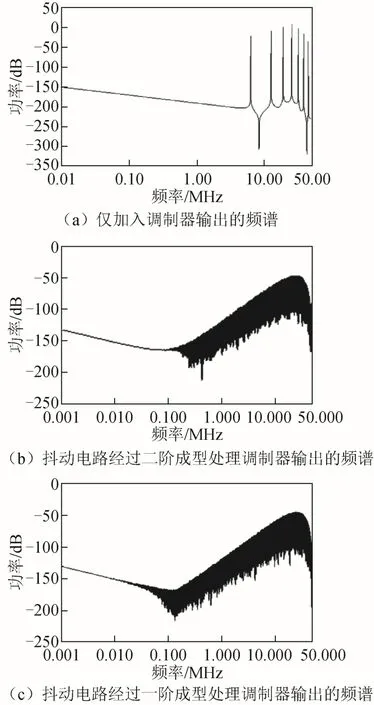

由于A=0.25時結構寄生尤為明顯,分別對僅加入調制器,加入抖動電路的調制器,對抖動做成型處理的調制器進行仿真,結果如圖9所示。

圖9 小數為0.25時調制器輸出序列的頻譜

圖9(a)為僅在小數分頻器中加入調制器,可以看到,高頻時固定頻點出現極高的頻譜線,即結構寄生現象;圖9(b)為對抖動進行二階成型處理,采用“-2、-1、0、1”映射的調制器,可以看到結構寄生現象明顯得到了抑制;圖9(c)為對抖動進行一階成型處理,采用“-1、1”映射的調制器,可以看到結構寄生現象也明顯得到了抑制且比圖9(b)效果好。

4 電路實現與仿真驗證

4.1 MASH 1-1-1型調制器電路

一個寄存器和累加器構成一階Σ-Δ調制器。根據一階調制器的邏輯電路,可得MASH 1-1-1型調制器的電路結構[12]如圖10所示。

圖10 MASH 1-1-1型調制器邏輯電路

圖10中:虛線框中的噪聲整形電路和三個級聯的累加器構成 MASH 1-1-1調制器電路;s1[n]至s3[n]為各個寄存器的輸出;q1[n]至q3[n]為進位值;-e1[n]至 -e3[n]為調制器引入的量化噪聲。為保證電路時序同步且減少因延時產生的毛刺,在噪聲整形電路和累加器之間加入一級寄存器。根據圖8可以寫出z域表達式為

式中:Y(z)為調制序列;Q1(z)至Q3(z)分別為產生的進位值。根據式(6),寫出噪聲整形電路的時域離散函數為

將式(7)整理為F(n) =q1(n) +q2(n) +q3(n),T(n) =q2(n- 1 ) + 2q3(n- 1 ) +q3(n- 2 ),故電路實現時,先分別求F(n)與T(n),再求F(n)-T(n)。

4.2 抖動電路

抖動電路的設計采用24階m序列[13],使用新的映射方法,且對抖動電路的輸出進行一階成型處理,具體電路邏輯圖如圖11所示。

如圖11所示,成型處理電路和m序列產生電路構成抖動電路。且24階m序列的特征多項式為

圖11 抖動電路邏輯

4.3 仿真驗證

為驗證所設計 Σ-Δ調制器的性能,對電路在莫德爾西姆(Modelsim)軟件中進行仿真。由表1可知,BDS-3載波中心頻率對應分頻比分別為95.125 1,96,71.626 5,73.501 4,77.251 1。由于 96是整數,所以采用其余4個分頻比進行驗證。因為所設計的調制器累加器位數為20 bit,將輸入到電路中的小數部分進行轉換,B1I載波中心頻率對應分頻比的小數0.125 1表示為N_frac=20’d131176,B2a載波中心頻率對應分頻比的小數0.626 5表示為 N_frac=20’d656932,B2b載波中心頻率對應分頻比的小數0.501 4表示為 N_frac=20’d525756,B3載波中心頻率對應分頻比的小數 0.251 1表示為 N_frac=20’d263297,電路的行為級仿真結果如圖12所示。

圖12 小數分頻器的仿真結果

5 結束語

為解決小數分頻器產生小數雜散的問題,在小數分頻器中加入Σ-Δ調制器。另外,加入經過成型處理的抖動電路,解決了調制器產生的結構寄生及輸出頻譜噪聲變高的問題。其中,抖動電路采用新的映射方法。研究表明:Σ-Δ調制器的加入,有效地抑制小數雜散對鎖相環輸出頻率的干擾;經過成型處理且采用新映射方法的抖動電路,不但能抑制調制器本身結構寄生問題,還能降低抖動電路引入的噪聲對電路輸出結果的影響。可將此調制器用于BDS-3射頻芯片中,以改善芯片性能。