更低功耗、更高帶寬!LPDDR內存的過去和現在

李實

內存芯片的重要性在今天愈發凸顯,無論是PC還是手機、平板還是游戲主機,都無處不閃現著內存芯片的身影。不過,不同產品使用的內存往往存在一差異。除了我們常見的DDR、GDDR外,在移動設備上還存在著一種專用的低功耗內存,那就是LPDD。今天,本文就和你一起走近LPDDR內存,探尋這種專門面向低功耗市場的內存的過去、現在和未來。

LPDDR是目前廣泛使用在移動設備和低功耗設備上的內存產品。LPDDR的全稱是Low-Power DDRSDRAM,中文名稱是低功耗雙倍數據速率同步動態隨機存取存儲器。在一些文章中,LPDDR也被稱為mDDR也就是移動DDR,“m”的意思是“mobile”,這是針對其應用市場所提出的名稱。相比常見的DDR內存,LPDDR的特點是“LP”,也就是低功耗。因此它被廣泛使用在包括手機、平板電腦、低功耗設備等對功耗比較敏感的場合。除了功耗外,LPDDR相比DDR,還在芯片面積、位寬、電壓、頻率、預取值、總線設置等方面作出了一系列的適應性改善,以便更符合低功耗設備的應用需求。

回望歷史:LPDDR從第一代到第三代

從初代LPDDR算起的話,LPDDR產品發展到今天,經歷了LPDDR、LPDDR2、LPDDR3、LPDDR4、LPDDR4X以及LPDDR5等多代次。其中,真正的巨變發生在LPDDR4時代,也正是從這個世代開始,LPDDR開始和DDR逐漸分道揚鑣,走上了獨立發展的道路。

LPDDR:脫胎于DDR,面向功耗敏感市場

在移動計算設備剛興起的時候,人們意識到用于桌面的DDR內存在移動設備上使用時存在很多問題,包括過大的芯片面積,較高的電壓導致較高的功耗等。因此,三星、美光、英特爾、英偉達等廠商聯合起來推出了一種新的內存技術規范,這種內存電壓更低,僅為1.8V,相比之下DDR內存的電壓高達2.5V。此外,這種新的內存技術規范的面積相對更小一些,更適合在“寸土寸金”的移動設備內部使用。技術方面,考慮到移動設備對能耗的敏感程度,因此新的產品加入了一些節能特性,比如深度睡眠模式(DeepPower Down Mode,用于休眠狀態大幅度降低功耗),可配置的自刷新以及溫度補償自刷新(減少刷新次數從而降低功耗)等,使得新產品在功耗上相對DDR有比較大幅度的下降。此外,數據位寬方面,傳統的DDR的數據位寬是64bit,而考慮到當時移動設備的計算能力較弱,過大的數據總線帶寬沒有意義且占據太多的布線面積,因此這種新的存儲產品將10界面的位寬縮減至32bit(廠商可以根據需要配置16bit甚至8bit使用),這也在很大程度上降低了產品的功耗。

在擁有了新的低電壓、小尺寸和新的節能技術加持后,為了和傳統的DDR區分開來,這種新的存儲顆粒被人們稱之為LPDDR或者mDDR。不過,LPDDR在早期并沒有統一的規范,首批使用LPDDR內存的移動產品包括大名鼎鼎的iPhone3系列手機、三星Galaxy系列手機和平板電腦等。

在產品型號方面,初代LPDDR包含了LPDDR 400和LPDDR 533(后者也被稱為LPDDRe,e是“enhance”也就是“增強”的意思)兩種產品,由于基本規范脫胎于DDR,LPDDR的預取值也是2n,內部時鐘頻率為200MHz-266MHz,10頻率同為200MHz-266MHz,數據傳輸速率為400MT/s-533MT/s,在32bit線下的數據帶寬可達1.6GB/s-2.1GB/s,也能完全滿足當時移動設備對帶寬的需求。

新的LPDDR帶來了一個全新的市場,并且這個市場獲得了快速發展。為了規范產品和市場行為,JEDEC也在2008年底推出了針對LPDDR的規范JESD209B。在此之后,LPDDR被JEDEC納入標準統一管理中,從而成為業界的統一標準。

LPDDR2:嶄露頭角,拓展規格

LPDDR的成功不是沒有原因的,移動計算時代的大潮洶涌而來。在這種情況下,JEDEC也加緊努力,“規范走在產品前”的思想開始指導LPDDR2的發展。JEDEC在2009年4月就推出了全新的LPDDR2規范JESD209-2F。新的規范擴大了LPDDR2的產品范圍,將非易失性內存納入其中,并且還帶來了更高的內存密度、更好的性能、更進一步縮小的封裝尺寸以及大量降低功耗的技術。

根據規范內容,LPDDR2實際上分為LPDDR2-S2、LPDDR2-S4以及LPDDR2-N三種產品。其中前兩種都是傳統的易失性存儲設備,最后一種LPDDR2-N是非易失性存儲設備,這種存儲芯片往往會被使用在特殊場合,比如一些執行單一功能,任務量和計算量都比較小的物聯網設備、工業設備中,比如智能電表、工業計算機等。對一般用戶來說,重點還是易失性存儲器。

對于LPDDR2-S2、LPDDR2-S4而言,其最大的差別在于前者使用2n預取,后者使用4n預取。其中前者在市場上并不多見,主要用于和LPDDR過渡的一些場合,后者才是LPDDR2的主力軍。相比之前的LPDDR,LPDDR2的電壓再度大幅度降低至1.2V,節能效果更為出色。另外,所有LPDDR2器件都在命令,地址(CA)總線上使用DDR架構,并采用了lObit位寬(前代LPDDR采用的19bit SDR總線,一次只能在單一方向傳輸數據),這條總線包含了命令、地址和存儲區,行緩沖區信息,這樣設計使得內部總線復雜性降低并帶來了一些能耗的減少。在特色功能方面,LPDDR2帶來了新的低電平操作,使得LPDDR2芯片可以根據情況進入活動、空閑、自刷新或者深度睡眠狀態,LPDDR2能結合實際情況選擇它的運行狀態,更有利于節約功耗。

在產品型號方面,LPDDR2帶來了LPDDR2 800和LPDDR2 1066(后者被稱為LPDDR2e)兩種規格,當然,這個數據是針對LPDDR2-S4而言。因為預取值提升至4n,所以LPDDR2 800和LPDDR2 1066的實際內部時鐘頻率、10頻率等相比之前的LPDDR都沒有變化,均運行在200MHz和266MHz的頻率上。相應地,LPDDR2的數據傳輸速率就提升至800M T/s和1066M T/s,在32bit(可選16bit方案,帶寬減半)下的帶寬也提升至3.2GB/s和4.2G B/s,相比上代LPDDR翻倍。

LPDDR2的壽命周期比較長。從2009年提出規范開始,直到2012年5月,替代LPDDR2的LPDDR3規范才開始提出。考慮到規范發布后一般半年后才有產品推出,LPDDR2的真正產品壽命周期差不多大約接近4年。

LPDDR3:全面改善,提高速度

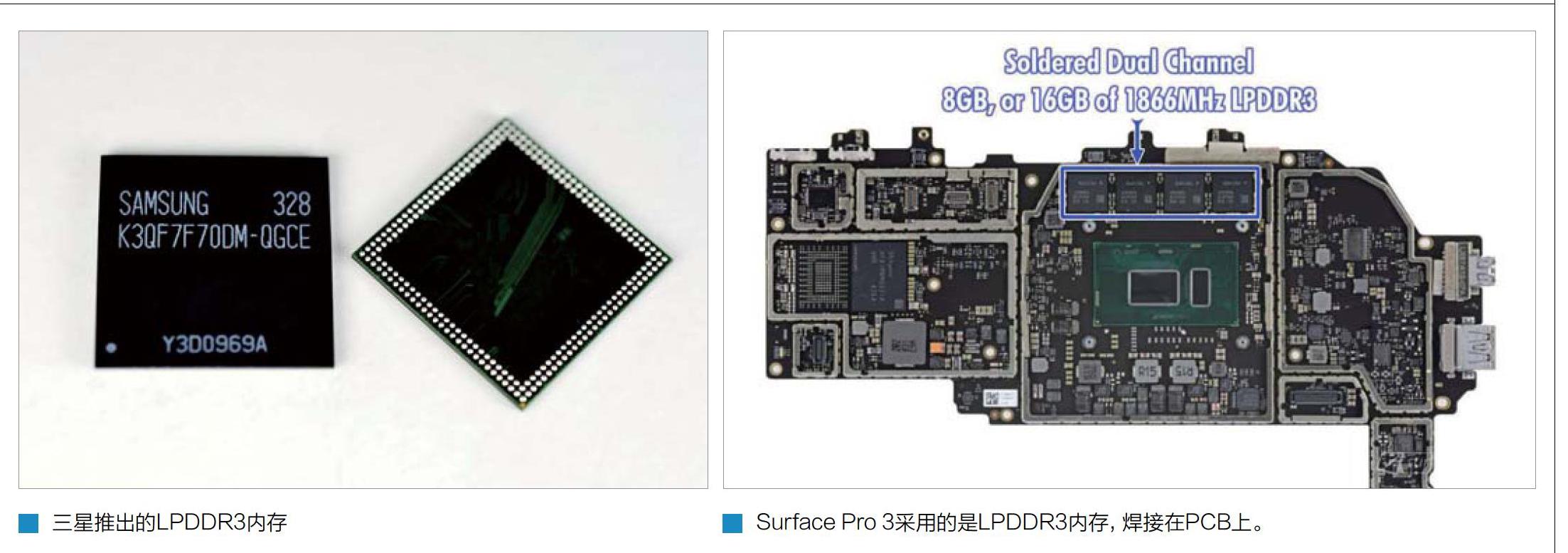

201 2年5月,JEDEC發布了LPDDR3規范,白皮書代碼是JESD209-3。相比之前的LPDDR2,LPDDR3將改善的重點放在了數據傳輸速率和帶寬方面,同時在保留LPDDR2功耗控制功能的情況下還做出了一些優化。另外,在封裝方面,LPDDR3開始支持POP封裝或者離散型封裝,其中前者非常重要,POP堆疊類型的封裝為進一步減小移動設備內部的面積打下了基礎。

LPDDR3出現的背景是移動計算設備使用的SoC性能提升速度較快,在LPDDR2難以滿足的情況下需要新的規格來加強數據傳輸帶寬。因此LPDDR3將數據預取值翻倍至8n,可以在和LPDDR27相同的內部時鐘頻率的情況下使得數據傳輸帶寬翻倍。值得一提的是,LPDDR3規格中并不包含針對非易失性存儲設備的規格,考慮到這類設備多用于工業或者物聯網產品,在當時也的確沒有太強的性能需求。

LPDDR3首先推出的標準是LPDDR3 1600,DRAM的內部時鐘頻率為200MHz,但是8n預取的設計使其數據傳輸速率高達1600MT/s,在32bit配置下(可選16bit方案,帶寬減半)帶寬可達6.4GB/s,基本和同期桌面DDR產品在可比條件下相當。另外,LPDDR3后期還推出了增強版的LPDDR3e,內部時鐘頻率提升至266MHz,數據傳輸速率高達2133MT/s,帶寬也在32bit配置下(可選16bit方案,帶寬減半)提升至8.5GB/s,基本達到了之前LPDDR2的2倍以上。LPDDR3搭配的產品非常多,包括著名的蘋果iPhone 5s、Macbook Air、三星Nexus 10以及微軟的Surface Pr03。后期高通推出的驍龍800和驍龍600也都提供了對LPDDR3的支持。

雖然LPDDR3的速率更高,但是其在架構設計上還是延續了之前LPDDR2的那一套。考慮到移動計算發展速度越來越快,內存也需要加入更多的特性,尤其是針對移動設備進行一些改變,因此在LPDDR3發布之前的2012年3月,JDEDC就召開會議討論下一代LPDDR內存的發展,三星等廠商在2012年1 2月30日就推出了新一代LPDDR產品的樣品,其速度高達3200MT/s,并且在能耗方面有更出色的表現。隨后,在經過長達一年多的協調和技術驗證后,LPDDR4規范在2014年8月正式發布,LPDDR3時代宣告落幕,LPDDR進入了全新發展周期。

LPDDR4:全新架構,為移動計算打牢基礎

夸張一點來說的話,LPDDR3和之前的LPDDR產品都可以看作桌面DDR內存的變種,只是加入了諸如節能、降耗、縮小面積等特性來滿足移動設備的需求。而隨著移動計算進一步發展,LPDDR3這樣繼續根據之前的技術路線改進的發展方式開始無法滿足市場需求了,尤其是在高清視頻、高清攝影等功能逐漸成熟后,移動設備對內存帶寬提出了極高的要求,這是之前LPDDR3以及其相關架構難以做到的。因此,JEDEC需要一種全新架構的產品來滿足移動計算的需求并繼續在能耗和帶寬方面進行平衡。

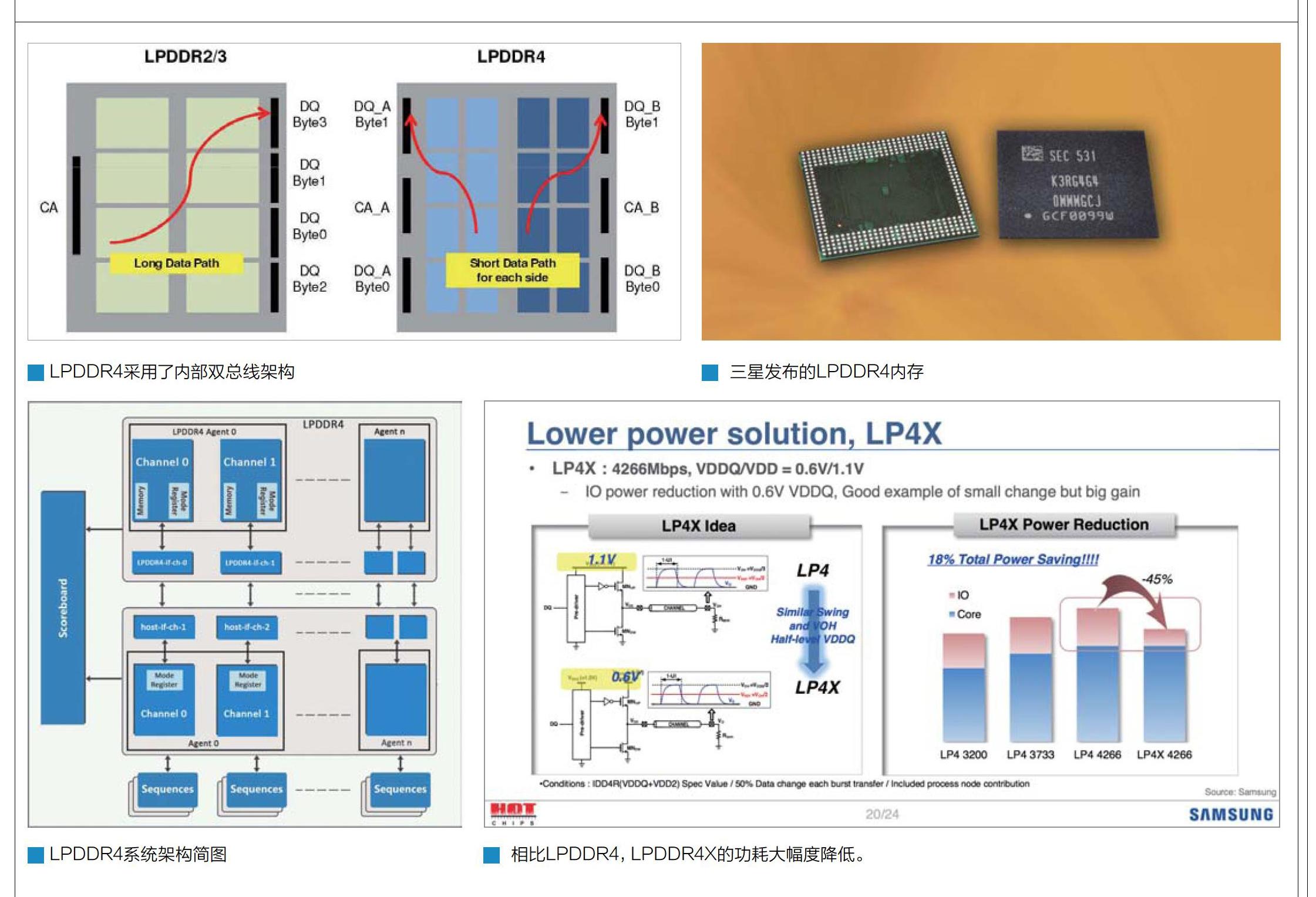

這就是LPDDR4。新的規范在2014年8月發布,其實際產品早在2012年底就出現在各種演示上了。相比LPDDR3,LPDDR4帶來了幾大改進。首先是工作最低電壓從之前的1.2v進一步降低至l.lv,不斷降低電壓帶來了能耗減少。其次,LPDDR4改用了16n預取值,通過預取值翻倍,LPDDR4可以在不繼續提升內部時鐘頻率的情況下提高帶寬。第三,LPDDR4的內部總線從之前的32bit改為2個16bit,總帶寬依舊是32bit,這樣改進使得內部數據存取效率大幅度提升,并在一定程度上降低了存儲部分的功耗。除了上述三種重要改進外,LPDDR4的CA總線從之前的10位DDR命令(繼承自LPDDR2時代)改為6bit的SDR總線,但是加入了多周期命令功能,由于新的總線只在數據傳輸的上沿或者下沿傳輸信息且位寬更窄,能耗更低,其他的一些改進還包括通過專用的命令啟動自刷新,封裝尺寸進一步縮小、數據密度提升等。

由于大幅度更新了內部架構,因此LPDDR4整體效能表現更為出色。業內的例證顯示,和基于4GbLPDDR3的2GB內存相比,采用8Gb的LPDDR4顆粒的2GB內存在功耗方面降低了40%。在產品方面,LPDDR4帶來了LPDDR4 3200這樣的規格,其內部時鐘頻率為200MHz,10速度為1600MHz(注意2個16bit總線),但是數據傳輸速率來到了3200MT/s,因此最終在32bit的位寬下,LPDDR4 3200的帶寬達到了12.8GB/s的水平。

LPDDR4之后,在三星的倡議下,JEDEC又在201 7年3月發布了JESD209-4-1規范,確定了新的LPDDR4X。LPDDR4X是LPDDR4的技術擴展版本,和之前的“e”增強版本有所不同的是,LPDDR4X除了在頻率、性能上有所加強外,還帶來了進一步的功耗節省設計。在新的規范中,LPDDR4X IO部分的電壓從l.lv降低至0.6V,數據存儲部分的電壓維持不變。

對LPDDR家族的產品來說,其頻率分為兩個部分,分別是數據存儲部分頻率和10頻率。繼續細分的話,數據存儲部分頻率可以分為內部時鐘頻率和內部物理頻率。在本文的描述中,大家可以清楚地看到LPDDR的內部時鐘頻率始終不會超過266MHz,一般只有200MHz和266MHz這2個規格。對于內部物理頻率而言,考慮DDR帶來的內部時鐘頻率倍數的話,那么實際上LPDDR內存的數據存儲部分一直都在100MHz和133MHz兩個頻率上運行。對內存這種產品而言,其頻率并不會太高,較低的頻率有助于確保內存在低電壓下運行時的穩定性和可靠性,同時低電壓又帶來了能耗降低。雖然內部時鐘頻率和內部物理頻率一直沒有提升,但通過預取值不斷翻倍又翻倍,比如從2n到4n、8n再到16n-LPDDR4的預取值是LPDDR的8倍,LPDDR的數據傳輸速率一直在提升。比如內部時鐘頻率都為200MHz,LPDDR4 3200的數據傳輸速率達到了3200MT/s,相對應的在LPDDR 400上則只有400MT/s。

那么這和10頻率又有什么關系呢?由于10部分承擔的是LPDDR內存對外的數據傳輸,在預取值提升后,10頻率就不得不進一步提升以跟上越來越大的數據吞吐量。從LPDDR到LPDDR4,10頻率從200MHz一路提升至1600MHz。高頻率運作下的10部分帶來了較高性能的同時,也產生了比較高的功耗。因此,在LPDDR4X上,三星率先提議將10電壓降低至0.6v,這帶來了總線和IO部分功耗的顯著降低。因此,新的LPDDR4X功耗得以進一步降低,性能得到了同步提升。

LPDDR4X還帶來了新的LPDDR4X 4266型號,其內部時鐘頻率提升至266MHz,預取值還是16n,雙總線方案,數據傳輸速率達到了4266MT/s,在32bit位寬配置下帶寬達到了17G B/s,進一步提高了低功耗設備在存儲方面的性能。

不過,雖然LPDDR4X在內核改進方面和LPDDR4相比非常微小,但是LPDDR4X和之前所有代次的LPDDR內存一樣,都無法實現向后兼容,這是因為LPDDR4較高的電壓會導致LPDDR4X的10部分無法正常工作,不過和桌面內存有所不同的是,LPDDR4X這樣的產品主要用于OEM廠商制造使用,用戶幾乎不存在更換的機會,因此也不會帶來額外的兼容性問題。

由于LPDDR4X帶來了功耗的降低和性能的提高,因此在移動設備中大獲成功,大量高端手機、平板甚至筆記本電腦都采用LPDDR4X作為內存使用,LPDDR內存迎來了其發展的黃金時刻。

LPDDR5:帶寬翻倍,比拼高端桌面平臺

在LPDDR4X帶來了輝煌后,LPDDR5也開始緊鑼密鼓地準備了。2019年,JEDEC發布了JESD209-5規范,正式帶來了LPDDR5標準。

從架構角度來看,LPDDR5保留了LPDDR4時代使用的16n預取值,但是加入了在桌面DDR4上使用的區塊組( Bank Group)概念。簡單來說,之前的LPDDR內存如果內部有8個或者16個區塊的話,那么它們是以串行的方式來讀寫的,O號區塊讀寫完成后再去讀寫1號區塊、2號區塊,以此類推。但是在區塊組概念出現后,一個內存中會根據情況被劃分為2個或者4個或者更多的區塊組,數據并行進入每個區塊組進行讀取操作。這相當于在內存的內部實現了并行存取。因此LPDDR5才可以在不提高預取值和頻率的情況下,僅僅依靠區塊組和10部分的頻率提升來大幅度提升數據帶寬。

除了引入區塊組的概念外,LPDDR5還帶來了包括新的可擴展時鐘架構,解決了CA總線的速度無法跟上數據總線速度提升的問題。新的設計使得CA總線可以有條件以數據總線1/4或者1/2的速度運行,這使得CA總線的穩定性和可靠性都得到了提升。另外,LPDDR5還加入了決策反饋均衡器(DFE),減少了對

為什么DDR4還比LPDDR4“慢”

本文的介紹凸顯了LPDDR4的優勢,那么既然LPDDR這么好,為什么不引入桌面平臺呢?實際上這個問題的答案也是明確的。我們以目前主流的LPDDR4和DDR4作為對比解釋—下。

先來看看DDR4內存的基本規格。目前DDR4并沒有采用16n預取值,而是依舊采用了8n預取值,但是其實際運行的物理頻率從200MHz起跳,直到更高的400MHz、533MHz等,同時還加入了區塊組的概念。可以說,DDR4和LPDDR4在架構設計上是完全不同的兩個產物,它們基本上沒有任何技術上的關聯。同時,DDR4具備了桌面內存所有的特性,比如64bit位寬、更大的容量、更高的電壓和相對較低的延遲值。

這樣來看相比LPDDR4,首先要明確的是DDR4內存的位寬更大,單條內存能夠實現的帶寬更高。目前所有主流DDR DIMM內存的位寬都是64bit,搭配桌面級別CPU的128bit通道,2根DDR4 4266規格的內存就可以實現4266MT/sx64bitx2/8=68.3G Bls。相比之下,即使是LPDDR4X 4266這樣的LPDDR4家族的頂級型號,其位寬僅為32bit,單個LPDDR4X 4266的帶寬數值是4266MT/sx32bit/8=17GB/s。如果搭配桌面CPU的話,需要4個內存通道才能完全匹配,雖然最終總帶寬也可以達到和桌面CPU相同的水平,但是更多通道帶來了更復雜的主板設計、內存控制器設計以及使用上的麻煩,顯然是不合算的。

其次,雖然移動平臺的LPDDR通過降低電壓等手段實現了低功耗,但是世上沒有免費的午餐,LPDDR的低功耗也需要付出代價,那就是較高的延遲值。舉例來說,LPDDR3 2133的延遲值一般在lOOns左右,即使是延遲更高、近似規格的DDR4內存,其延遲值也只有大約70ns,低了一大截,如果選擇DDR3做比較的話,延遲值還會更低。對于這種情況,一篇名為《A Performance&PowerComparison of Modern High-Speed DRAM Architectures》的論文專門作出了研究。在仿真結果下,以帶寬完全相同的DDR4和LPDDR4作對比的話,DDR4的每周期指令數要比LPDDR4高6%,延遲值顯著更低。對現代高頻率CPU來說,尤其是桌面CPU頻率接近5GHz的情況下,更高的延遲值將會嚴重影響CPU的性能發揮。

因此,一般情況下,同代LPDDR內存是要弱于同時代的DDR內存的,其核心原因就是它的帶寬更低、延遲值更高。目前,LPDDR內存在PC中的應用僅限于超便攜、超輕薄或者對續航有要求的設備,也并非以性能作為主要方向。接收數據的符號間干擾(ISI),從而提高了接收數據的余量。此外,LPDDR5還帶來了包括鏈路ECC校驗、增加至3個FSP等設計,這些設計都在很大程度上增強了LPDDR5在高數據傳輸速率下的穩定性。

在功耗和電壓方面,LPDDR5目前支持多組低電壓設置。在較高的頻率下運行時,LPDDR5支持1.05V的核心電壓和0.5v的10電壓,在較低頻率下運行時,這兩個電壓數值會分別降至0.9V、0.3V,以進一步節約能源降低能耗。相比LPDDR4,LPDDR5的低電壓帶來了顯著的功耗降低。另外,LPDDR5還帶來了更新版本的深度睡眠模式,新模式相比舊模式能帶來更低的閑置功耗,三星給出的數據是LPDDR5的深度睡眠模式消耗的功耗是LPDDR4X的一半,值得期待。總的來看,三星的評估數據是LPDDR5的功耗相比LPDDR4X大約降低了20%,這個成績也相當不錯了。

產品規格方面,目前LPDDR5推出的產品主要是LPDDR5 5500,但是JEDEC宣稱LPDDR5最終將運行在LPDDR5 6400的速率上,在相同位寬配置下,其性能是LPDDR4 3200的2倍。舉例來說,在32b.t的位寬配置下(需要2個16bit的LPDDR5組成雙通道),LPDDR5 6400能帶來高達25.6G B/s的帶寬,如果是LPDDR55500的話,這個數據22G B/s,相比位寬為32bit的LPDDR4X,LPDDR5帶寬至少提升了29%,最多可以提升49%。

值得注意的是,正如上段提到的,目前推出的LPDDR5內存的位寬都只有16bit,這一點和之前的LPDDR4家族以及LPDDR3等產品是不同的,前代產品的位寬最高可配置為32bit。LPDDR5減少位寬的原因可能是考慮到其本身即使是現在的較低規格版本,在16bit下帶寬就超過10GB/s( 5500MT/sx16bit/8=11GB/s),對很多設備來說這個帶寬已經足夠了,因此降低位寬可以增加LPDDR5的市場適用范圍。針對高端SoC來說,即使LPDDR5采用了16bit位寬設計,還可以采用多通道技術來實現帶寬翻倍,這也不是太難的操作。

在LPDDR5的產品量產方面,目前三星和美光兩家廠商是推動的主力,國內合肥長鑫也計劃在2022年之前推出LPDDR5內存。具體來說,三星之前宣布將旗下EUV光刻機用于D1z DRAM的大規模量產,其最重要的產品就是LPDDR5內存。目前三星推出了兩代LPDDR5內存,其中一代采用DUV制造,工藝節點代號為Dly,新的一代就是前文所說的D1z。在改用EUV制造后,三星顯著提高了芯片的存儲密度并縮小了面積。Dly工藝節點的LPDDR5芯片容量可選8Gb和12Gb兩種,但是D1z就進化至12Gb和16Gb了。在面積方面,同為12Gb的顆粒,Dly產品的面積為53.53平方毫米,D1z僅為43.98平方毫米,工藝進步的效果顯著。美光方面也計劃在近期推出采用EUV技術的16Gb LPDDR5內存,不過相比三星的產品,美光的芯片面積略微大了一些,16Gb的LPDDR5面積為68.34平方毫米,相對應的三星的產品只有61.20平方毫米。

更加節能、更加高速:LPDDR的未來

從本文的介紹可以看出,LPDDR在發展過程中,從脫胎于DDR到走上獨立發展的路線,以及現在LPDDR5的帶寬逐漸趕上桌面平臺,同時功耗又在不斷降低,堪稱走出了一條高性能、低功耗的獨立之路。對于移動設備和低功耗設備來說,LPDDR的高帶寬和低功耗特性是非常令人滿意的。未來LPDDR內存還將在這條道路上繼續發展,給我們帶來更多輕便、節能但是高速的產品。