日本開發新型晶體管利于實現2nm半導體

2021-06-28 17:45:24

電腦報 2021年10期

關鍵詞:結構

半導體細微化(Scaling)是目前半導體行業最熱門的話題之一。隨著DRAM等的芯片元器件在內的大部分電子元器件和存儲單元趨于超小型化,對于高度集成技術的需求也逐漸提高,超小型芯片將可以儲存并快速處理天文數字般的數據量。

日本產業技術綜合研究所近年來致力于開發新一代半導體的晶體管結構,預計有助于制造電路細微化的高性能半導體。半導體細微化的技術逐年提高,不同研究機構之間的合作或將成為打開局面的方法之一。

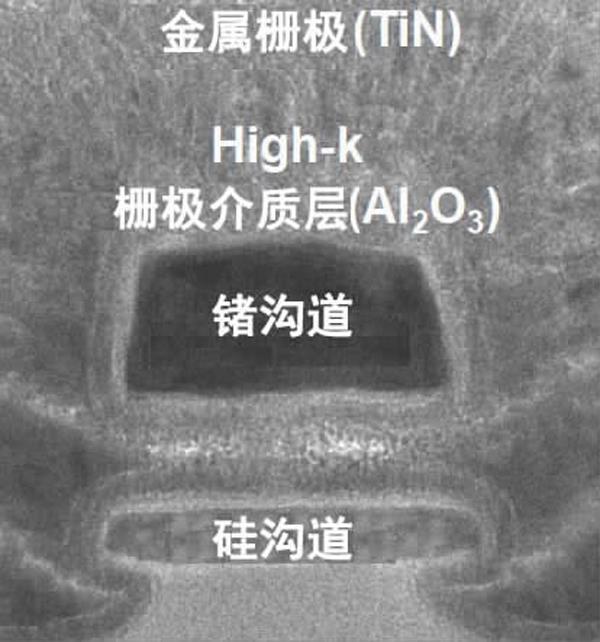

新結構的場效應晶體管(FET),將硅(Si)和鍺(Ge)等不同材料從上下方堆疊、使n型和p型場效應晶體管靠近的名為“CFET”的結構。日本産業技術綜合研究所表示,這在世界上首次實現。

研究成果發表于2020年12月在線上舉行的半導體相關國際會議“IEDM2020”上,日本產業技術綜合研究所等將在今后約3年里向民營企業轉讓技術,力爭實現實用化。

與此前的晶體管相比,CFET結構的晶體管性能高、面積小,有助于制造2nm以下線寬的新一代半導體。晶體管是在半導體之中承擔電信號切換等的基本電子元件,但要實現細微化,改善結構成為課題。

把半導體晶片的晶體管以高密度集成后,能夠以高速、低耗電量處理人工智能(AI)等。如果應用于數據中心等,有望大幅削減電力消耗。

目前最新款智能手機使用5nm線寬半導體,今后將采用3nm、2nm產品,此次開發的新型晶體管預計應用于2024年以后的尖端半導體。不過,將來哪種晶體管結構得到采用仍未確定,或將取決于性價比。

猜你喜歡

小獼猴智力畫刊(2023年4期)2023-04-23 08:49:58

哲學評論(2021年2期)2021-08-22 01:53:34

中華詩詞(2019年7期)2019-11-25 01:43:04

模具制造(2019年3期)2019-06-06 02:10:54

中學生數理化·高一版(2018年1期)2018-02-10 05:20:03

影視與戲劇評論(2016年0期)2016-11-23 05:26:01

七彩語文·寫字與書法(2016年7期)2016-07-28 21:40:22

七彩語文·寫字與書法(2016年6期)2016-07-15 19:36:34

人間(2015年21期)2015-03-11 15:23:21

現代企業(2015年9期)2015-02-28 18:56:50