一種雙通道16位串行數模轉換器電路設計

康明超,孔祥藝,黃立朝,丁 寧,時晨杰

(中科芯集成電路有限公司,江蘇無錫 214072)

1 引言

數模轉換器(Digital to Analog Converter,DAC)在通信系統、音頻系統和混合信號系統等眾多領域具有廣泛的應用,其主要功能是將數字信號轉換成與之對應的模擬信號,在手持式電子產品中,不僅要求數模轉換器具有很低的功耗,還要有很高的信噪比,為適應快速發展的電子產品的需求,數模轉換器的性能也要不斷提高[1]。

數模轉換器有很多種架構,常見的架構包括R-2R倒梯形電阻網絡型、串電阻型、電流舵型(Current-Steering)以及電荷再分布型[2]。R-2R倒梯形電阻網絡型數模轉換器功耗低、面積較小,但是速度較慢[3]。串電阻型數模轉換器具有高分辨率、高精度的優點,但是電阻數目會隨著分辨率的提高逐漸增多,導致電路面積增大[4]。電流舵型數模轉換器工作速率快,但是功耗大,精度相對較低[5]。電荷再分布型數模轉換器具有較高的分辨率,但該結構對電路中電容的精度要求較高,同時會增大電路面積[6]。本設計提出電流舵與電阻網絡混合型DAC。電流舵中的電流源采用共源共柵架構,有效提高了輸出阻抗,在保持較低功耗和面積的同時達到較高的精度。

2 混合型DAC結構設計

2.1 DAC整體架構設計

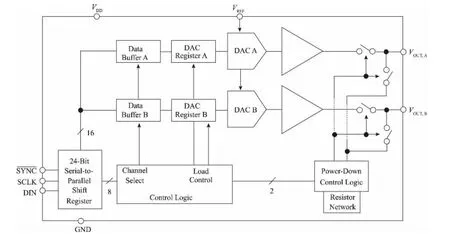

本設計是一款混合型雙通道數模轉換器。其系統結構框圖如圖1所示,該DAC主要由24位串轉并移位寄存器模塊、數據緩沖模塊、寄存器模塊、輸出緩沖放大器模塊、邏輯控制模塊、下電控制模塊等組成。

圖1 數模轉換器結構框圖

VREF為系統提供穩定的參考電壓。24位串轉并移位寄存器模塊將DIN串行輸入數據轉換成并行數據,其中高8位作為邏輯控制位,有通道選擇和寄存器選擇的作用。低16位作為數據位,將數字碼傳輸到對應的數據緩存器后輸入到DAC譯碼電路,進行數字信號到模擬信號的轉換。輸出緩沖放大器輸出軌到軌的模擬信號。同時,該DAC電路支持上電復位和Power-Down模式。

2.2 譯碼電路設計

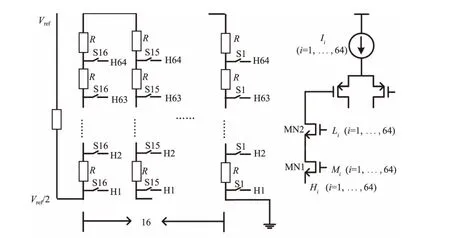

譯碼電路主要包括低6位溫度計譯碼、中6位電阻網絡譯碼和高4位電阻網絡譯碼電路。溫度計譯碼電路中,每一個開關控制的電流源權重的大小相同,當輸入數字信號中有1位信號發生改變的時候,其所相應的開關單元中也只有一對差分開關發生狀態改變,輸出的電流源就像溫度計一樣逐格上升或下降發生變化。譯碼電路圖如圖2所示。

在譯碼電路中,高4位數據位將0 V~VREF/2用1024個相同阻值電阻串聯分壓,通過數字邏輯構成16選1的邏輯(S1,...,S16),將VREF/2分成16等份,每組包含64個串聯電阻,使每一份電壓包含64個臺階,任意輸出端用Hi(i=1,...,64)表示。中6位數據位通過數字邏輯構成64選1的邏輯,其輸出為開關陣列,開關陣列共有64組開關,每組開關對應高4位輸出的64個臺階電壓中的一個,任意輸出用Mi(i=1,...,64)表示,由于是NMOS開關,故輸出開關信號為高電平有效。低6位譯碼器為64位的溫度計譯碼器,高電平有效,其64個溫度計譯碼輸出控制圖2右側64個帶有相同尾電流源的差分輸入對開關陣列,每個開關傳遞的電壓為高10位的輸出電壓。隨著輸入碼元的增加,溫度計譯碼器輸出的有效高電平越多,差分對和電流源導通的更多,這樣就把臺階電壓再次細分成64份。綜上,經過高4位、中6位和低6位譯碼電路,就把VREF/2的電壓分成16×64×64=65536份,實現了模擬量的譯碼。

圖2 譯碼電路原理圖

2.3 輸出緩沖放大器設計

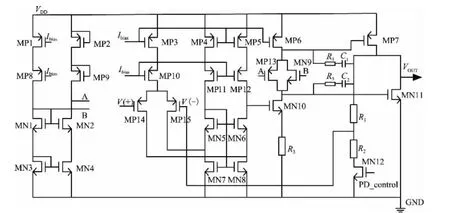

該電路與譯碼電路的輸出端相連,能夠隔離電路負載端對線性電阻網絡的干擾,具有輸出緩沖的作用,同時可以輸出穩定的電壓,電路圖如圖3所示。

圖3 放大器電路原理圖

該放大器的輸入為開關電阻網絡的輸出,范圍為0~VREF/2,該運放閉環增益為2,輸出端為軌到軌,范圍為0~VREF。

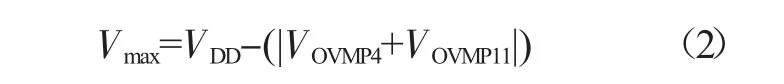

為了得到較高的轉換線性度和增益,放大器第一級采用折疊式共源共柵結構,該結構具有較高的增益,其輸出擺幅的最小值為:

輸出擺幅最大值為:

因此第一級運放的輸出擺幅為:

第二級為帶電阻R3負反饋的共源級單級放大器,可進一步提高運放的整體增益,但是輸出仍無法達到軌到軌。為了增大電路的輸出擺幅,第三級放大器采用推挽式反相器,達到輸出端軌到軌的目的,由于該運放輸出端需要驅動大電流負載,且電路整體的功耗較小,因此第三級輸出級的MOS管工作于亞閾值區,提供的增益較小,運放的增益主要來自前兩級。為了保證輸出級的大面積NMOS管工作于亞閾值區,需要將第二級的放大管NMOS漏級電壓的靜態電壓設置于NMOS管VTH以下,而為了保證輸出級PMOS管工作于亞閾值區,需要額外增加一個有源電阻來抬高靜態電位,圖3中的有源電阻是通過一對CMOS開關的導通電阻來實現的,它可以把輸出端PMOS管柵級電壓抬高到接近正電源軌,使得PMOS管也處于亞閾值區工作。運放第一級的差分輸入端正向端接收譯碼電路輸出電壓,而負向端接收運放負反饋電阻的反饋電壓,若運放增益高,使得運放工作于深度負反饋時,輸出電壓VOUT與輸入臺階電壓VIN之間的關系為VOUT=2VIN。為了使放大器有良好的頻率響應特性,采用Miller電容補償技術。

3 電路仿真結果

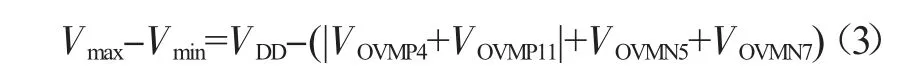

本次設計的電路、版圖和仿真驗證都是基于0.5μm CMOS工藝,版圖布局如圖4所示,通過對DAC功能與參數特性進行分析仿真,仿真結果表明DAC功能正常,參數達標。

圖4 DAC版圖布局

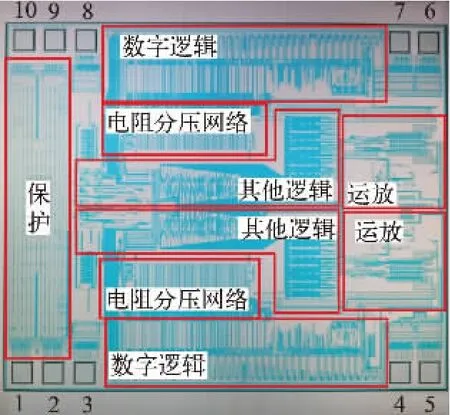

在5 V工作電壓、tt工藝角、25℃環境下,設置輸入信號頻率約為20 MHz、采樣頻率為200 MHz時對電路進行整體仿真,仿真結果如圖5所示。

圖5 仿真結果圖

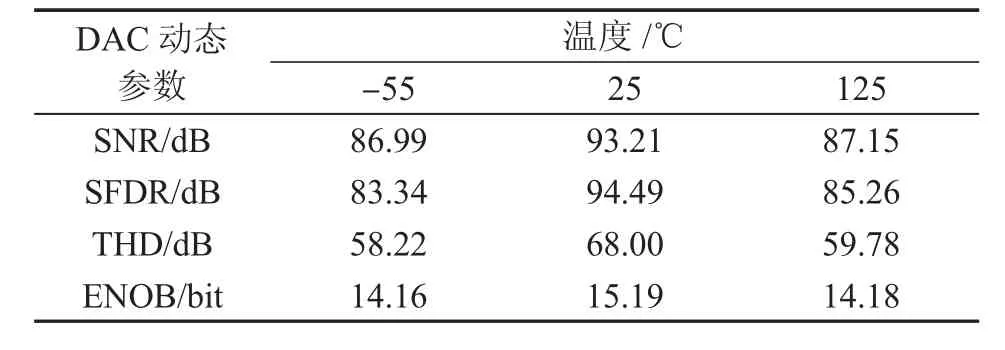

表1給出了幾種典型溫度下DAC動態參數的仿真結果,可以看出在高溫和低溫情況下對DAC輸出結果產生微弱影響,動態參數仍保持較好的特征。

表1 DAC動態參數仿真結果

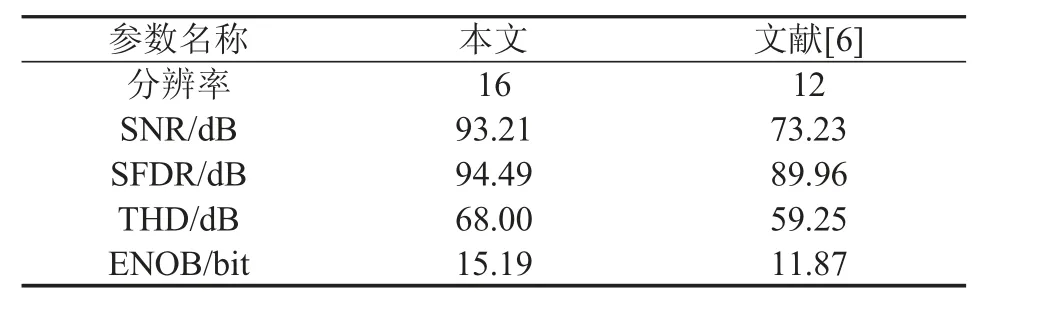

表2給出了本文中混合型DAC和文獻[6]中同類型DAC的動態參數仿真結果的對比情況,其中溫度為25℃,tt典型工藝條件,可以看出本文提出的DAC結構具有更好的動態參數性能。

表2 本文與之前研究成果的性能對比

4 結論

本文基于0.5μm CMOS工藝設計了一款16位混合型數模轉換器,通過電阻陣列譯碼和電流舵溫度計譯碼電路、輸出緩沖放大器提高DAC的精度和線性度,降低了電路的功耗和面積。通過電路仿真,該款DAC電路在200 MHz采樣頻率、25℃、tt典型工藝條件下,有效位數為15.19位,信噪比為93.21 dB,總諧波失真為68.00 dB,無雜散動態范圍為94.49 dB。

在代工廠生產加工芯片的時候,可能會因為加工設備不能達到生產要求、工藝落后等一系列非理想因素的存在,使得電流源陣列中每個單位電流源電流的大小與理想中存在失配。電流源的控制開關在進行開關動作時會產生瞬態響應。器件在版圖中的擺放位置、方向等因素會導致器件尺寸、摻雜、氧化層厚度等參數發生微小變化。以上因素會導致DAC的輸出信號噪聲增大、輸出波形毛刺增多、非線性誤差增大等現象,對DAC動態參數性能產生影響,可以通過校正算法和版圖合理布局等方法對參數的不足進行改善。