多次熱氧化削減硅通孔內壁扇貝紋

王 碩,楊發順,2,3,馬 奎,2,3

(1.貴州大學大數據與信息工程學院,貴陽 550025; 2.貴州省微納電子與軟件技術重點實驗室,貴陽 550025;3.半導體功率器件可靠性教育部工程研究中心,貴陽 550025)

0 引 言

集成電路當前主要采用半導體平面集成技術進行制作,該技術的發展主要依賴于光刻技術的不斷進步和器件特征尺寸的不斷縮小。隨著集成電路的復雜度和規模的不斷增加,芯片上互連線的長度劇增,互連線導致的延遲和功耗越發明顯。自超深亞微米工藝后,互連線延時基本已經超過了晶體管的門延時,互連延時問題越發成為影響集成電路發展的瓶頸[1-2]。基于硅通孔(through silicon via, TSV)實現多層堆疊芯片互連的三維集成技術能夠有效縮短互連線的長度、提高系統集成度和功率密度,且可實現異質集成、減小芯片面積、降低成本[3-7]。

硅通孔是三維集成系統的關鍵技術之一[8]。目前常見的硅通孔內部一般包含絕緣層、勢壘層和金屬芯,由于各層材料的性質不同,層間界面質量對硅通孔的性能以及三維集成系統的可靠性有著至關重要的影響。刻蝕形成原始硅通孔后,孔內壁的平滑度對后續填充的孔內各層材料以及層間界面的微觀結構有著直接影響[9]。BOSCH刻蝕技術是當前主流的硅通孔刻蝕方法,該方法是用SF6作為蝕刻劑進行硅刻蝕,刻蝕一定時間后用C4F8對側壁進行鈍化,這樣交替多次刻蝕和鈍化,能夠實現側壁陡峭、橫向刻蝕極小的硅通孔。但是,由于刻蝕和鈍化的交替進行,不可避免地會在硅通孔的內壁形成扇貝紋[10-11]。

銅擴散是造成硅通孔可靠性下降的原因之一,勢壘層是防止銅擴散的重要技術[12]。平滑的TSV內壁更容易通過物理氣相沉積(physical vapor deposition, PVD)得到連續的勢壘層,有利于縮短勢壘層淀積時間[13]、降低成本。熱機械應力是影響硅通孔可靠性的主要因素之一,相鄰兩層材料的熱膨脹系數失配是導致熱機械應力的主要原因。過大的熱應力可能會造成界面分層、裂縫和空洞等可靠性問題,且過大的應力會改變載流子的遷移率,對電路的時序產生負面影響[14]。TSV內壁扇貝紋起伏越大,平均熱機械應力也會越高,且存在尖峰應力,其值高于平均熱應力水平,會導致TSV的可靠性顯著降低。因此,削減TSV內壁的扇貝紋是非常重要的[15-16]。

探索新的深硅刻蝕技術是實現平滑內壁TSV的有效途徑之一。Morikawa等[13]采用平面磁中性環路放電(magnetic neutral loop discharge, NLD)等離子體獲得了高縱橫比和均勻的深孔刻蝕,該方法是一種無扇貝刻蝕技術,但側壁仍然有一定的粗糙度。Wong等[17]通過在TSV側壁沉積正硅酸乙酯氧化物來改善或完全去除TSV側壁的扇貝紋,但正硅酸乙酯氧化物和單晶硅襯底之間存在晶格失配和熱膨脹系數適配等問題。優化和改進BOSCH刻蝕工藝的相關參數,也能夠降低扇貝紋起伏。趙鴻等[18]通過優化工藝參數,在較厚的二氧化硅掩蔽層上刻出微孔后,通過BOSCH刻蝕工藝刻蝕TSV,實現了刻蝕速率為0.612 μm/min、刻蝕選擇比為2.122、刻蝕角度為80.573°的孔,通過降低襯底溫度消除了孔口咬邊效應,縮短每個循環步驟的刻蝕時間和鈍化時間,減小了TSV內壁的扇貝尺寸,但不能徹底消除扇貝紋。后處理也能夠降低高深寬比TSV內壁的扇貝紋起伏。目前常用的方法是在BOSCH刻蝕完成后用氬離子進行清洗,去除刻蝕生成物的同時削減TSV內壁的扇貝紋。氬離子清洗的主要目的是去除刻蝕生成物,對削減扇貝紋的效果甚微。為了有效削減TSV內壁的扇貝紋,本文提出了通過循環多次“高溫熱氧化+腐蝕二氧化硅”的實驗方法。氧化實驗在高溫水平管式氧化爐中進行,將TSV的孔口正對石英管尾部的進氣口,用較高流量的氧氣灌入小孔徑、高深寬TSV內來保證內部的氧濃度均勻,這樣在扇貝紋凸起的地方氧化速率會較快。氧化完后通過濕法腐蝕去掉二氧化硅。通過循環多次“高溫熱氧化+腐蝕二氧化硅”,可得到平滑的TSV內壁。

1 機理分析

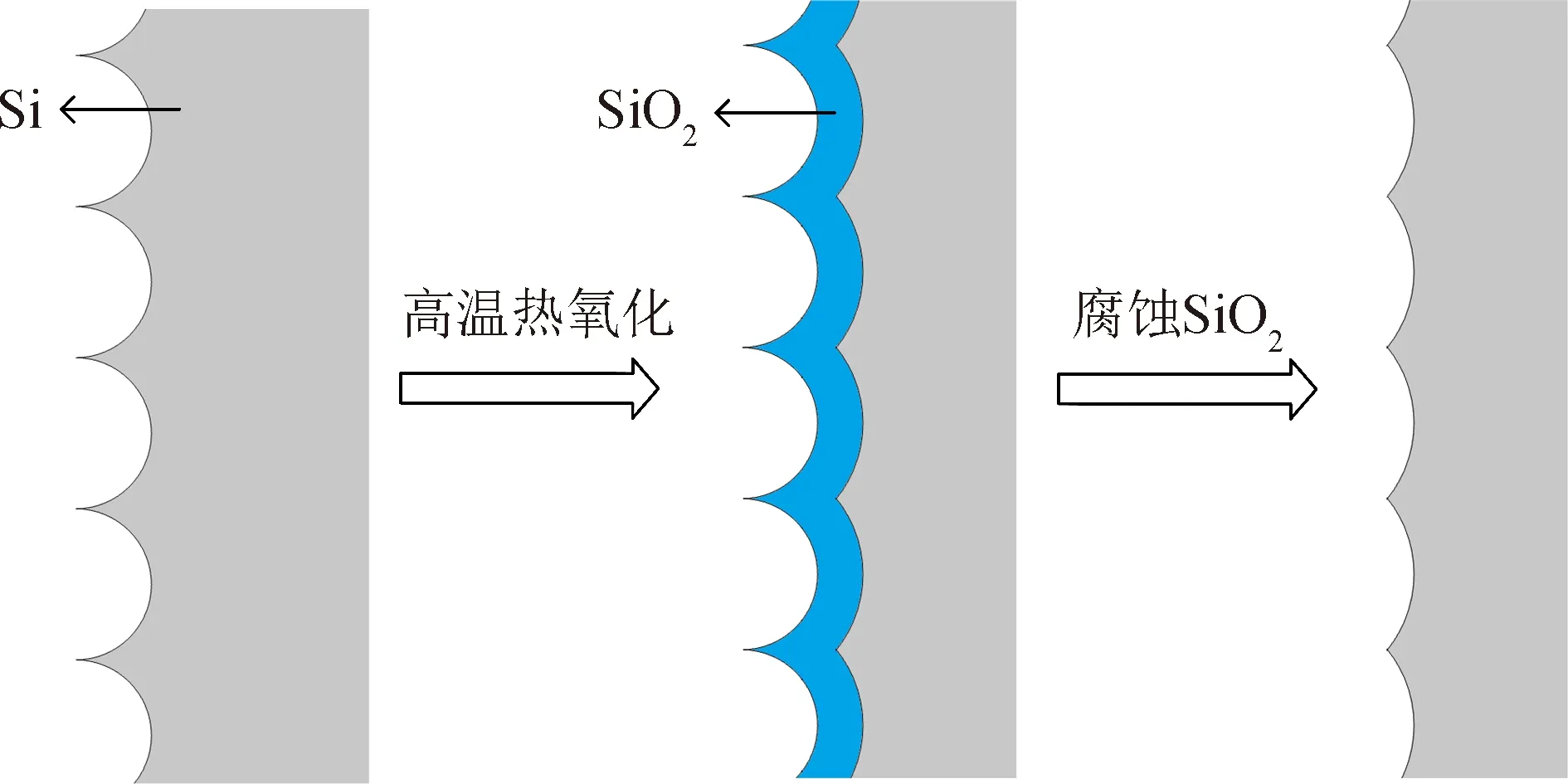

單晶硅暴露在室溫空氣中,經過幾秒鐘就會生成幾個原子厚度(0.5~1 nm)的二氧化硅層(俗稱“自然氧化層”)。在室溫下,自然氧化層會阻擋空氣中的氧原子繼續和硅反應。但當環境溫度升高到600 ℃以上后,在含有充足氧原子的氣體氛圍中,氧原子能穿透硅表面已有的氧化層,繼續和硅反應生成二氧化硅,硅和氧氣氛圍的接觸面越大,氧化速率會越快。如圖1所示,TSV內壁存在扇貝紋起伏,在保證孔內氣體氛圍中氧濃度均勻的情況下,扇貝紋突起的地方,氧化速率會較快。因此,經過高溫熱氧化并去除二氧化硅層后,TSV內壁的扇貝紋起伏會降低。

圖1 削減扇貝紋的機理分析示意圖Fig.1 Schematic diagram of mechanism analysis of scallop pattern reduction

2 實 驗

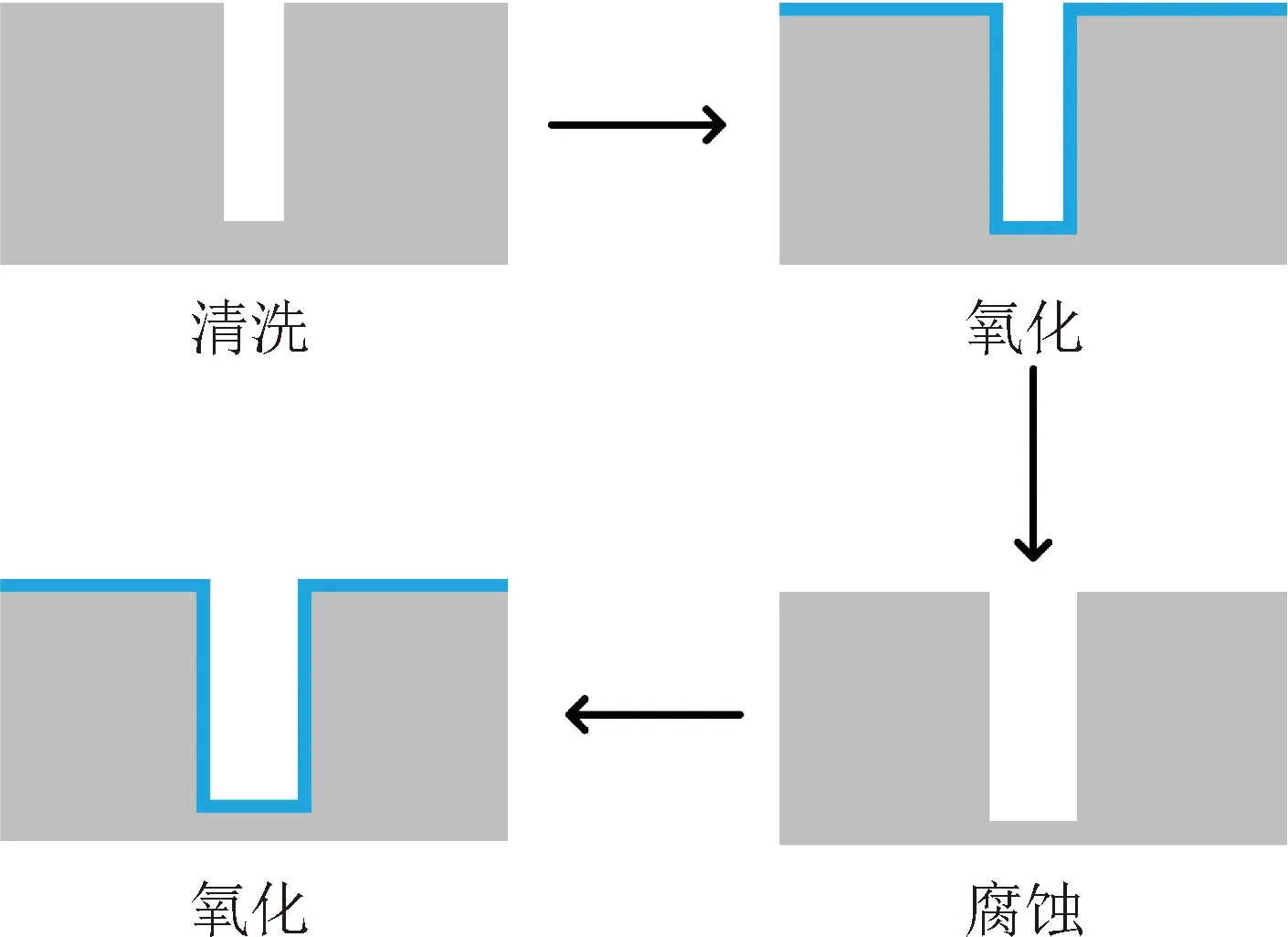

高溫熱氧化和腐蝕二氧化硅多次交替循環削減硅通孔內壁扇貝紋的工藝示意圖如圖2所示,具體實驗方案如下:

圖2 多次循環熱氧化示意圖Fig.2 Schematic diagram of multi cycle thermal oxidation

(1)用微電子工藝中的標準清洗流程對干法刻蝕后的硅片進行清洗,清洗后用高純氮氣吹干備用;

(2)將含有TSV的硅片送入爐管中,在特定溫度、濕氧環境(高純氧氣攜帶水蒸氣進入反應爐)下進行高溫熱氧化;

(3)氧化完成后用40%(體積分數)氫氟酸與去離子水體積比為1∶10的水溶液腐蝕掉二氧化硅,為確保硅通孔底部的二氧化硅能被完全腐蝕,腐蝕過程在超聲波水浴環境下進行;

(4)腐蝕完二氧化硅后,再用標準清洗流程對硅片進行清洗,清洗后再次進行高溫熱氧化;

(5)氧化后再次進行二氧化硅腐蝕;

(6)如此交替循環進行多次高溫熱氧化和腐蝕二氧化硅。

3 結果與討論

實驗樣品是BOSCH刻蝕得到的孔徑為10 μm、孔深為80 μm的圓柱形硅通孔,通過四次高溫熱氧化和四次腐蝕二氧化硅的工藝削減硅通孔內部的扇貝紋。每次高溫氧化的溫度為1 150 ℃、濕氧氧化時間為10 min、氧氣流量為1.5 L/min、氧氣流向垂直于硅片表面(平行于硅通孔的側壁),每次高溫氧化時硅片在900 ℃進出爐,升、降溫過程中用氮氣對硅片進行保護,防止硅片氧化。

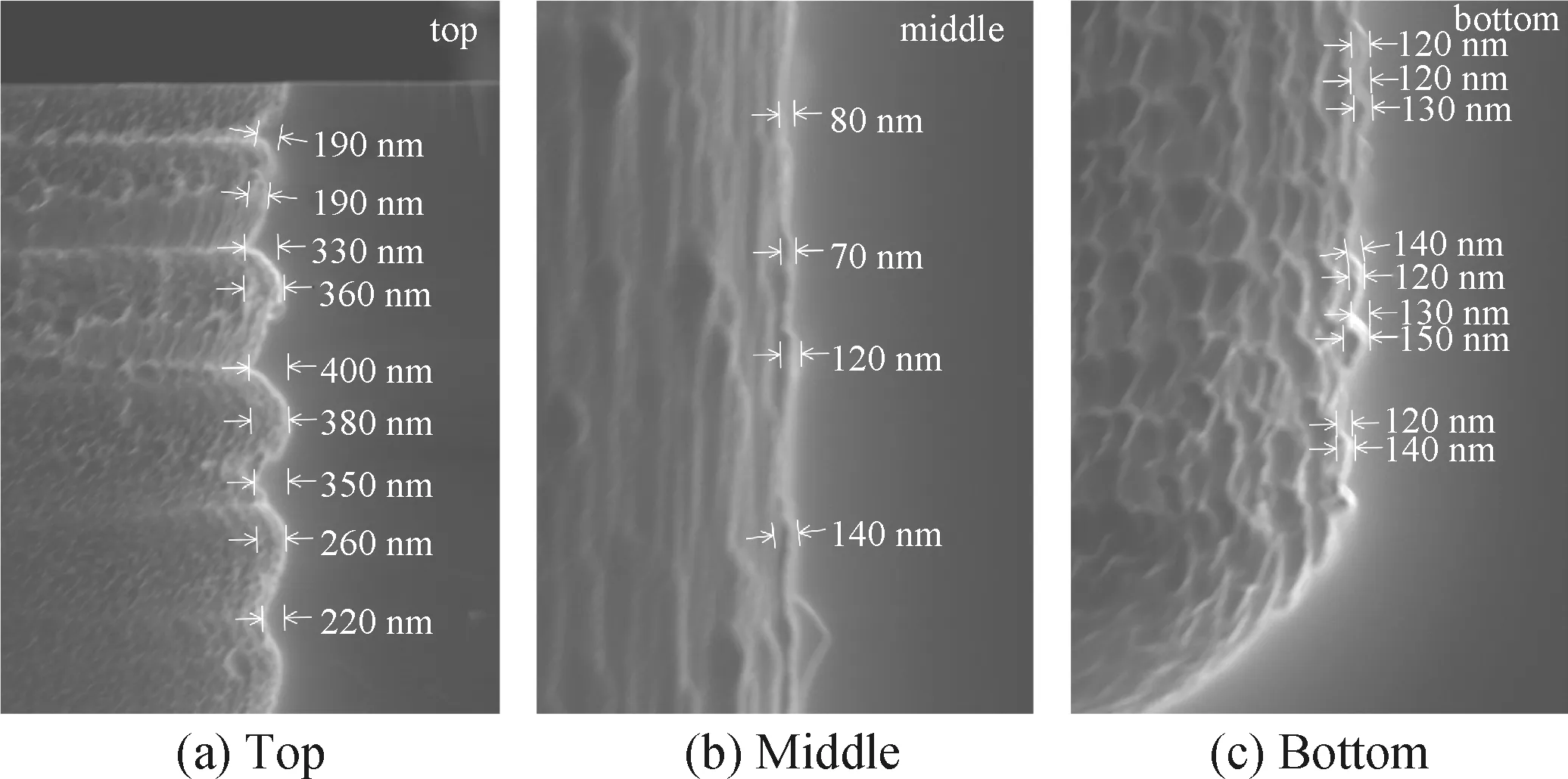

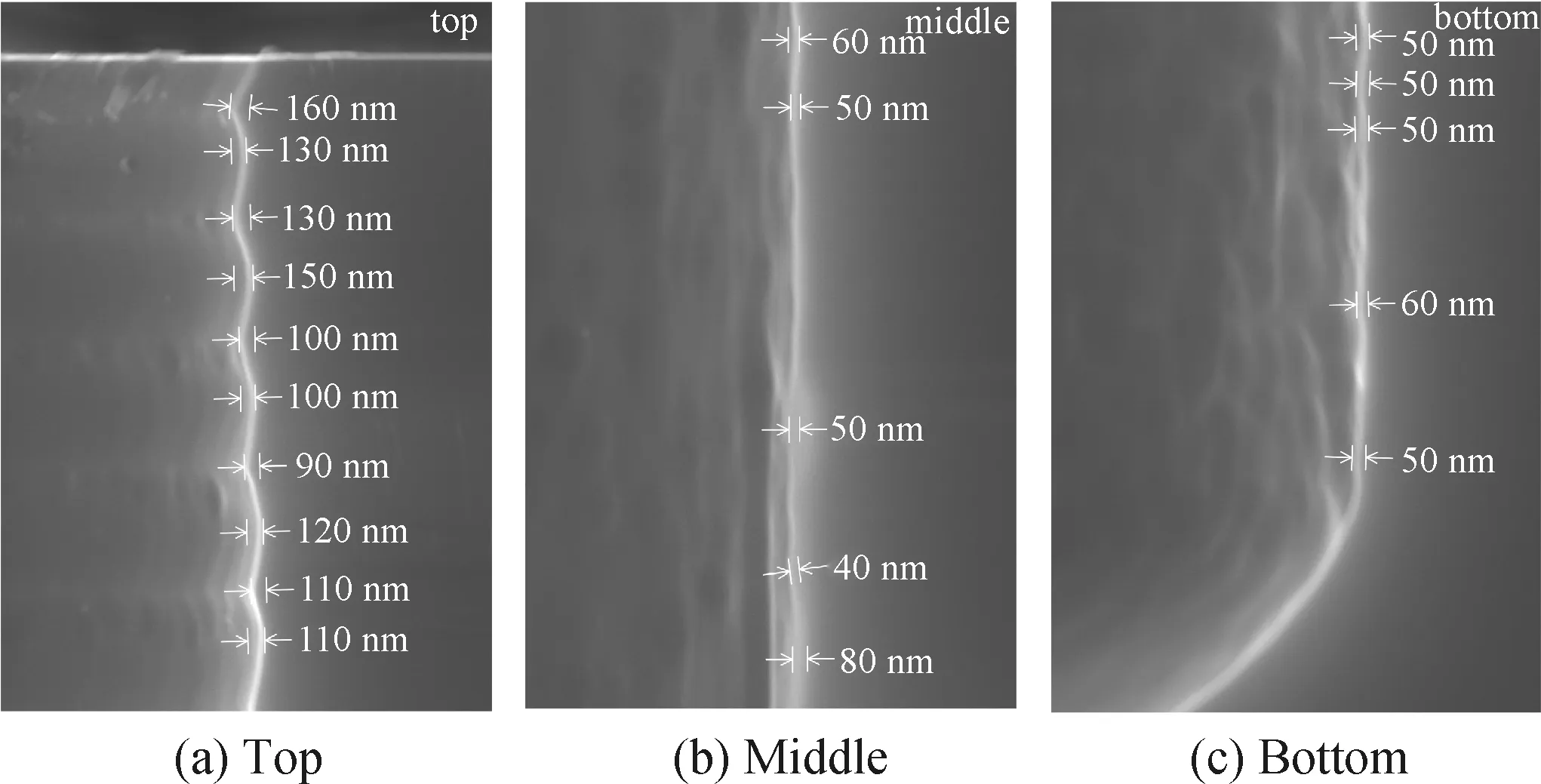

原始硅通孔的SEM照片如圖3所示,從圖中可以看出,硅通孔的頂部、中部和底部的側壁扇貝紋都比較粗糙。硅通孔頂部內壁的扇貝紋起伏最小值為190 nm、最大值為400 nm、平均值為297.8 nm;孔中部內壁的扇貝紋起伏最小值為70 nm、最大值為140 nm、平均值為102.5 nm;孔底部內壁的扇貝紋起伏最小值為120 nm、最大值為150 nm、平均值為130 nm。

圖3 BOSCH刻蝕后硅通孔頂、中、底部內壁扇貝紋的SEM照片Fig.3 SEM images of scallop pattern at the top, middle, and bottom of through silicon via just after BOSCH etching

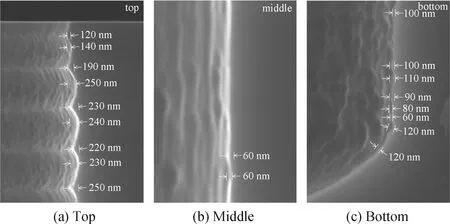

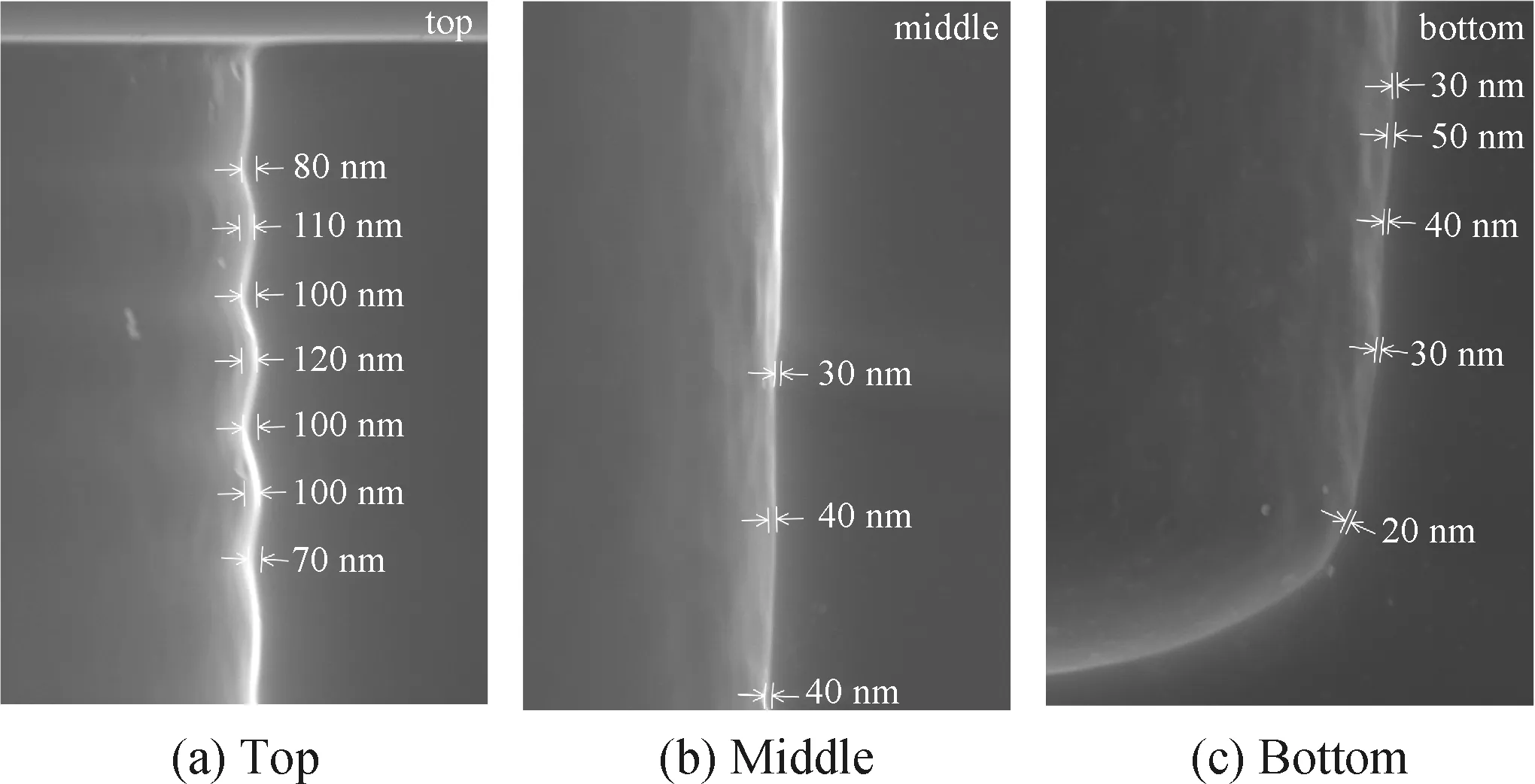

經過一次高溫熱氧化并腐蝕二氧化硅后,硅通孔內壁的扇貝紋起伏明顯降低。從圖4中可以看出,硅通孔頂部內壁的扇貝紋起伏最小值為120 nm、最大值為250 nm、平均值為207.8 nm,相較于原始硅通孔,頂部內壁扇貝紋的平均起伏值減小了90 nm;硅通孔中部內壁的扇貝紋起伏值為60 nm,相較于原始硅通孔,中部內壁扇貝紋的平均起伏值減小了42.5 nm;硅通孔底部內壁的扇貝紋起伏最小值為60 nm、最大值為120 nm、平均值為97.5 nm,相較于原始硅通孔,底部內壁扇貝紋的平均起伏值減小了32.5 nm。

圖4 經過一次高溫熱氧化后硅通孔頂、中、底部內壁扇貝紋的SEM照片Fig.4 SEM images of scallop pattern at the top, middle, and bottom of through silicon via just after once high temperature thermal oxidation

經過二次高溫熱氧化并腐蝕二氧化硅后硅通孔內壁扇貝紋SEM照片如圖5所示。從圖中可以看出,硅通孔頂部內壁的扇貝紋起伏最小值為90 nm、最大值為160 nm、平均值為121 nm,相較于原始硅通孔,頂部內壁扇貝紋的平均起伏值減小了176.8 nm;硅通孔中部內壁的扇貝紋起伏最小值為40 nm、最大值為80 nm、平均值為56 nm,相較于原始硅通孔,中部內壁扇貝紋的平均起伏值減小了46.5 nm;硅通孔底部內壁的扇貝紋起伏最小值為50 nm、最大值為60 nm、平均值為52 nm,相較于原始硅通孔,底部內壁扇貝紋的平均起伏值減小了78 nm。經過第二次氧化之后,相較于第一次氧化,扇貝紋起伏再次降低,側壁粗糙度也相應減小。由于硅通孔中部內壁的扇貝紋相對較小且側壁相對較平滑,所以在第二次高溫熱氧化后,硅通孔中部內壁扇貝紋的削減量相對于頂部和底部就小很多。

圖5 經過二次高溫熱氧化后硅通孔頂、中、底部內壁扇貝紋的SEM照片Fig.5 SEM images of scallop pattern at the top, middle, and bottom of through silicon via just after twice high temperature thermal oxidation

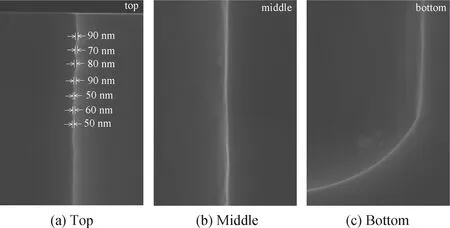

圖6所示是經過三次高溫熱氧化、腐蝕二氧化硅的硅通孔內壁扇貝紋SEM照片。從圖中可以看出, 相較于二次氧化,硅通孔各部位內壁扇貝紋起伏進一步被削減,側壁粗糙度也變得更小。硅通孔頂部內壁的扇貝紋起伏最小值為70 nm、最大值為120 nm、平均值為97 nm,相較于原始硅通孔,頂部內壁扇貝紋的平均起伏值減小了200.8 nm;硅通孔中部內壁的扇貝紋起伏最小值為30 nm、最大值為40 nm、平均值為36.7 nm,相較于原始硅通孔,中部內壁扇貝紋的平均起伏值減小了65.8 nm;硅通孔底部內壁的扇貝紋起伏最小值為20 nm、最大值為50 nm、平均值為34 nm,相較于原始硅通孔,底部內壁扇貝紋的平均起伏值減小了96 nm。

圖6 經過三次高溫熱氧化后硅通孔頂、中、底部內壁扇貝紋的SEM照片Fig.6 SEM images of scallop pattern at the top, middle, and bottom of through silicon via just after three timeshigh temperature thermal oxidation

經過四次高溫熱氧化并腐蝕二氧化硅后,得到硅通孔各部位內壁扇貝紋的SEM照片如圖7所示。從圖中可以看出,經過四次氧化之后,扇貝紋起伏得到了極大的改善,側壁粗糙度在很大程度上減小了,側壁變得平滑。硅通孔頂部內壁的扇貝紋起伏最小值為50 nm、最大值為90 nm、平均值為70 nm,相較于原始硅通孔,頂部內壁扇貝紋的平均起伏值減小了227.8 nm。硅通孔的中部和底部內壁已變得很平滑,SEM測量(實驗用超高分辨場發射掃描電子顯微鏡Regulus8100的最高分辨率為1.1 nm)已分辨不出扇貝紋起伏。

圖7 經過四次高溫熱氧化后硅通孔頂、中、底部內壁扇貝紋的SEM照片Fig.7 SEM images of scallop pattern at the top, middle, and bottom of through silicon via after four times high temperature thermal oxidation

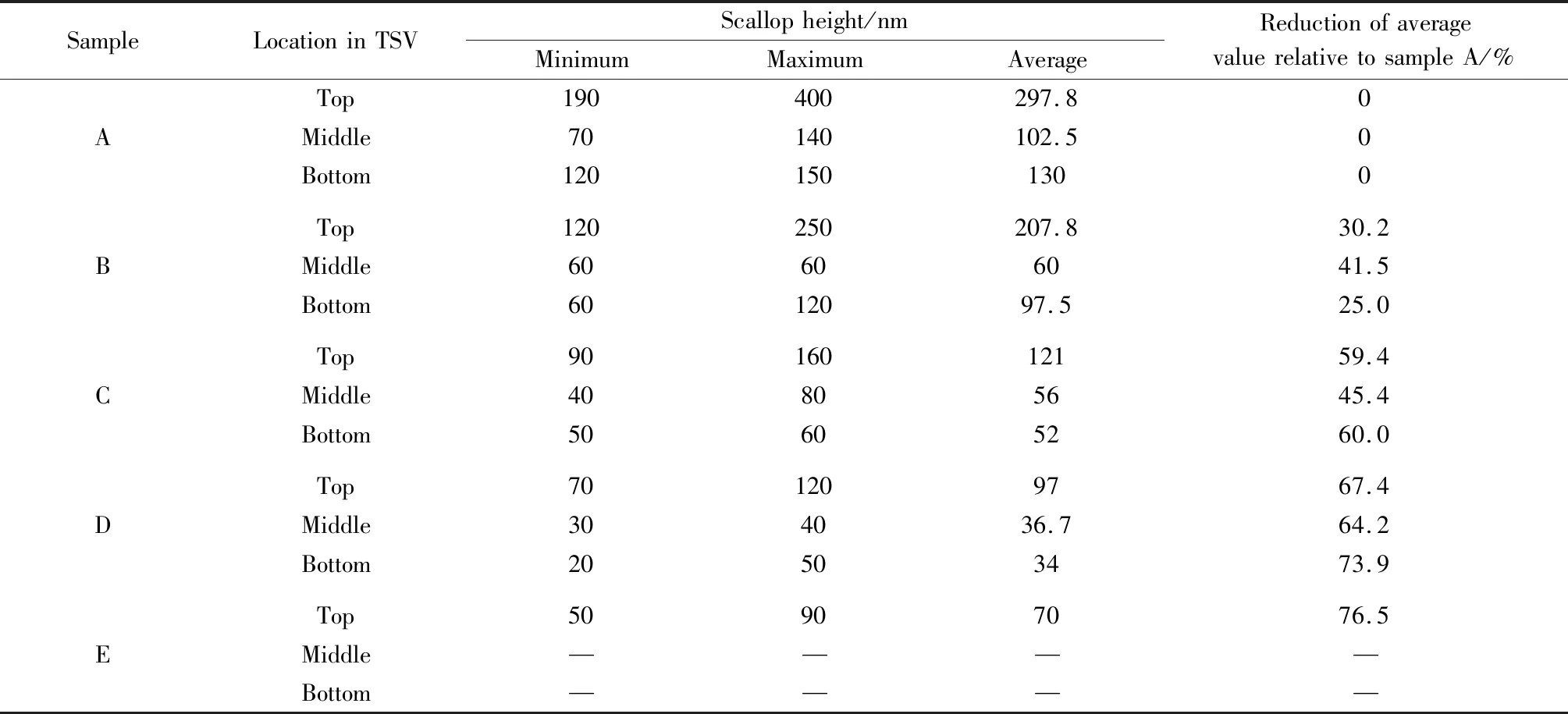

表1統計了每次高溫熱氧化后硅通孔各部位內壁扇貝紋的削減比例。由于硅通孔頂部內壁的扇貝紋起伏較大,逐次高溫熱氧化削減扇貝紋的絕對值較大,扇貝紋起伏的平均值從原始硅通孔中的297.8 nm經過每次高溫熱氧化后分別逐步將為207.8 nm、121 nm、97 nm和70 nm,第一次氧化后就削減了30.2%的扇貝紋起伏,第二次氧化后又在第一次氧化的基礎上有削減了29.2%,前兩次氧化削減扇貝紋起伏的比例接近,分析認為這是因為原始硅通孔和第一次氧化后的硅通孔(如圖3和圖4所示)頂部內壁都較粗糙,氧化層生長速率較快。第三次和第四次高溫熱氧化在上一次氧化的基礎上削減扇貝紋起伏的比例分別為8%和9.1%,削減扇貝紋的比例明顯下降,因為從圖5和圖6中可以看出,硅通孔頂部內壁明顯變得平滑了。經過四次高溫熱氧化后扇貝紋起伏的平均值相較于原始硅通孔的降幅為76.5%。與頂部和底部相比,硅通孔中部內壁的扇貝紋起伏較小。由于硅通孔側壁很陡峭,又由于氧氣流向平行于硅通孔的側壁,第一次氧化后孔中部內壁的扇貝紋起伏就被削減了41.5%,是三個部位中減幅最大的。第二次和第三次氧化后削減硅通孔中部內壁扇貝紋的幅度減緩,相對于上一次氧化分別又削減了3.9%和18.8%,出現如此大的減幅差異有可能是因為兩次氧化后測量的不是同一個硅通孔,孔與孔之間存在差異。對于硅通孔底部內壁,第一、第二、第三次高溫熱氧化后分別削減扇貝紋起伏的比例為25%、35%、13.9%,到第三次后扇貝紋減幅就明顯下降,因為扇貝紋的絕對高度變小了。

表1 五種條件的樣品扇貝紋起伏以及每次高溫熱氧化對硅通孔頂、中、底部內壁扇貝紋削減比例統計Table 1 Scallop height of samples under five conditions and the reduction of average scallop height of each high temperature thermal oxidation at the top, middle, and bottom of through silicon via

4 結 論

BOSCH刻蝕技術刻蝕硅通孔時在孔內壁形成的扇貝紋會嚴重影響后續填充材料的質量以及填充的各層材料界面的微觀結構。削減扇貝紋,使硅通孔內壁變得平滑,不僅能顯著提升硅通孔的性能以及三維集成系統的可靠性,還有利于孔內各層材料的填充。本文介紹了一種通過“高溫熱氧化+腐蝕二氧化硅”多次交替循環削減硅通孔內壁扇貝紋的實驗方法。實驗結果表明,經過四次高溫熱氧化后,孔徑為10 μm、孔深為80 μm的圓柱形硅通孔中部和底部內壁的扇貝紋基本被削平,硅通孔頂部的扇貝紋起伏從297.8 nm削減到了70 nm,孔的內壁變得平滑。