多工作模式的刷新成像系統

李 波,余 達,劉金國,孔德柱,梅 貴,陳佳豫,趙 瑩

(中國科學院 長春光學精密機械與物理研究所,吉林 長春 130033)

1 引 言

大容量SRAM型現場可編程邏輯器件(Field Programmable Gate Array,FPGA)功能強大,在空間成像領域如空間監視、遙感成像中有廣泛的應用[1-3]。由于復雜的空間輻照環境和SRAM型FPGA自身的結構工藝,該類器件在軌易受單粒子翻轉效應(Single Event Upset,SEU)影響,導致成像功能異常,在成像探測器上電配置期間出現翻轉有損壞器件的風險,需要進行輻射加固。常見的SEU加固措施包含三模冗余、糾錯編碼、局部重配置和配置刷新等[4-6]。其中三模冗余資源占用率高,長時間工作可能導致故障累積而失效,適用于邏輯關系故障;糾錯編碼占用資源更少,編碼簡單時檢測和糾錯有限,編碼復雜時會降低數據傳輸速率,適用于BRAM翻轉故障;動態重配置主要針對器件發生的永久物理故障,而配置區受SEU的影響能通過刷新方式解決,配置期間不能工作[7-10];刷新技術[11-14]通過將正確的配置幀信息寫入FPGA可以較好地修復SEU。刷新方法常使用對輻照不敏感的反熔絲FPGA對刷新過程進行控制,但軟硬件設計復雜。另一種刷新方法是使用專用的定時刷新芯片,設計難度和復雜度可大幅降低[15]。

上海復旦微公司的刷新芯片JFMRS01RH,采用SMIC 0.18 μm CMOS工藝和DICE設計加固方法,具有自身可靠性高、抗輻射能力強,可以定時檢測FPGA的SEFI狀態并刷新FPGA,削減單粒子的累積效應。該芯片支持可編程只讀存儲器(PROM)、SPI FLASH、異步NOR FLASH存儲器件,提供對異步NOR FLASH、SPI FLASH的編程、全芯片擦除、扇區擦除、數據校驗、數據回讀功能,同時提供對PROM的數據回讀功能。JFMRS01RH支持復旦微電子公司研制的JFM4V系列和JFM7V系列FPGA器件,以及Xilinx公司主流FPGA[16]。該器件通過串口即可實現復雜的操作,但其串口不支持菊花鏈工作方式,而且波特率為固定的115.2 bit/s,不可調整。若刷新成像系統中每片FPGA和刷新芯片都各配置一組串行總線,則整個刷新成像系統的電纜數量龐大;若使用FPGA對刷新芯片串口控制,則可能由于二者的相互控制陷入工作不正常的死循環。該刷新芯片應用不方便的另一方面,是在器件加電后就立即啟動FPGA配置操作,而FPGA由于配置過程電流大通常采用分步上電方式,從而容易出現刷新芯片控制下的FPGA加載失敗。若完全依靠刷新芯片進行成像系統控制,當刷新芯片出現損壞或者工作異常,則整個成像系統失敗;在調試過程中出現異常,也難進行問題定位,因此需要進行多工作模式的設計。最后,刷新成像系統需要在軌軟件重注功能,可根據在軌的應用需求,實現刷新成像系統的功能重構。

2 多工作模式的刷新成像系統設計

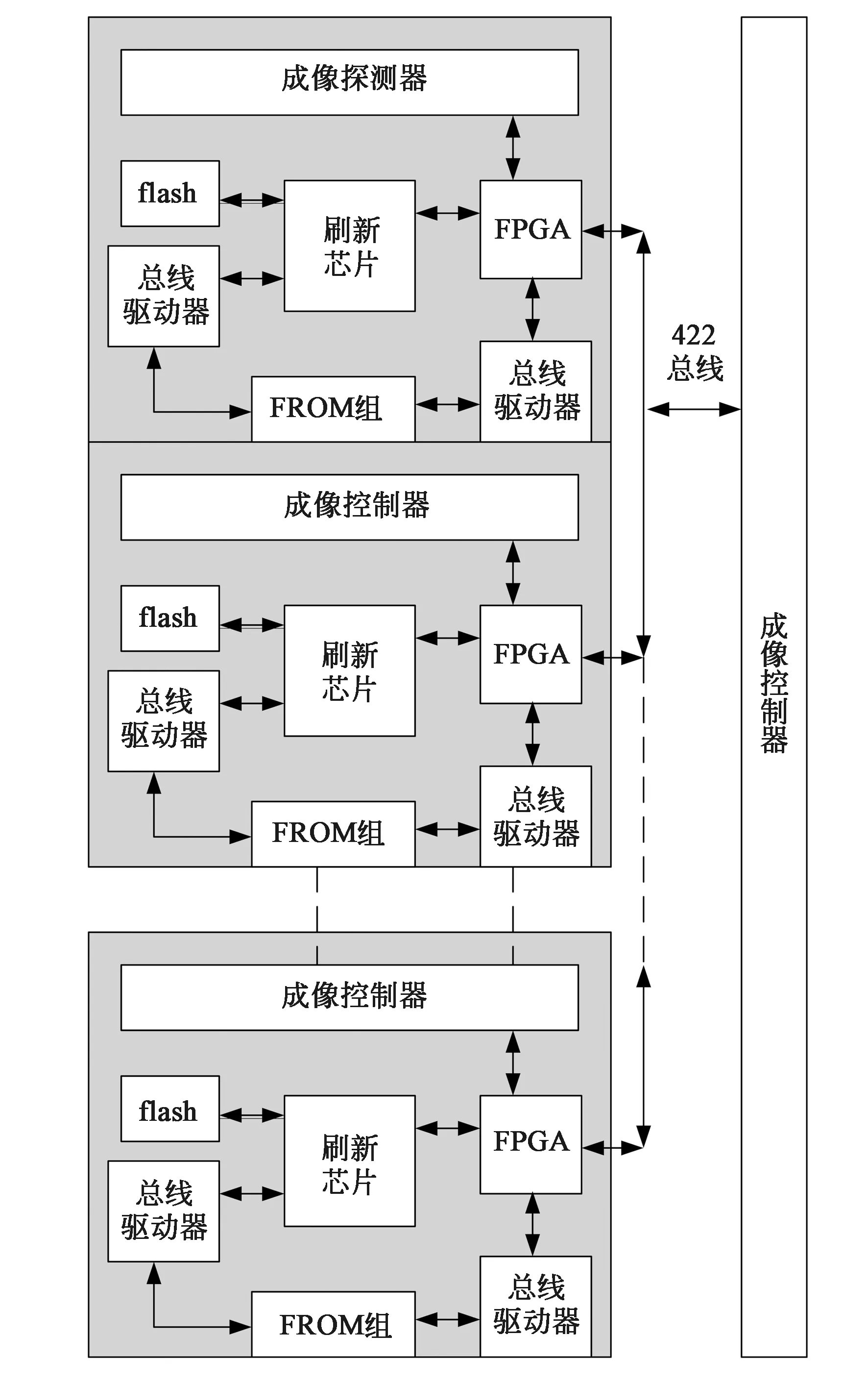

刷新成像系統包含多組刷新成像單元和主控。刷新成像單元包含刷新芯片、FPGA、flash、PROM組、總線驅動器和成像探測器。flash直接與刷新芯片相連,受刷新芯片控制,用于接收待更新的配置數據。PROM與FPGA之間、FPGA與刷新芯片之間采用總線驅動器實現通路的切換。FPGA產生成像探測器工作所需的相關工作時序,并接收成像探測器輸出的圖像數據。主控通過邏輯控制信號和菊花鏈結構的串行422總線對各成像單元刷新配置過程進行控制。然而,串行422總線直接與FPGA相連,FPGA通過解析主控的422命令,產生響應的控制命令并將接收到的配置數據通過刷新芯片的串口寫入與刷新芯片相連的flash中。

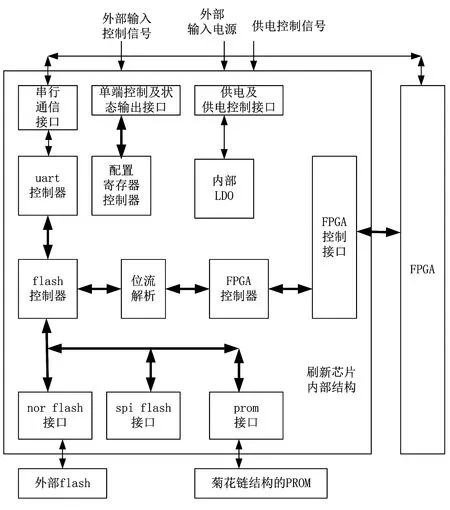

2.1 刷新芯片JFMRS01RH電路

在軌刷新成像系統如圖1所示,刷新芯片JFMRS01RH內部結構如圖2所示。可通過外部的控制信號或者串行通信接口進行刷新芯片內部配置寄存器的狀態控制,刷新芯片的內核可外部供電,而與可選擇使用內部的LDO供電;刷新芯片可通過讀取FPGA內部的配置信號,與指定的配置數據源進行對比,進行位流解析,產生相應的控制;也通過串行接口,接收重注程序,編程寫入外部flash中。

圖1 在軌刷新成像系統Fig.1 On-orbit refresh imaging system

圖2 刷新芯片JFMRS01RH內部結構Fig.2 Internal structure of refresh chip JFMRS01RH

2.2 成像處理電路

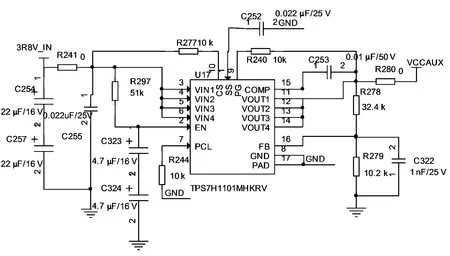

成像處理電路中FPGA采用Xilinx公司的V5系列FPGA XQ5VFX100tff1136M,最大可用680個管腳,內部包含8 208 kbit的塊RAM資源和256個DSP48E資源[17]。成像處理需要多種供電電源,為盡量降低成像電箱的總功耗,成像處理擬采用3種供電電源。此部分主要采用TI公司的TPS7H1101MHKRV進行供電(圖3),其中由于FPGA內核電流大,采用VPT公司的點負載DS-DVPL0510S-5.0供電;外部接口電路和刷新成像部分采用LS883進行供電。

圖3 TPS7H1101MHKRV供電電路Fig.3 Power supply circuit based on TPS7H1101MHKRV

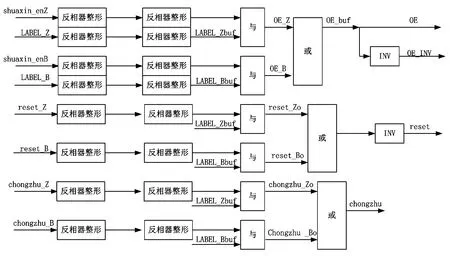

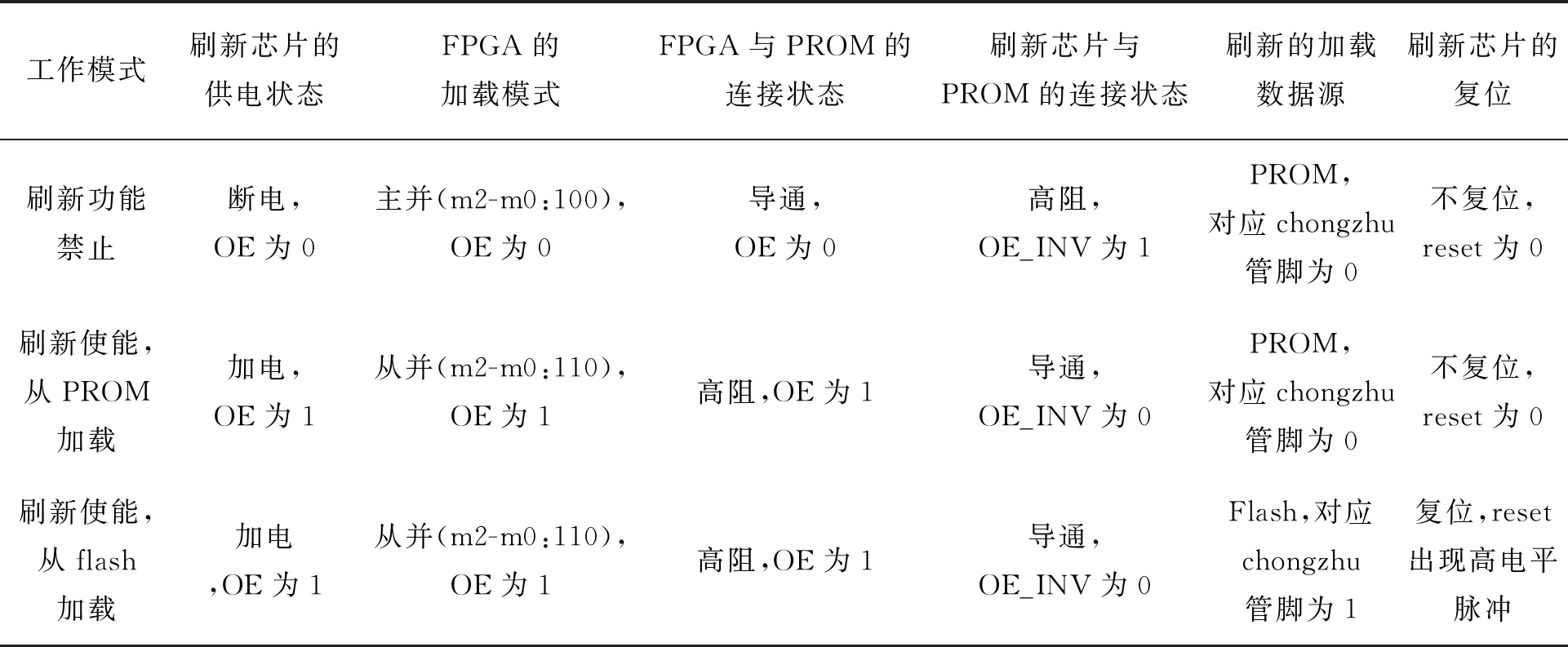

刷新成像成像系統具有3種成像工作模式,如圖4和表1所示:

圖4 刷新成像控制邏輯流程圖Fig.4 Refresh imaging control logic flow chart

表1 3種工作模式下的電流及狀態Tab.1 Current and status in three working mode

(1)刷新功能禁止模式。主控發出的控制信號使刷新使能處于無效的低電平。FPGA為主并工作模式,直接從PROM加載數據,刷新芯片的供電處于禁止狀態。

(2)從PROM加載的在軌刷新模式。刷新芯片的供電輸出使能,主控發出的控制信號刷新使能處于有效的高電平,重注使能處于無效的低電平。FPGA為從并工作模式,加載過程受刷新芯片控制,刷新芯片的串口是受FPGA控制,通過外部復位,刷新芯片的加載配置信號取決于外部的管腳電平信息,刷新芯片的管腳電平為默認從PROM加載。

(3)從flash加載的在軌刷新模式。刷新芯片的供電輸出使能,主控發出的控制信號刷新使能處于有效的高電平,重注使能處于無效的低電平。FPGA為從并工作模式,加載過程受刷新芯片控制,刷新芯片的串口是受FPGA控制,通過外部復位,刷新芯片的加載配置信號取決于外部的管腳電平信息,刷新芯片的管腳電平為從修改了程序的flash加載。

3 測試結果

3.1 多工作模式加載結果

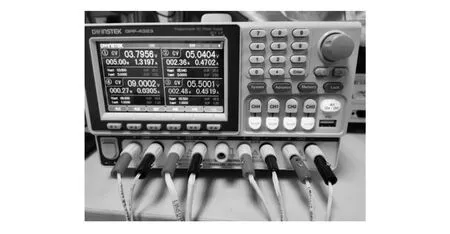

表2為不同工作模式下的加載結果,具體表現為工作電流的變化,如圖5所示。

圖5 未刷新使能的工作電流Fig.5 Operating current without refresh enable

表2 不同加載模式下的供電電流Tab.2 Supply current in different loading modes

3.2 刷新驗證結果

(1)不刷新使能,燒入新的bit文件

刷新成像系統運行正常,輸出正常的感光圖像。

(2)刷新使能,燒入新的bit文件

刷新成像系統在正常攝像的狀態下,通過JTAG口燒入新的bit流,燒入成功,結果輸出圖像的攝像狀態停止了,重新發送攝像命令,然后才開始繼續輸出圖像。說明刷新功能僅能實現恢復回原始的bit,并不能恢復回發生SEU前的狀態,除非對配置相關外的數據進行三模冗余。

3.3 重注驗證

(1)每包編程數據返回遙測值:編程成功。

(2)位流CRC校驗結果:位流CRC校驗成果。

(3)回讀數據與編程數據的對比結果:回讀數據與編程數據相同。

3.4 加載重注

刷新成像系統中FPGA芯片XQ5VFX100T的配置數據在刷新芯片的控制下,0.6 s內可完成上電加載配置(圖6)。直接使用復旦微公司的上位機軟件,刷新芯片串口波特率為固定的115.2 kbit/s,單包204 byte有效數據外還需要添加27 byte的幀頭、幀長等數據,傳輸效率為88.3%,傳輸時間為2.01 ms。采用422串口助手,串行控制信號的波特率為625 kbit/s,單包204 byte有效數據外還需要添加32 byte的幀頭、幀長、同步碼、地址碼等數據,傳輸效率為86.4%,傳輸時間為0.377 6 ms。

圖6 FPGA加載配置時間長度測量結果Fig.6 Measurement length of FPGA load configuration time

4 結 論

本刷新成像系統可以實現FPGA配置數據源為PROM的主并工作方式加載,在刷新芯片控制下的配置數據源為PROM從并工作方式,也可以實現配置數據源為flash的從并工作方式,因此該系統具有很高的可靠性。可通過外部串行總線進行各組刷新程序的分時更新,因此具備設計靈活性和在軌可維護性。通過JTAG口燒入與加載數據不同位流,在刷新使能狀態下會恢復為原數據流,證明刷新芯片能把改寫的位流恢復,具備防單粒子的功能。要保證寄存器等數據不因單粒子事件而改寫,還需要結合三模冗余等措施對關鍵信號和數據進行保護。