圖像處理算法IP核的異構驗證框架

趙 陸,文建平*,莫 為,陳仕睿,李項河

(1.西安科技大學機械工程學院,陜西 西安 710054;2.陜西科技控股集團有限責任公司,陜西 西安 710000;3.西安西微智能科技有限公司,陜西 西安 710000)

1 引 言

數字圖像處理從日常生活到工業生產的各個領域,都扮演著重要的角色[1]。由于圖像分辨率的提升和圖像處理算法的復雜化,傳統的串行處理器已難以滿足圖像處理的實時性需求。隨著芯片制作工藝的不斷提高,單一芯片能夠承載更多的功能,以預處理和特征提取為任務的圖像處理算法或機器視覺算法經過優化后,移植為具有一定功能的電路模塊(Intellectual Property core,IP核),集成在片上系統(SoC)或應用在現場可編程門陣列(FPGA)成為解決實時圖像處理任務的一個新的研究方向[2-3]。

隨著SoC和FPGA設計規模的不斷增大,IP核的獨立正確性成為了系統正常工作的基本保證。在芯片設計的整體流程中,驗證占據了70%的工作量[4-5],如何對IP核進行實時、有效的驗證成為硬件設計的關鍵。使用EDA仿真軟件對設計進行動態模擬是最為廣泛的功能驗證方法,經過設計人員的不斷完善,已發展出了成熟的驗證方法學(UVM)[6-7]。雖然具有良好內部信號可見性、實時調試性和可重用性,但使用EDA軟件進行仿真時,大量的驗證激勵會使得驗證周期長達數日。為了克服軟件仿真驗證周期長的問題,FPGA原型驗證成為最有效的解決方法之一。文獻[8]使用FPGA對LSD直線檢測算法IP核進行功能驗證。文獻[9]使用FPGA針對Canny算子IP核構建了功能原型。但由于FPGA原型驗證需要圍繞待驗證的設計,有針對性地構建測試框架,給設計人員帶來了極大的不便。為了解決該問題,研究人員嘗試使用軟硬件結合的方式,在保證FPGA仿真效率優勢的同時,增加驗證框架的復用性。文獻[10]使用SoC器件的硬核處理器作為激勵的發生單元和驗證覆蓋率分析單元,避免因修改激勵而使得FPGA全局重新配置,但在圖像處理算法IP核的驗證任務中,測試激勵是類型各異的視頻流,無法通過硬核處理器產生。文獻[11]提出了一種基于軟硬件協同仿真的IP核驗證平臺,平臺由PC端的Leon3 SoC模擬環境和FPGA端基于Microblade軟核搭建的SoPC仿真環境組成,兩者通過以太網進行鏈接,但受限于軟核的處理速度,PC端和FPGA端的通信速率無法承擔測試視頻流的傳輸。文獻[12]開發的框架提供了一個驗證覆蓋庫,通過驗證覆蓋和待測IP的組合,實現FPGA的完整配置。該覆蓋庫減輕了為特定設計搭建驗證框架的壓力,但為保證驗證覆蓋的可重用性,覆蓋只針對通用接口構建了基礎結構,缺少對圖像數據的兼容性。文獻[13]構建了FPGA與主機的信息交換系統,提出了使用FPGA聯合上位機軟件進行數字電路測試和驗證的思路,但文中只驗證了系統收發信息的有效性,沒有針對復用性對軟硬件進行協同設計。本文基于FPGA原型驗證技術,使用集成ARM(Advamced RISC Machine)和FPGA的異構平臺聯合上位機軟件,針對圖像處理算法IP核構建驗證框架。通過軟硬件的協同設計保證了驗證框架對不同圖像處理算法IP核的驗證兼容性和實時性,并通過部分重配置技術快速更替待驗證算法IP核,提高了驗證框架的穩定行和敏捷性。

2 圖像處理算法IP核驗證方法

圖像處理算法向數字電路移植的過程中,首先采用C或者python等高級語言構建圖像處理算法模型,然后使用RTL代碼對構建的模型進行描述和移植,C/Python模型被用作IP開發的理想參考模型[14]。在使用FPGA對圖像處理算法IP核的功能進行驗證時,由于圖像處理算法的特殊性,存在著以下難點:

(1)激勵圖像的分辨率和位深度具有多樣性,對FPGA硬件架構的兼容性提出了較高的要求。

(2)圖像處理算法的應用場景及目標具有很大的差異性,相應的測試圖像呈現多樣性,無法通過SoC中的硬核處理器自發產生激勵圖像。

(3)圖像處理算法IP核的更改會導致整個框架的重配置,降低了圖像處理算法IP核的迭代速度。

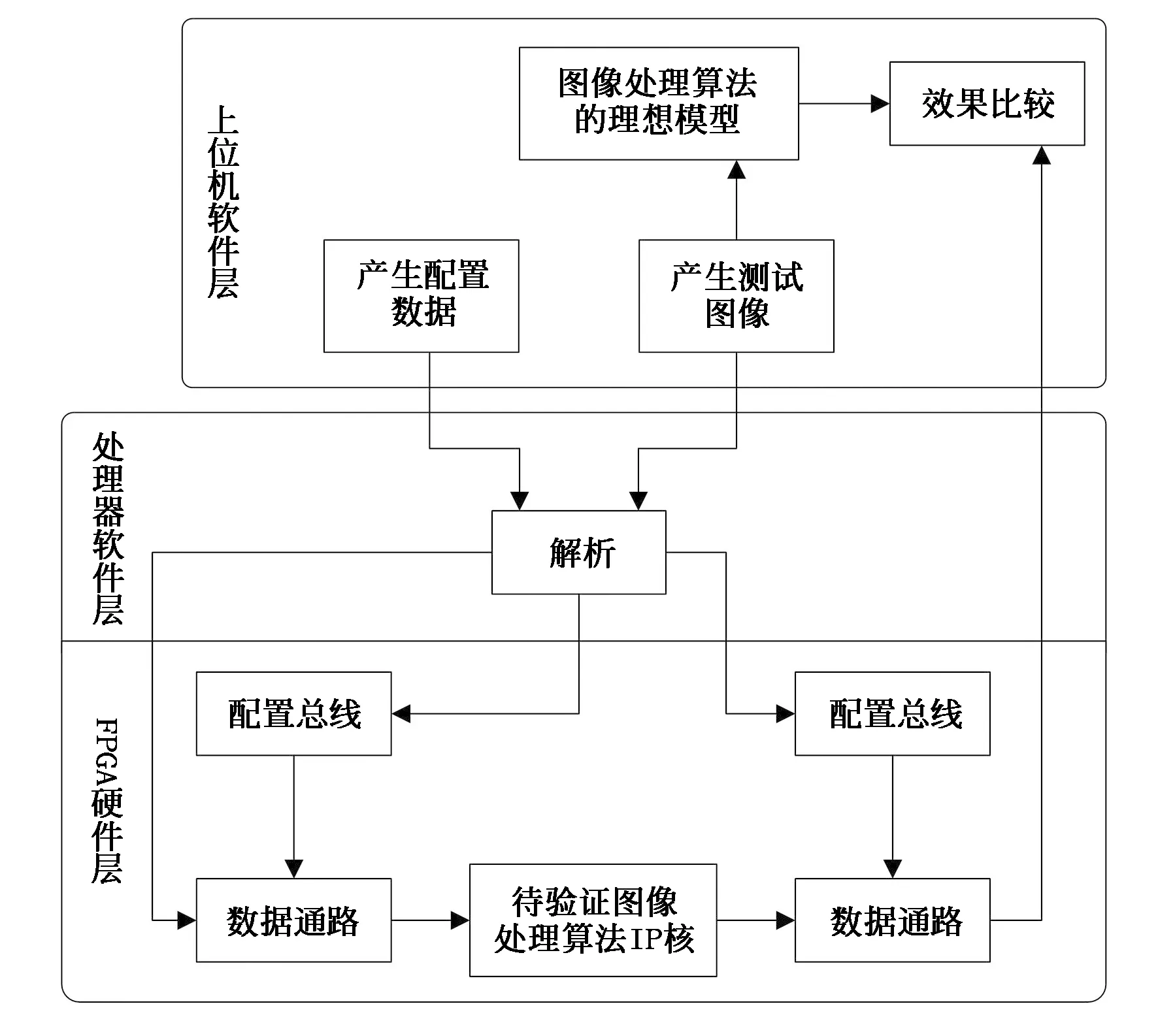

針對以上存在的難點,本文提出了如圖1所示的驗證方法。首先在FPGA硬件層中針對圖像處理算法IP核的輸入和輸出預先搭建了兼容多類型圖像數據的傳輸通路,再由上位機MATLAB軟件發送,處理器軟件層解析的配置數據經由配置總線實現數據通路的動態配置,進而保證了驗證框架的泛用性;上位機MATLAB軟件根據待驗證算法IP核的需求產生測試視頻流,一方面發送給由高級語言構建的圖像處理算法理想模型,另一方面由處理器軟件層解析后,經由配置后的數據通路發送到待驗證的算法IP核中,通過比較二者的測試響應實現IP核的功能驗證;待驗證算法IP核作為部分重配置模塊,在形成完整構型時避免了配置總線與數據通路的重配置,在保證框架穩定性的同時,加快了待驗證IP核的部署速度。

圖1 圖像處理算法IP核驗證思想Fig.1 Verification idea of IP core for image processing algorithm

3 驗證框架設計

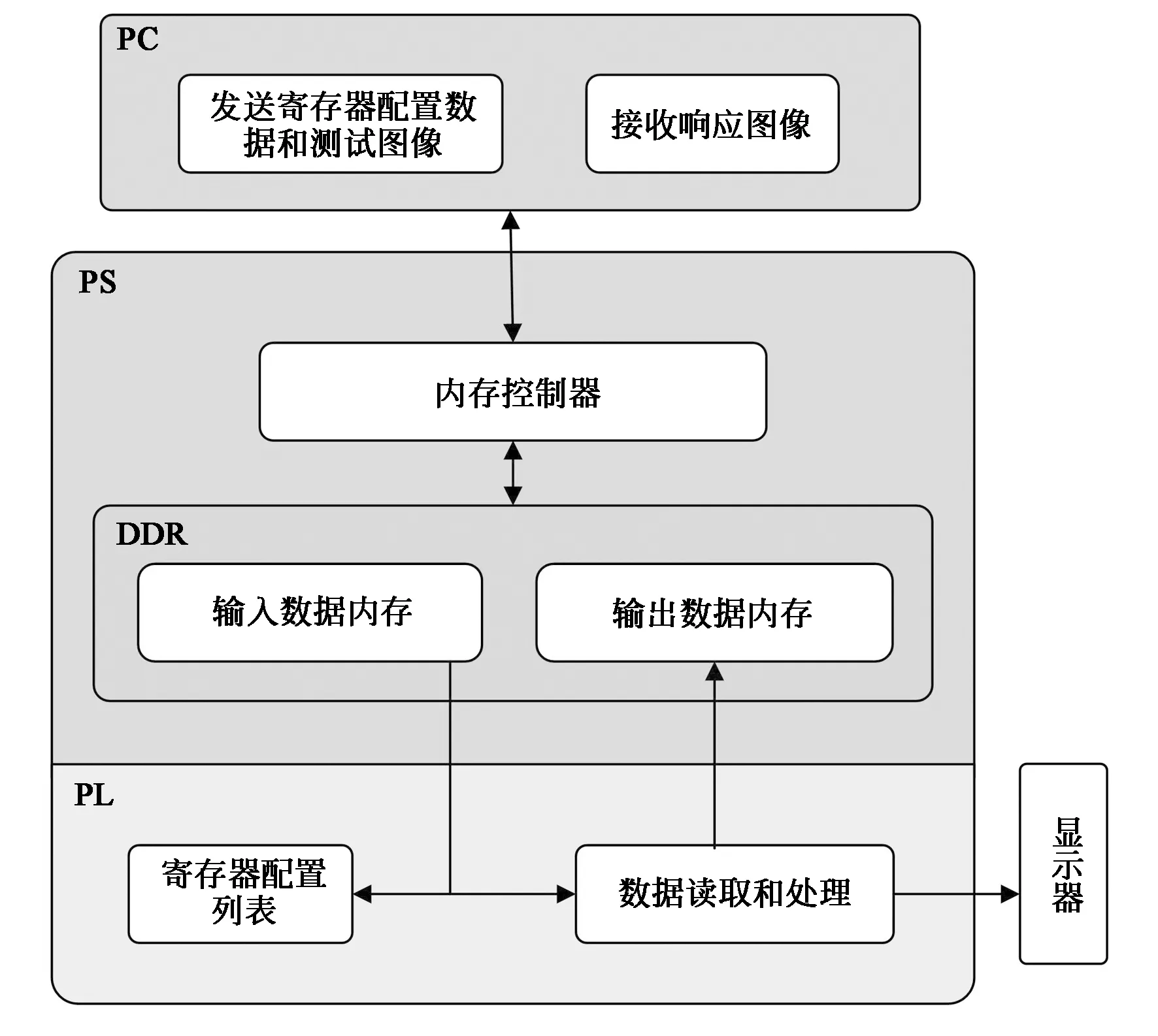

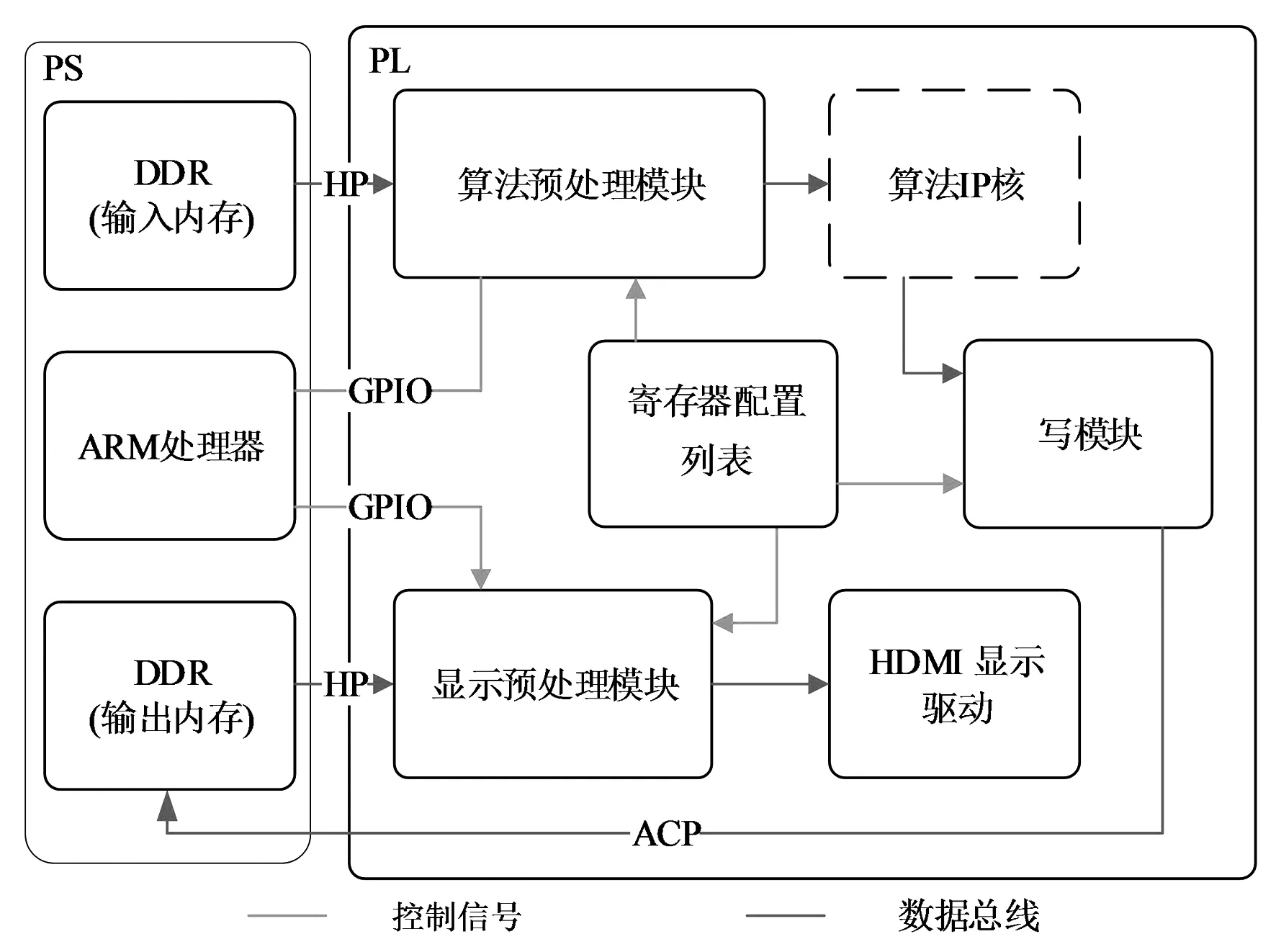

驗證框架由集成處理器系統(Processing System,PS)和可編程邏輯(Programmable Logic,PL)的SoC聯合上位機軟件構成。PS包括ARM處理器、內存控制器、千兆以太網控制器、USB控制器等。PL擁有標準FPGA的結構,二者通過從低速到高速的一系列接口進行通信。如圖2所示,上位機使用MATLAB軟件產生測試圖及相應配置數據。PS端與上位機建立以太網通信,并進行數據的解析和調度。PL端對接收的圖像數據進行處理、計算和顯示。該框架能夠兼容以8,16,24 bit位深度圖像為對象的算法IP核的驗證工作,并具有良好的擴展性。

圖2 系統架構Fig.2 System framework

3.1 PS端軟件開發

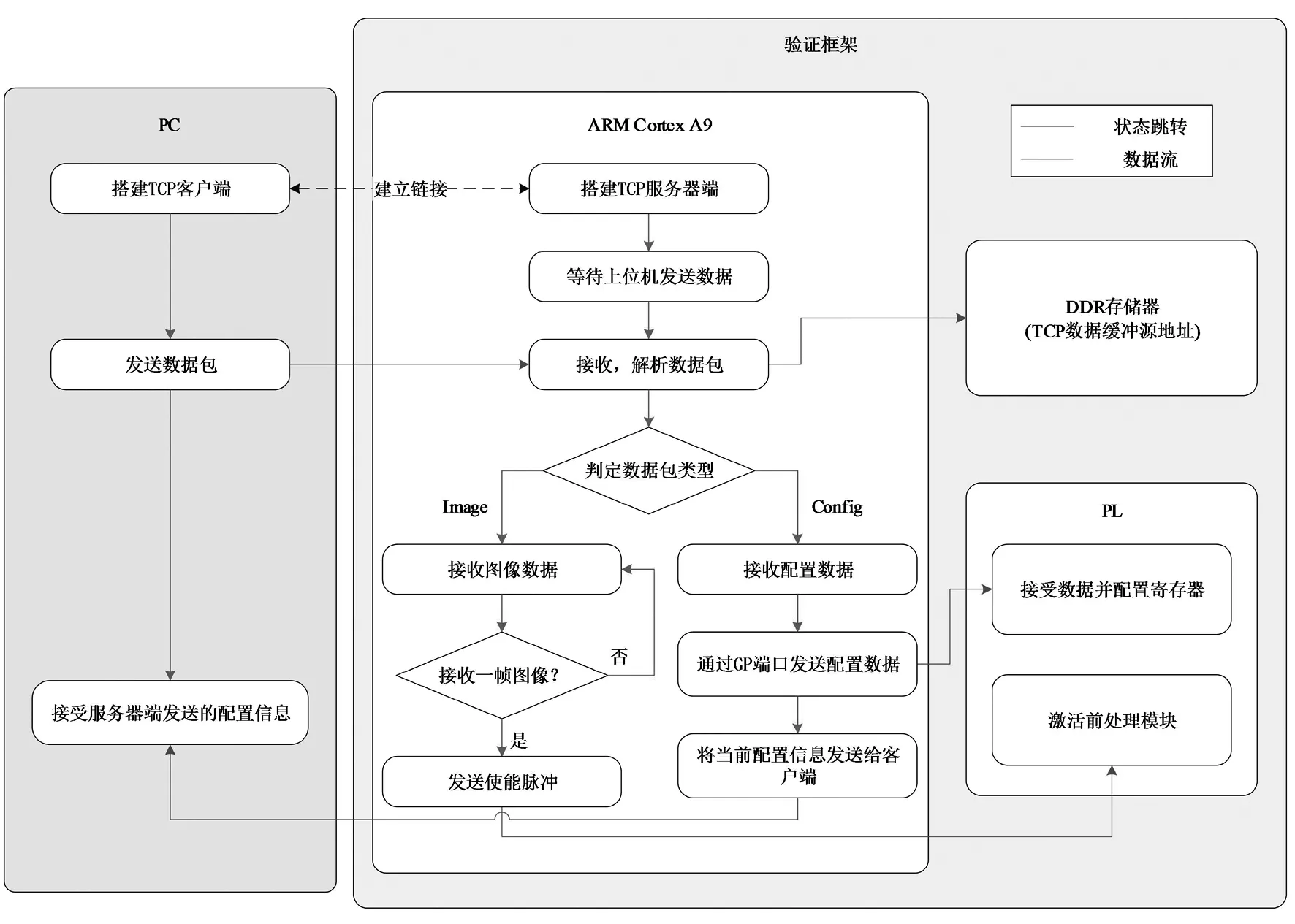

由自身特性決定,FPGA對并行數據具有很好的處理實時性,而不善于處理串行指令,雖然可以通過在FPGA內部搭建軟核的方法實現軟件編程,但軟核會占據較多的邏輯資源并且處理性能有限。ARM硬核處理器則很好地彌補了FPGA在事務管理方面的不足。本設計采用PS完成與上位機的通信、數據的交互、任務的調度等,其整體架構如圖3所示。

圖3 PS端軟件處理流程圖Fig.3 PS software processes flowcharts

由于視頻流的傳輸需要較大的帶寬,在上位機和驗證框架之間建立TCP/IP協議棧,實現千兆以太網通信,保證驗證框架對視頻流處理的實時性。為降低協議對RAM資源的占用并增強驗證框架的泛用性,采用Light Wight IP協議中的Socket API進行網絡開發,上位機使用MATLAB軟件與驗證框架進行連接。在圖像傳輸之前,需要對處理框架進行配置以兼容各種類型和大小的圖像數據,如圖3所示。

配置數據包由上位機發送給PS端,PS端進行解析后,通過GP口配置PL端寄存器,實現硬件架構對于不同類型和分辨率圖像的兼容處理。在該框架中,PL端擁有256個可配置寄存器,對應地址范圍0~255,其中地址0~5對應的寄存器為基礎寄存器,該部分寄存器必須在發送測試圖像之前進行配置;地址6~255是預留地址段,可進行拓展配置。基礎寄存器的配置數據如表1所示。

表1 寄存器配置數據Tab.1 Register configuration data

3.2 PL端邏輯設計

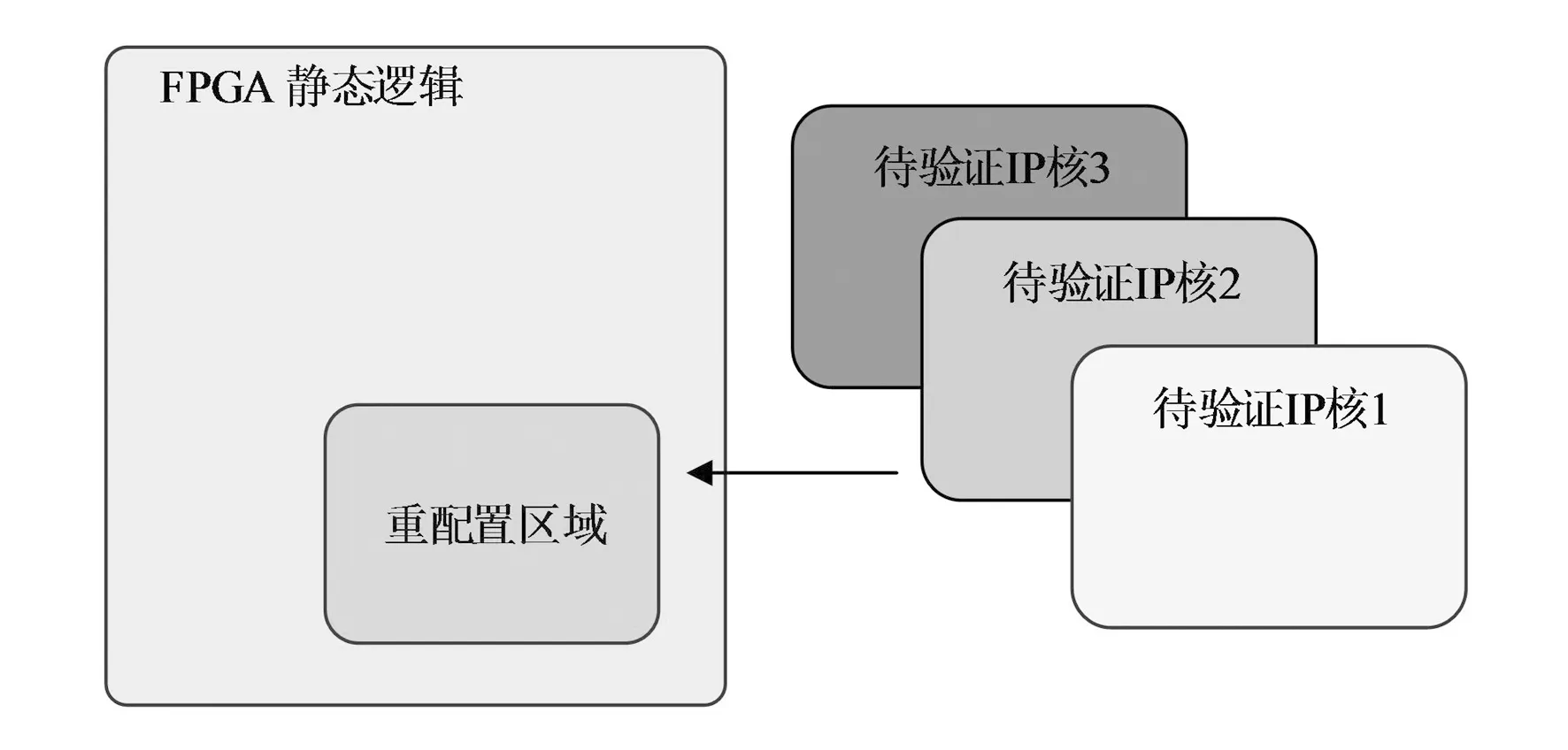

由于算法IP核驗證任務的特殊性,在實際應用中需要分時對待驗證的IP核進行替換,為加快圖像處理算法IP核部署速度,提高FPGA中硬件邏輯的穩定性,使用部分重配置技術將PL的邏輯資源分為靜態區域和部分重配置區域。如圖4所示,待驗證IP核作為部分重配置模塊,能夠在鎖定FPGA靜態邏輯的同時實現更替,既避免了待驗證IP核的部署對靜態邏輯時序的影響,又加快了算法IP核在FPGA上的部署速度[15]。

圖4 部分重配置Fig.4 Partial reconfiguration

靜態邏輯的任務是為圖像處理算法IP核搭建具有高度泛用性的數據輸入和輸出通道,并將處理結果發送給顯示器。如圖5所示,靜態邏輯由預處理模塊、寄存器配置列表、寫模塊和HDMI驅動模塊組成。當PS端收到圖像數據包并完成解析后,通過通用輸入輸出接口(General-purpose input/output,GPIO)發送脈沖激活算法預處理模塊與顯示預處理模塊,然后,算法預處理模塊通過高性能接口(High Performance,HP)將內存中輸入地址的圖像數據讀出進行格式化,并輸出給算法IP核計算,計算后的結果發送到寫模塊中,利用加速器一致性接口(Accelerator Coherency Port,ACP)將處理結果寫入內存的輸出地址中。輸出地址中的數據通過顯示預處理模塊和高清多媒體接口(HDMI)顯示驅動模塊輸出給顯示器。

圖5 PL整體架構Fig.5 Overall structure of PL

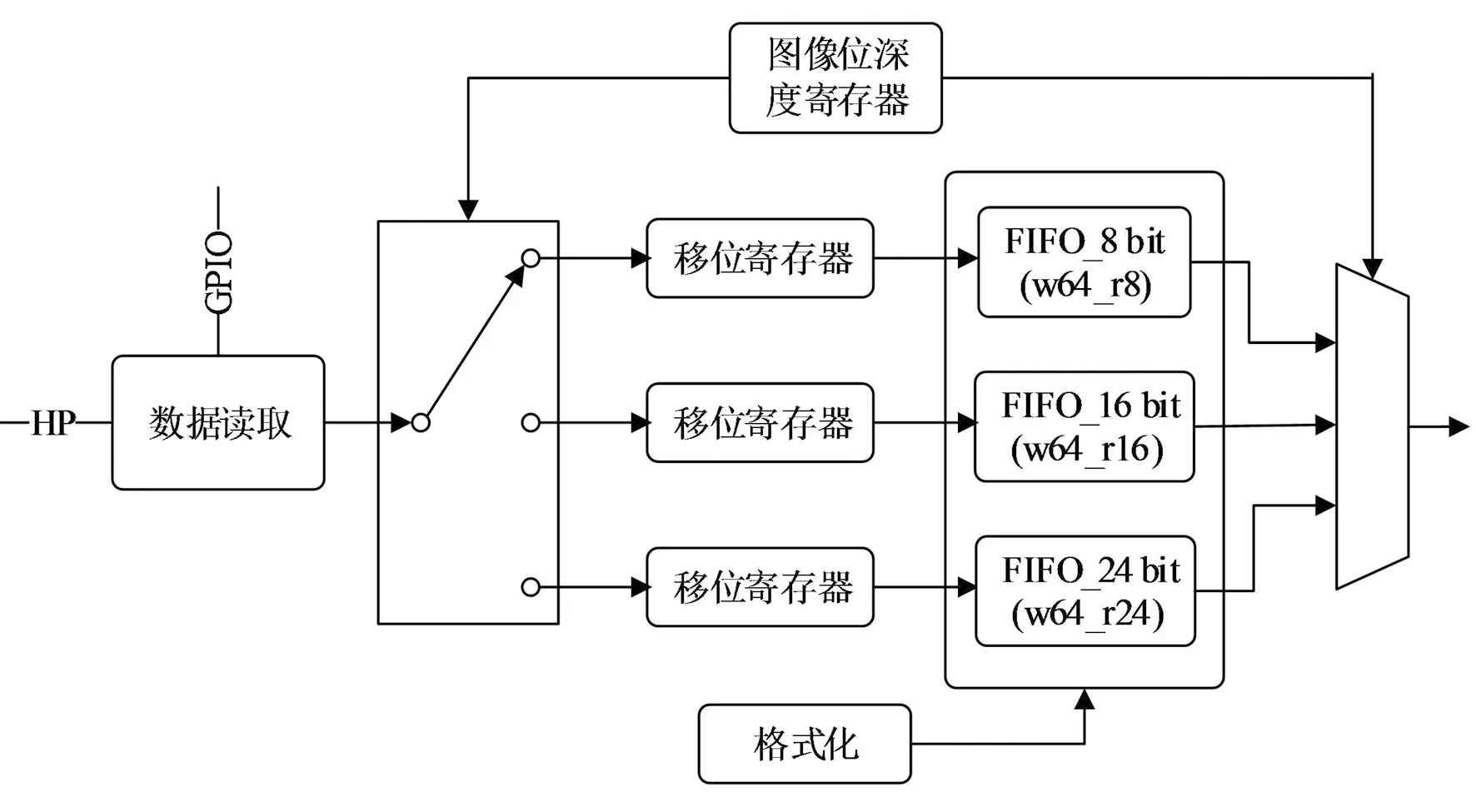

預處理模塊負責將內存中的數據讀出,并賦予一定特征,使其能夠符合后續模塊對輸入數據的要求。分別布置在待驗證算法IP核和HDMI顯示驅動模塊之前。預處理模塊分為兩部分:數據讀取和格式化。如圖6所示,PS通過GPIO向該模塊發送啟動脈沖后,內存中的數據通過HP口讀出到預處理模塊中。為保證一次突發傳遞的像素數量為整數,應將兼容圖像位深度的公倍數設為突發數據位寬。讀出的數據通過異步FIFO進行緩存和位寬轉換,由于不同位深度的圖像數據對位寬轉換的要求各有不同,基于邏輯資源換取兼容性的思想,使用多個FIFO對數據進行緩存和位寬轉換,再通過用戶配置的圖像位深度寄存器對電路進行選通。

圖6 預處理模塊Fig.6 Preprocessing module

在傳輸過程中,圖像數據僅保留亮度或顏色數據,行場同步信息丟失。由于算法模塊和顯示驅動模塊對時序的要求不同,所以兩個預處理模塊在格式化上的需求有所不同。

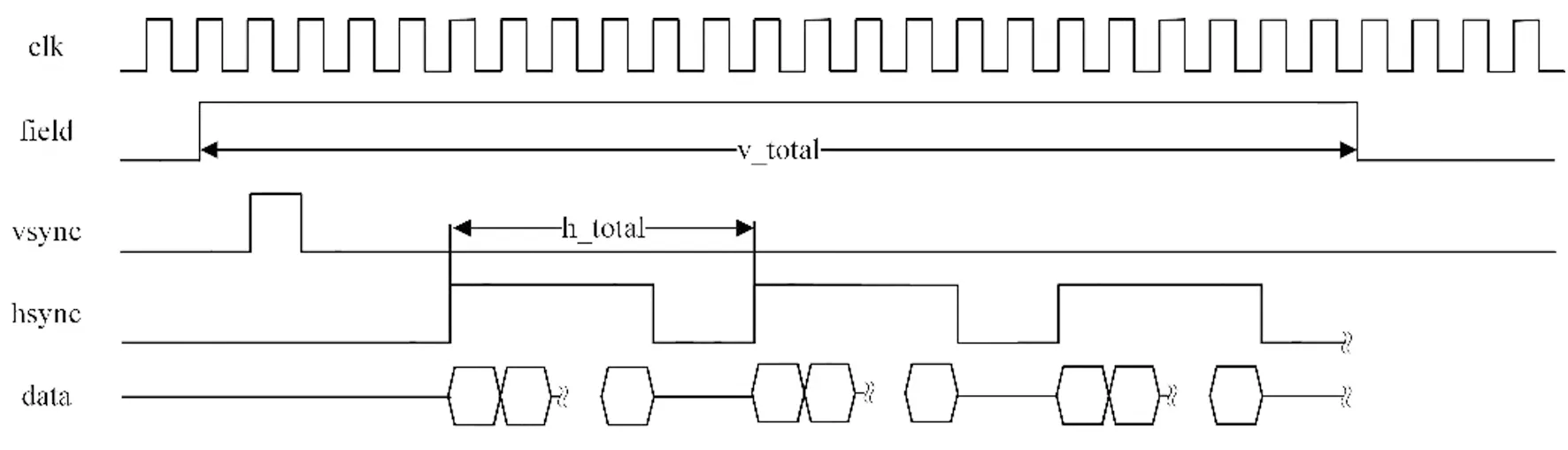

(a)算法模塊對圖像數據的時序參數沒有嚴格要求,只需按照一定的規律對連續數據進行分割。時序參數如圖7所示,以實際的圖像大小為基礎,將連續數據分割為圖像數據。

圖7 格式化的時序參數Fig.7 Timing parameters of formatting

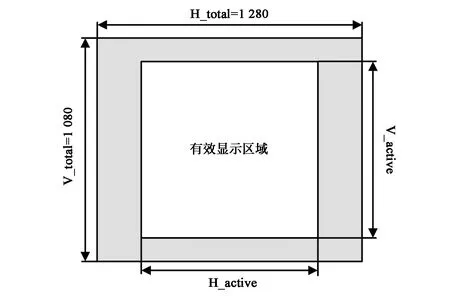

(b)由于顯示驅動模塊對圖像的時序參數要求嚴格,而不同分辨率具有不同的同步信號參數,為顯示分辨率各異的圖像,將顯示區域劃分為有效顯示區和無效顯示區。如圖8所示,有效區域位于顯示區域的中央,無效區域像素點的值置為0,為顯示區域中除有效區域的部分。在本實驗中,采用1 280×1 080向下兼容的顯示方案。

圖8 顯示區域劃分Fig.8 Display area division

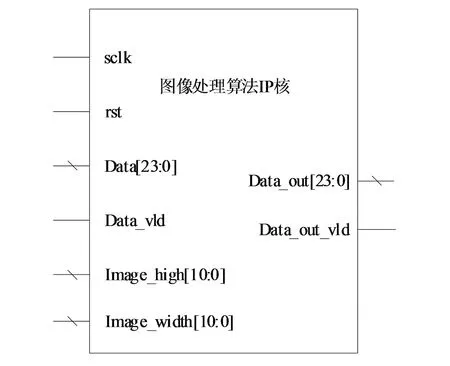

為保證對8,16,24 bit位深度圖像的兼容處理,規定部分重配置模塊接口一致,對算法IP核接口的設定如圖9所示。數據總線設定為24 bit,圖像高度和寬度設定為11 bit。在部分重配置中手工布局是不可或缺的[16],布局約束(Pblock)的設置直接影響著部分重配置模塊能否成功地部署在重配置分區中。在驗證框架中,由于不同算法IP核所需的邏輯資源有所區別,所以Pblock需要使用者根據需要進行約束。

圖9 部分重配置模塊Fig.9 Partial reconfiguration

4 案例分析

基于Xilinx Zynq-7000系列SoC,在Vivado18.2開發套件下,對本文提出的驗證框架進行實驗驗證。為證明所述驗證框架的有效性和兼容性,測試驗證周期和待驗證IP核的部署速度,本文以3種圖像處理算法IP核為例,采用多類型、多分辨率的視頻流作為測試激勵,由上位機通過以太網發送給測試框架。

4.1 案例算法簡述

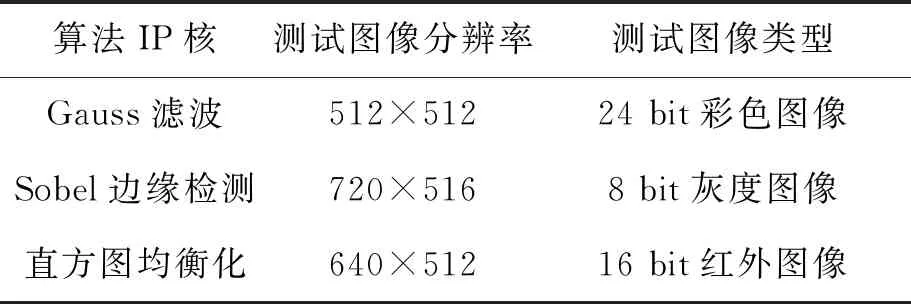

待驗證的算法IP核及相應的測試視頻如表2所示。

表2 測試圖像分辨率及類型Tab.2 Type and resolution of test image

RGB圖像的GAUSS濾波:高斯濾波是一種線性平滑濾波,作為低通濾波器使用時,可以將低頻能量濾去,起到圖像平滑作用[17]。本案例中對彩色圖像的RGB通道分別進行高斯平滑操作。

灰度圖像的Sobel邊緣檢測:Sobel是最常用的邊緣檢測算子,通過計算圖像灰度函數的一階梯度近似值實現圖像邊緣的增強[18]。

基于直方圖均衡化的紅外圖像可視化:由于紅外信號的動態范圍較寬,需要高比特的模數轉換器去采集。但是大部分模擬和數字視頻接口都要求輸入數據為8 bit,所以高動態范圍的紅外圖像需要經過壓縮才能夠正常顯示。直方圖均衡化(HE)將紅外圖像的直方圖均勻映射至256級,提升了顯示圖像的對比度。

4.2 驗證框架驗證效率

驗證框架的實時驗證效率由圖像處理算法IP核的帶寬、存儲器與FPGA之間的讀寫速率和上位機與驗證框架的通信速率決定。驗證框架中各模塊的傳輸帶寬(Bandwidth,BW)如式(1)所示,其中C為模塊的工作時鐘頻率,W為傳輸的數據位寬。相較于16 bit和24 bit圖像,8 bit圖像的算法IP核具有最低的帶寬,該框架中工作時鐘為100 MHz,則最低傳輸速率為800 Mbit/s。存儲器與FPGA之間使用HP口實現數據交互,讀寫的工作時鐘為250 MHz,數據位寬為48 bit,通信帶寬為12 Gbit/s。

KBW=C×W,

(1)

上位機中的MATLAB軟件與驗證框架建立千兆以太網通信,其平均傳輸速度為502 Mbit/s。

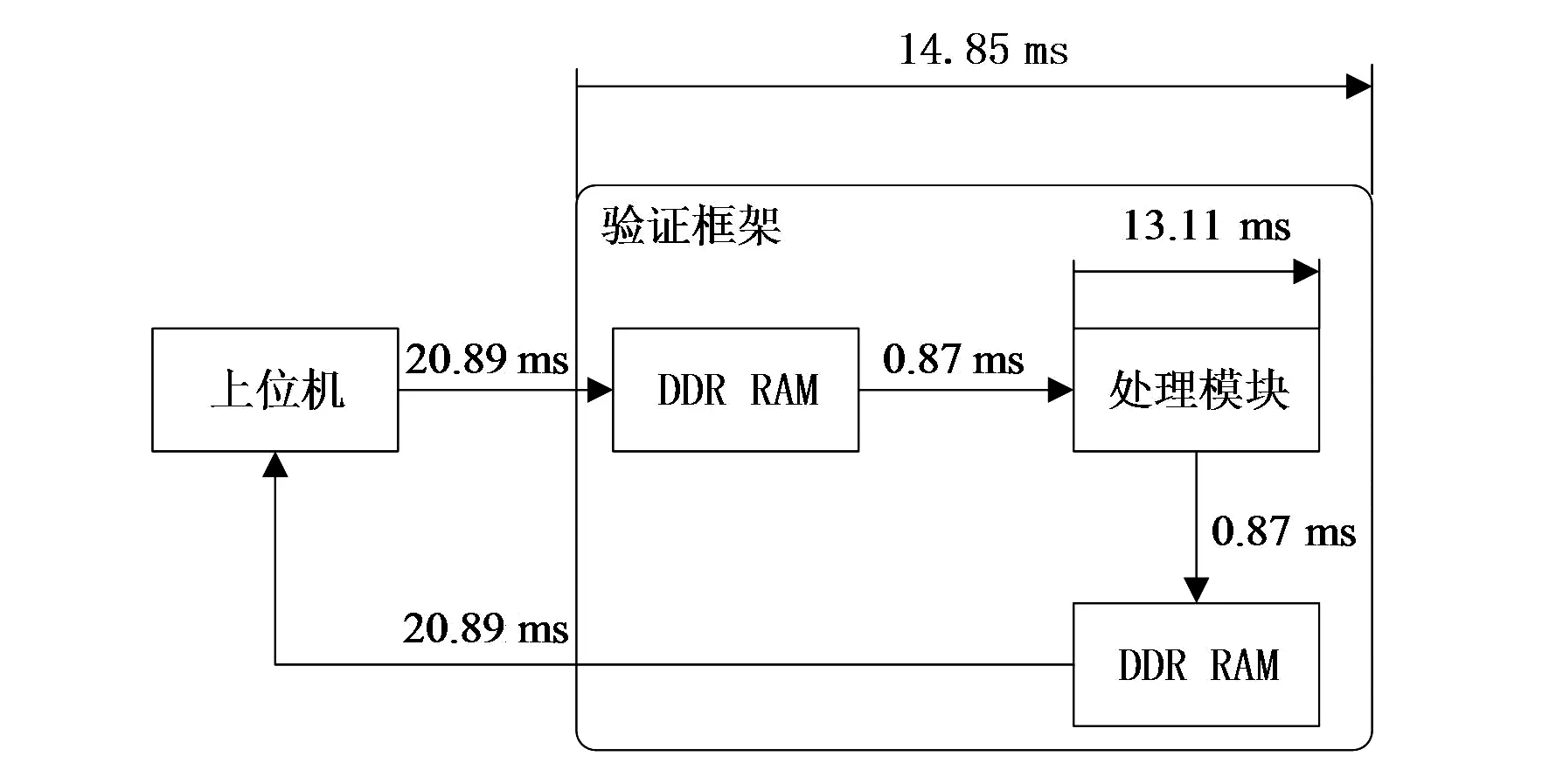

以分辨率為720 P(寬1 280 bit,高720 bit)位寬為8 bit的測試圖像為例,分析數據環路的處理時效性。圖10為測試圖像處理過程的時間消耗,由式(1)得驗證框架的處理延遲為14.85 ms,上位機與驗證框架的通信延遲為20.89 ms,綜合上述分析,驗證效率的瓶頸在于上位機與驗證框架的以太網通信速率。

圖10 證框架處理時效Fig.10 Processing time of verification framework

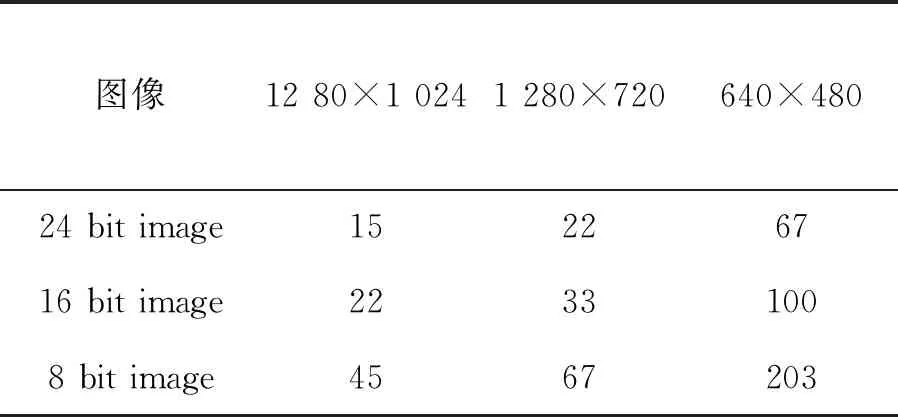

根據以太網的通信速率計算出不同位深度和分辨率圖像下的驗證效率如表3所示,能夠達到圖像處理算法IP核在實際應用場景中的使用幀率。

表3 不同測試圖像的驗證速率Tab.3 Image verification rate of different test images (FPS)

4.3 部分重配置應用與分析

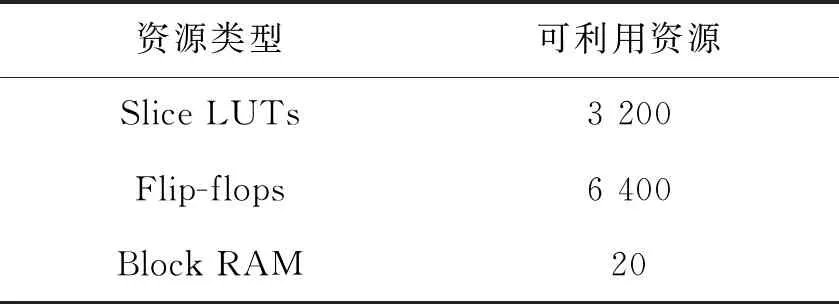

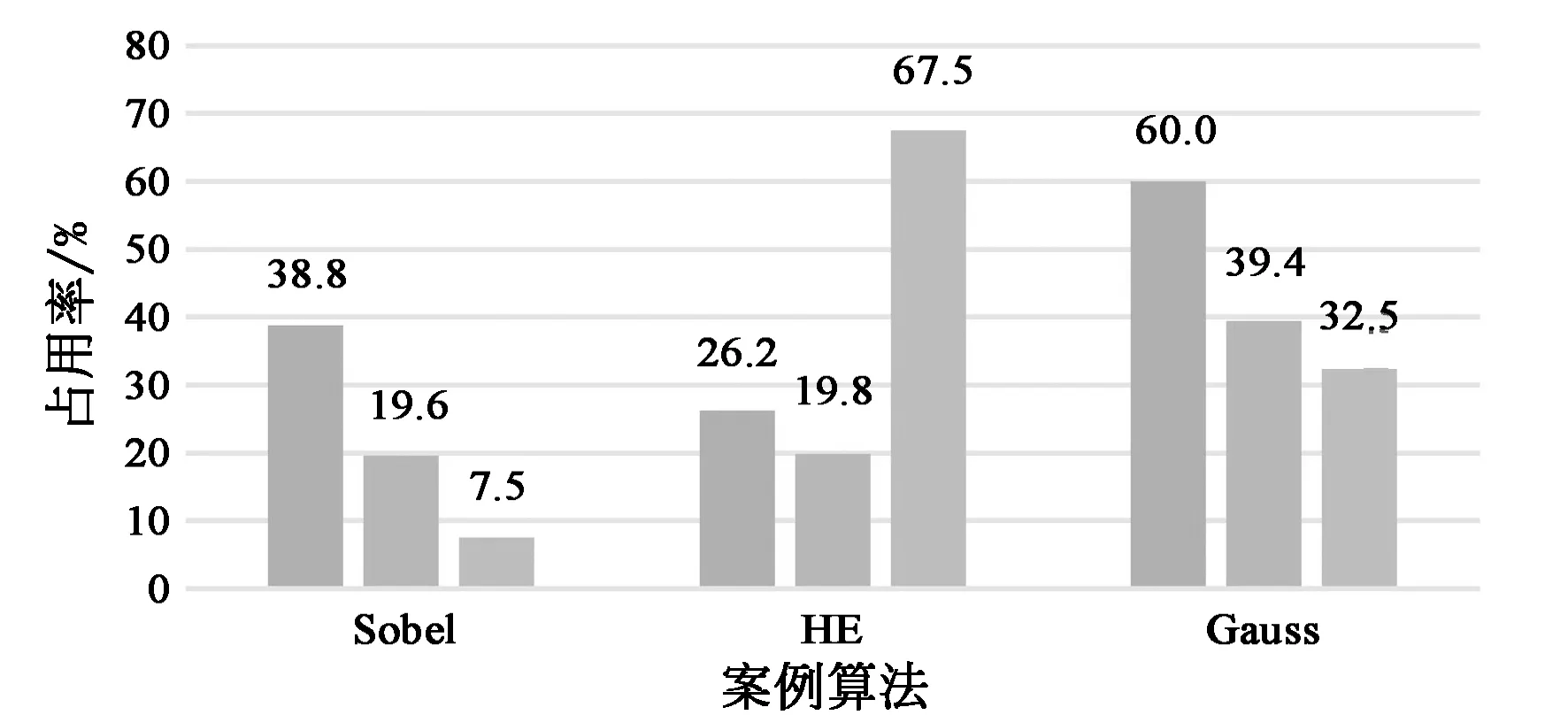

為避免重復劃分可重構區域,Pblock中的資源應滿足3種算法的邏輯需求[19]。根據待驗證算法IP核綜合后的邏輯資源需求,在FPGA中對重配置區域進行劃分,本案例中Pblock中的物理資源如表4所示。待驗證IP核在Pblock中的邏輯占比見圖11(a),Pblock的劃分以Gauss濾波中所需的Block Ram資源以及HE所需的Slice LUTs和Flip-flops資源為標準,并且為了方便靜態區域和重配置區域之間的布線,Pblock預留了一定的邏輯資源。

表4 Pblock中的邏輯資源Tab.4 Logical resource in Pblock

部分重配置模塊占用的邏輯資源在整體構型中的百分比如圖11(b)所示,其中,靜態邏輯使用了整體構型90%左右的LUTs、Register和絕大多數的Block RAM。

(a)IP核在Pblock中的資源占比(a)Resource ratio of IP core in Pblock

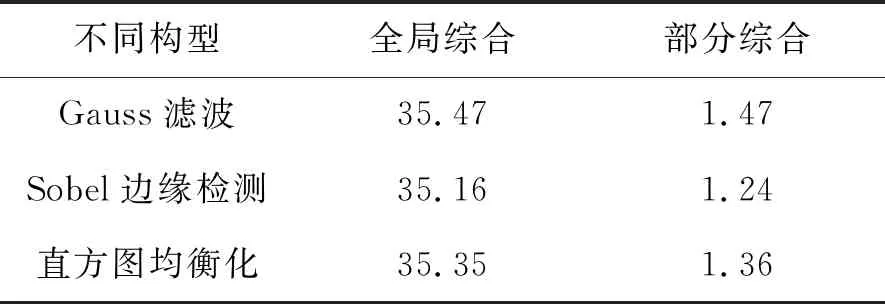

由于靜態邏輯占據了整體構型邏輯量的90%左右,所以避免靜態區域的重配置一方面降低算法IP核在驗證框架上的部署周期,另一方面保證了靜態邏輯的功能穩定性。該實驗中,綜合工程使用的CPU類型為4核I5-4210H,對不同算法IP核構型采用全局綜合消耗的時間與部分綜合所消耗的時間如表5所示,綜合速度提升了25倍左右。

表5 不同構型的綜合時間Tab.5 Synthesis time of different configurations min

4.4 測試結果與討論

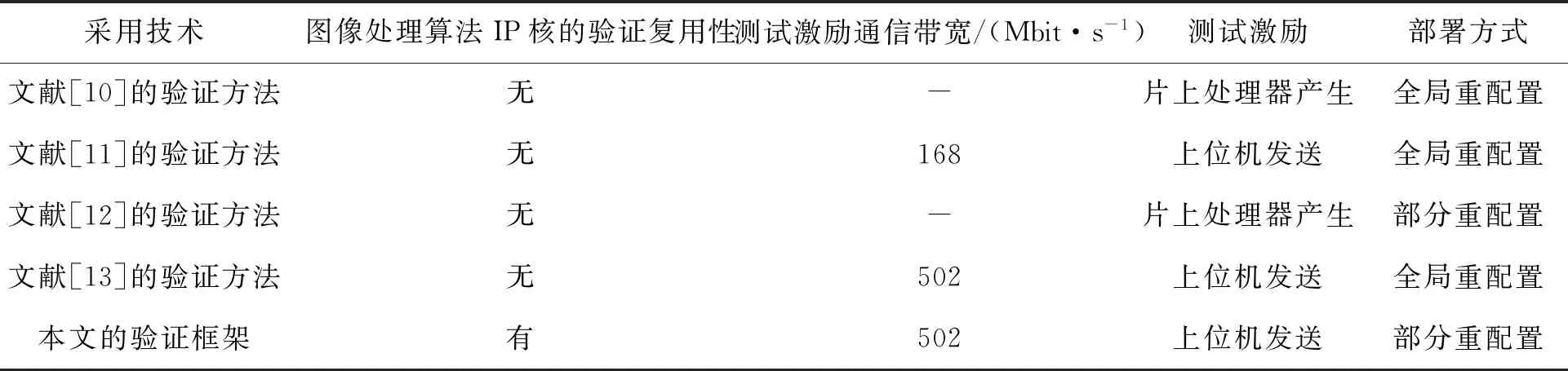

在本實驗中,將3種不同的算法IP核部署在驗證平臺中,上位機針對待驗證算法IP核發送位深度和分辨率各異的測試視頻,證明了本文所設計的框架具有兼容3種位深度圖像的數據通路,進而對框架的可重用性進行了驗證。測試激勵通過上位機發送,更符合圖像處理算法IP核的實際使用要求。對實時驗證效率和算法IP核的部署時長進行了分析,驗證框架的驗證效率達到圖像處理算法IP核的使用幀率,部分重配置技術在提高框架穩定性的同時,縮短了算法IP核的部署時長,著重降低了不同構型綜合的時間周期。表6為本文提出的方法與相關工作的對比。本文所設計的框架針對性地為圖像處理算法IP核構建了可動態配置的數據通路,具有驗證可重用性。文獻[12]針對通用數據接口(AXI,FIFO)設計的驗證覆蓋庫無法兼容類型各異的圖像數據,文獻[10]需要設計人員針對待驗證的硬件設計開發協議橋,文獻[11]與[13]只針對特定任務在FPGA中為待測設計構建了測試架構。上述方法面向圖像處理算法IP核不具有可重用性。文獻[10]和文獻[12]使用硬核處理器產生測試激勵的方法雖具有較高的傳輸帶寬,但針對不同算法IP核構建測試視頻流會增加處理器系統的軟件開發難度,降低圖像處理算法IP核的驗證效率。本文與文獻[11]、[13]采用上位機軟件發生測試激勵,具有較好的操作性和靈活性,其中文獻[11]受限于軟核的處理速度,通信速率較低。本文與文獻[12]采用部分重配置的方法提高了框架的穩定性,避免了因時序問題引起的驗證錯誤,加速了待驗證算法IP核的部署速度。

表6 本文提出的方法與其他文獻的結果對比Tab.6 Performance comparison of different methods

5 結 論

針對圖像處理算法IP核驗證效率和復用性難以統一的問題,本研究基于FPGA原型驗證技術,使用ARM+FPGA異構平臺,聯合上位機軟件以實時性與可重用性為目標構建了圖像處理算法IP核驗證框架。驗證框架對于以8,16,24 bit位深度圖像為處理對象和結果的算法IP核具有可重用性;上位機通過千兆以太網發送測試視頻,更符合算法IP核的實際應用場景;部分重配置使待驗證IP核的部署速度相對全局重配置提高了25倍。本文提出的方法為圖像處理算法IP核的驗證提供了一種統一架構。