HDB3編譯碼設(shè)計的FPGA實現(xiàn)

劉雪峰,張 希

(1. 西安交通工程學院,陜西 西安 710300;2.西安黃河光伏科技股份有限公司,陜西 西安 710048)

0 引言

在進行長距離數(shù)據(jù)通信之前,通常要對數(shù)據(jù)進行編譯碼處理,HDB3碼因具有無直流成份、低頻成份和連0個數(shù)最多不超過三個等優(yōu)點而被廣泛采用。其所具有的時鐘恢復和抗干擾性能更適合于長距離信道傳輸。鑒于此,本文設(shè)計了基于FPGA的 HDB3編譯碼系統(tǒng)。

本設(shè)計利用Verilog HDL編寫軟件代碼,采用模塊化的設(shè)計方案,在QuartusⅡ開發(fā)軟件上,完成了硬件的布局與軟件的仿真,并用ALTERA CycloneⅣ系列的芯片進行了軟硬件功能驗證,與理論輸出值保持一致。FPGA具有高集成度、響應速度高、編程可重復的特點,故本設(shè)計具有軟件靈活可靠、硬件調(diào)試方便、較低開發(fā)成本、系統(tǒng)穩(wěn)定可靠等優(yōu)點。

1 HDB3編譯碼的設(shè)計

1.1 HDB3編譯碼的原理

HDB3碼是為了克服AMI碼的長連零現(xiàn)象而出現(xiàn)的,將4個連續(xù)的“0”位元取代成“000V”或 “B00V” 。其編碼規(guī)則如下:一是將消息代碼轉(zhuǎn)換為AMI碼;二是檢查AMI碼中連“0”的情況,出現(xiàn)4個或4個以上連“0”時,將第4個“0”變?yōu)榕c前一個非“0”符號同極性的符號,用“V”標識(+V和-V);三是檢查相鄰V符號之間非“0”符號是否為偶數(shù),如果為偶數(shù),則將當前V符號前一個非“0”符號后的第一個“0”變?yōu)椤癇”,“B”的極性與前一個非“0”符號相反,并使“V”后的非“0”符號從“V”開始再交替變化。根據(jù)編碼規(guī)則,V碼脈沖與前一個脈沖具有相同的極性。可從接受的信碼中找出V碼流,根據(jù)通信傳輸中加取代節(jié)原則,V碼與前三位碼是取代碼,需復原為四連0。只要找到V碼,不管V碼流前是兩個“0”碼,將取代節(jié)清零,完成了扣V扣B功能,進而得到原信碼序列。

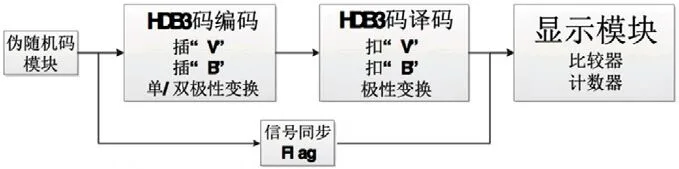

1.2 系統(tǒng)整體框圖

系統(tǒng)設(shè)計的整體方案如圖1所示,本設(shè)計包括用于產(chǎn)生基于M序列的偽隨機產(chǎn)生模塊,產(chǎn)生的偽隨機碼流分為兩條支路:一條支路通過HDB3編譯后輸送給比較器,另一支路通過幀同步模塊輸入比較器。同步模塊對偽隨機碼產(chǎn)生模塊起始幀頭信號進行標記,以使兩路信號實現(xiàn)同步;比較器比較兩條支路的信號幀,以判斷傳輸過程中是否存在誤碼,將產(chǎn)生的誤碼進行標記;計數(shù)器統(tǒng)計比較器產(chǎn)生的誤碼個數(shù);顯示器顯示計數(shù)器計數(shù)的結(jié)果。

圖1 系統(tǒng)整體框圖

設(shè)計亮點在于比較器之前設(shè)置同步Flag模塊,同步模塊可將偽隨機碼與通過HDB3編譯碼后的兩支路信號保持同步,比較器可以直接對兩支路信號進行比較,提高了判斷誤碼的準確率。

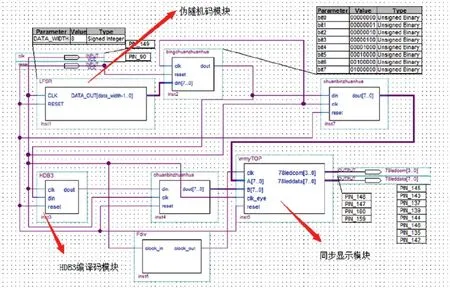

1.3 HDB3編譯碼整體設(shè)計

圖2所示為HDB3編譯碼頂層設(shè)計,偽隨機碼模塊產(chǎn)生8位的偽隨機信號,通過并串轉(zhuǎn)換模塊合成為一路信號送入HDB3編譯碼模塊,將編譯數(shù)據(jù)通過串并轉(zhuǎn)換模塊恢復為8位信號與偽隨機碼模塊進行兩次轉(zhuǎn)換后的8位信號進行比較,計數(shù),顯示編譯碼過程中的誤碼。

圖2 HDB3編譯碼頂層設(shè)計框圖

信號幀頭設(shè)置flag同步模塊,在進入比較計數(shù)模塊之前,有效的防止了信號的抖動以及在傳輸過程中的誤碼問題。具體步驟如下:

在QuartusⅡ12.0開發(fā)軟件上編程,并利用芯片EP4CE115F29C7N加上外接電路制作實物,進行偽隨機碼的HDB3編譯碼模塊顯示,與理論輸出值一致。

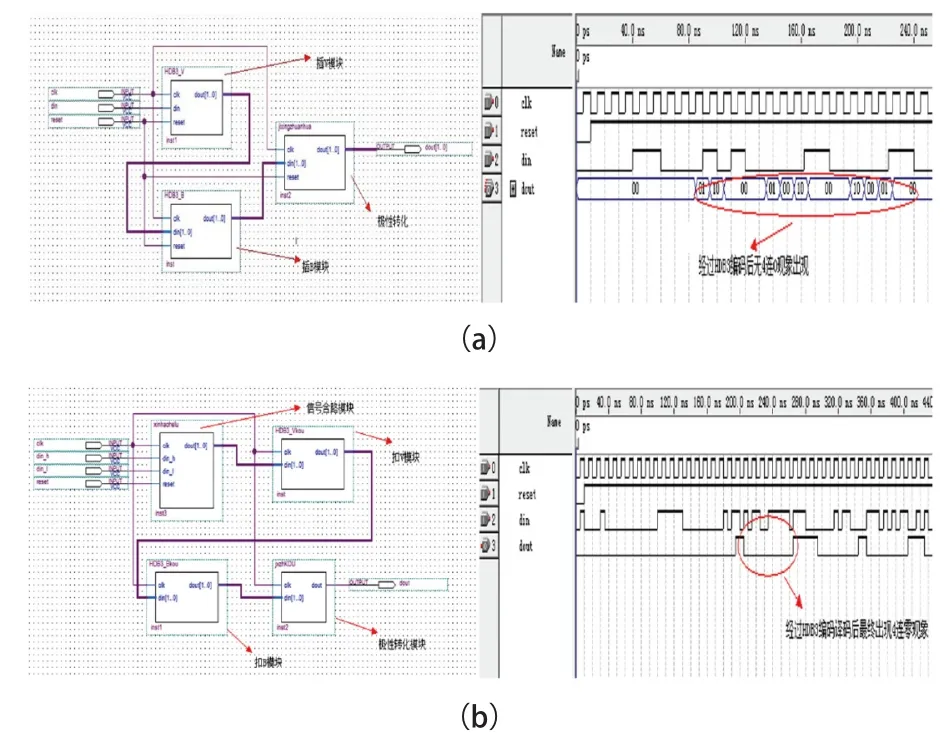

圖3(a)所示為HDB3編碼頂層設(shè)計及仿真波形,信號經(jīng)過HDB3編碼部分,在編碼部分進行插V、插B操作,以及極性轉(zhuǎn)換;圖3(b)所示為HDB3譯碼頂層設(shè)計及仿真波形,信號經(jīng)過HDB3譯碼部分,在譯碼部分進行扣V、扣B操作,以及極性轉(zhuǎn)換。由波形圖可以看出,偽隨機信號經(jīng)過HDB3編譯碼后出現(xiàn)了四連零現(xiàn)象。

圖3 HDB3編碼頂層設(shè)計及仿真波形

2 實驗分析

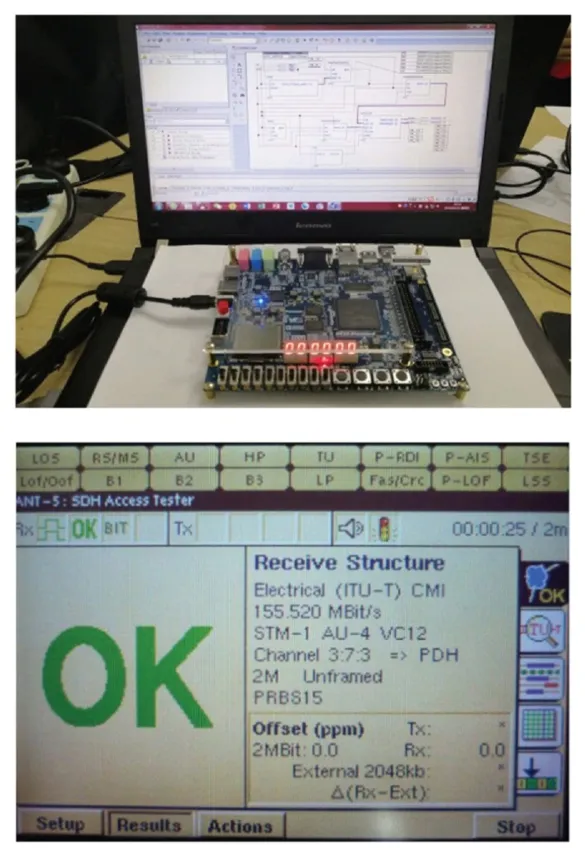

本文設(shè)計的軟件部分下載進開發(fā)板的整個實驗系統(tǒng)如圖4所示,由圖可以看出將編譯碼后的信號下載進信號分析儀顯示OK,說明編譯碼過程符合通信要求。整個測試過程為期一星期,通信過程產(chǎn)生了0個誤碼,由實驗現(xiàn)象可知本文設(shè)計的編譯碼電路基本符合信號傳輸?shù)囊蟆?/p>

圖4 實驗結(jié)論圖

3 結(jié)束語

本文所設(shè)計的HDB3編譯碼模塊簡單實用,利用FPGA實現(xiàn) HDB3 編譯碼功能具有很強的靈活性,可以把編碼電路和譯碼電路與其他電路相集成在一起,提高系統(tǒng)設(shè)計的速度。本 文以ALTERA公司的CycloneⅣ系列的FPGA芯片EP4CE115F29C7N為硬件平臺,以Quartus II為軟件平臺,以Verilog HDL為開發(fā)工具,來驗證FPGA實現(xiàn)的HDB3編譯碼器。并對整個HDB3碼的編碼過程以及解碼過程作了一個詳細的分析。且實驗結(jié)果符合預期,有很好的應用遠景。