一種基于VPX架構和PSOC芯片的高速板卡設計

陳坤

(廣州海格通信集團股份有限公司,廣州510663)

0 引言

隨著技術的發展和功能應用的不斷增加,系統設備已逐漸往小型化、模塊化發展,與之而來的就是數據量的快速增加,在技術層面就要求系統設備具有更高的集成度、更大的總線帶寬和更強的運算處理能力。Zynq7000系列PSOC芯片內部集成ARM雙核處理系統和高性能FPGA,專為需求高處理性能的嵌入式系統而構建,目前已較多使用在工業自動化、輔助駕駛、航空航天等行業。VPX系統架構因具有模塊化、通用化、高可靠性和高帶寬等特點,特別適合在工業、航空航天等特殊環境中適用。本文將二者結合,提出了一種基于VPX架構和PSOC芯片的高速板卡設計方案,可滿足多種功能VPX板卡的基本開發需求。

1 板卡總體設計

作為新一代的工業總線標準,VPX在具有機械結構和導冷抗震優勢的基礎上,引入了Rapid IO、PCIE、高速以太網等高速總線,解決了帶寬和高速互聯問題,使得系統內部組件間的通信速率大大增加。

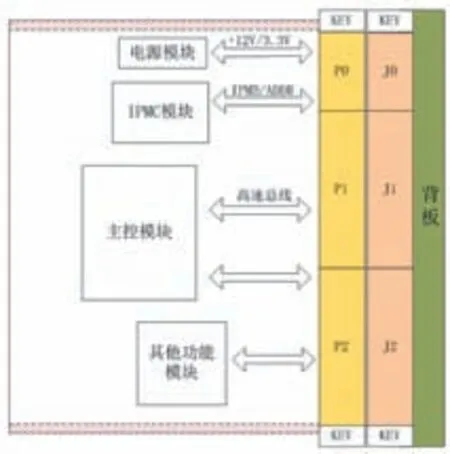

按照VPX標準將板卡控制功能和管理板卡功能分離,本文設計的高速板卡可分為主控模塊、智能平臺管理模塊(IPMC)、電源模塊以及用戶功能模塊,系統框圖如圖1所示。圖1以3U板卡為例,其中,主控模塊可與用戶其他功能模塊配合,根據需求完成協議處理、算法實現以及相關的時序和邏輯控制功能,IPMC模塊主要實現對板卡的管理功能,可用于整板電壓、電流、溫度等健康信息的監控,以及板卡的上下電控制。

圖1 板卡功能系統框圖

2 主控模塊設計

2.1 主控芯片選型

作為可擴展處理平臺,Zynq7000系列PSOC芯片實現了在單一芯片上集成ARM雙核處理器與FPGA,不僅具有ASIC等級的效能與功耗,更具備FPGA的靈活性和處理器的可編程等特點,并且相對于“嵌入式處理器+FPGA”的通常方案,Zynq7000在處理器和FPGA之間還采用了高帶寬、低延時的AXI4連接總線,讓二者效能得到充分的發揮,而不會有額外的接口開銷,非常適合小型化、高集成度和高性能的使用場景。

在Zynq7000的芯片系列中,7Z020以下芯片主要針對消費類或輔助駕駛等低端應用,7Z030以上針對工業、通訊、國防、廣播級等復雜應用等。本文選擇中高端芯片XC7Z035作為主控核心,該芯片可分為PS(Processor System)和PL(Programmable Logic)兩部分,其中PS側包含主頻高達1G的雙核ARM Cortex-A9 MPCore處理器、片上兩級緩存器、外部存儲器接口以及各種片內外設,PL側是基于Xilinx Kintex-7 FPGA的可編程邏輯,包含275K個邏輯單元、17萬個查找表LUT、900個DSP Slices,8對高速串行GTX接口,2個12Bit、1MSPS的ADC以及眾多的可配置輸入輸出I/O,廣泛支持LVDS、LVCMOS等電平標準。

2.2 主控芯片啟動模式設計

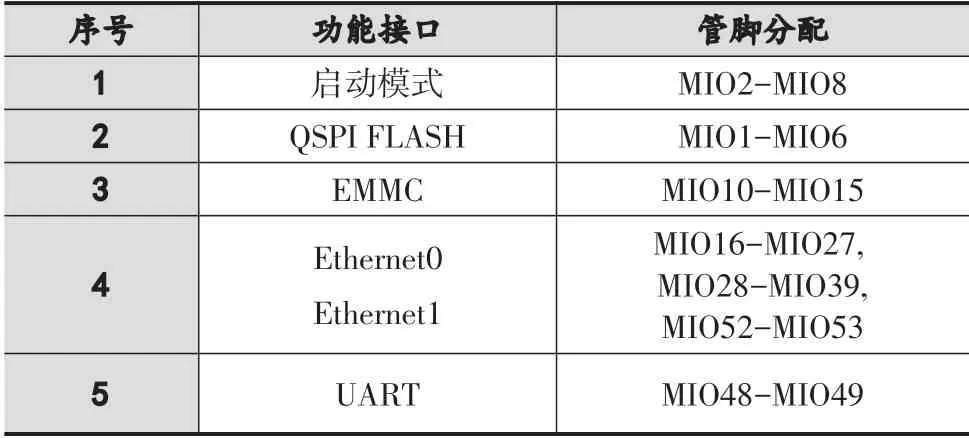

對7Z035進行設計,首先要通過芯片規格書中的管腳復用表或者借助Vivado開發軟件完成PS側MIO管腳的復用配置,根據通常的功能和接口需求,設計的管腳復用分配表如表1所示。

表1 MIO管腳復用分配表

其中,啟動模式通過配置MIO2-MIO8管腳的上下拉狀態來選定,本文采用常用的QSPI Flash啟動,并預留SD卡啟動模式,便于程序調試使用,根據規格書中的啟動模式配置表,QSPI啟動MIO[5:3]=100。MIO7和MIO8是MIO bank電壓配置位,bank500連接QSPI Flash和EMMC芯片,bank501連接以太網PHY芯片并引出UART串口,上述芯片都支持LVCOMS 3.3V電平,所以bank500和bank501都配置為3.3V電壓。配置管腳如圖2所示。

圖2 啟動模式管腳配置圖

2.3 外圍芯片選型

(1)QSPI Flash和EMMC

QSPI Flash主要存儲FSBL文件、裸機程序或者Uboot文件,本文選擇SPANSION的QSPI Flash S25FL256S,32MB容量、工作電壓2.7-3.6V,支持x1、x2和x4工作模式。EMMC芯片主要作為QSPI Flash的補充,存儲較大的文件,比如文件系統和用戶數據文件,具有體積小、容量大、讀寫速度快和使用方便等優點。本文選擇三星的8GB EMMC芯片KLM861WEPD-B031,工作電壓為2.7-3.6V,支持工業級-40℃低溫使用場景。

(2)DDR3

DDR3芯片選用了兩片鎂光的MT41K256M16RE-125,單片16位512MB容量,2片組合數據位寬32位,容量1GB,最高運行速度可達533MHz。兩片DDR3芯片在PCB設計上采用fly-by拓撲模式,并在地址線和控制線上加了VTT端接阻抗匹配,來確保信號完整性。

(3)以太網芯片

Zynq7000系列芯片包含2個10/100/1000M以太網MAC控制器,支持GMII、SGMII和RGMII等多種PHY芯片接口。根據VPX系統多有內外網的需求,本文選用了兩片MARVELL的PHY芯片88E1512設計了兩條以太網鏈路。88E1512芯片支持1.8V、2.5V和3.3V的LVCMOS I/O電平標準,支持單一3.3V電源供電,并支持RGMII接口到電口、光口以及SGMII接口的直接轉換,能較好滿足VPX系統對不同以太網協議標準的需求。88E1512芯片的工作模式、PHY芯片地址以及RGMII接口電平可通過上電配置管腳進行設置。兩片88E1512芯片的RGMII接口電平都設置為3.3V,與7Z035的Bank501電壓3.3V匹配,芯片地址可分別設置為00001b和00011b,7Z035通過SMI接口分別進行尋址訪問。

3 電源模塊設計

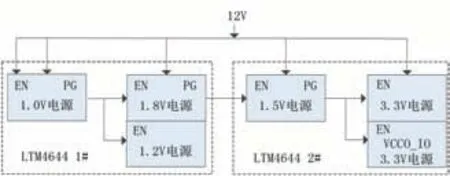

依據7Z035芯片的電源需求,VPX板卡一般會有1.0V、1.2V、1.8V、1.5V、2.5V、3.3V和5V等常見的電源。為減少電源部分所占的PCB空間,提高板卡集成度,再結合7Z035芯片各路最大電流值,本文選取兩片凌力而特的LTM4644作為板卡的電源主芯片。LTM4644是塑封一體集成式微型非隔離降壓型DCDC轉換器,基于同步整流Buck拓撲設計,最大四路4A或單路16A電流,可并聯配置多種輸出陣列,有較高的電源轉換效率,并且體積僅有10×16×6.5mm3,集成度高,外圍僅需一個調壓電阻、幾個輸入輸出瓷片電容,即可快速完成多路電源系統的設計。鑒于7Z035芯片1.0V核電壓在部分復雜算法應用中,瞬態電流較大,本文采取并聯2路LTM4644輸出的方式,給1.0V提供8A的電源供應。圖3為核電壓1.0V的電源設計。

圖3 1.0V電源設計

按照7Z035芯片的電源上電時序要求,上電次序為1.0V->1.8V、1.2V->1.5V->3.3V、VCCIO,本文利用LTM4644芯片的外部使能管腳和PGOOD管腳,設計了電源上電時序,如圖4所示,經實測各路電源上電時序滿足芯片要求。

圖4 上電時序設計

4 IPMC模塊設計

IPMC模塊作為板卡的智能平臺管理控制器,主要配合VPX機箱管理控制器實現對各板卡的統一管理,包括板卡健康信息監控、板卡信息讀取、供電和復位控制等。本文選取NXP的STM32F103RET6作為IPMC模塊的控制核心,通過I2C1和I2C2接口分別對應為VITA46.11協議中的IPMB-A和IPMB-B總線,實現與機箱管理控制器的信息交互,通過電流/功率監視芯片INA226和溫度監控芯片MAX31723分別完成對12V電壓電流和板卡溫度的監控,原理框圖如圖5所示。

圖5 IPMC模塊設計

5 結語

本文提出了一種基于VPX架構和PSOC芯片的高速板卡設計方案,包括主控芯片設計、電源模塊設計和IPMC模塊設計,具有高集成度、高性能和高帶寬等特點,目前已被多個課題所采用,驗證了該方案的可行性,可為板卡類項目設計提供借鑒參考。