基于0.18 μm CMOS加固工藝的抗輻射單元庫開發

姚 進,左玲玲,周曉彬,劉 諄,周昕杰

(中科芯集成電路有限公司,江蘇無錫214072)

1 引言

空間科技在增強國家實力和維護國家安全方面發揮著巨大的作用,目前國內對各種軌道衛星的需求十分迫切,因此對衛星控制系統的性能、可靠性、成本和研發進度等方面提出更高的要求。快速制造出滿足各類衛星需要,在電性能、可靠性及抗輻射性能三方面均符合要求的國產抗輻射加固元器件成為關鍵,而基于抗輻射標準單元庫的半定制設計方法能夠大大簡化設計,縮短設計周期,提高工作效率,因此設計一套能夠得到廣泛應用的抗輻射單元庫是非常必要的。目前基于商用0.18 μm CMOS工藝,國內已有多個抗輻射單元庫的設計[1-2],但在抗輻射性能及單元基本性能間未取得良好平衡,且未對單元庫設計的全流程進行描述,本文基于0.18 μm加固工藝,采用工藝加固與設計加固結合的方式,完成了抗輻射單元庫的全流程設計,成功開發了一套能廣泛應用于工程的抗輻射單元庫。

2 輻射加固方案

2.1 總劑量加固方案

總劑量加固方法包括設計加固和工藝加固,設計加固優勢會降低對工藝的依賴性,缺點是面積大,設計和版圖的靈活性不夠,有些電路甚至無法設計,如環柵結構無法設計小尺寸MOS器件,造成電路設計困難。工藝加固則是基于常規的條柵MOS器件結構,采用工藝開發方式提升NMOS器件抗總劑量輻射能力,可明顯減小版圖面積及降低設計難度,本文采用的是工藝加固方式。

深亞微米工藝中,隔離區寄生晶體管的漏電已經成為CMOS器件中總劑量效應的主要問題[3-4]。0.18 μm加固工藝主要對淺槽隔離(Shallow Trench Isolation,STI)場區進行總劑量加固,通過離子注入的方式將STI/襯底界面處的P型硅反型閾值提高,從而抑制隔離區寄生晶體管的漏電通道開啟。采用工藝加固后,1.8 V NMOS、3.3 V NMOS抗總劑量輻射能力分別從加固前的100 krad(Si)、50 krad(Si)達到了加固后的500 krad(Si)水平。STI場區注入的加固工藝會對器件的有效溝道長度產生影響,經實測NMOS管寬度W>0.5 μm后閾值電壓及飽和電流變化幅度均在10%以內[5],滿足電路實際設計需求,針對加固后NMOS管電參數的變化,重新抽取了器件Spice模型,以保證仿真精度。

2.2 單粒子效應加固方案

單粒子效應是指單個高能粒子穿過半導體器件的敏感區,在軌跡上沉積電荷,這些沉積電荷被器件所收集而引起的器件狀態改變。單粒子效應主要包括單粒子閂鎖效應(Single Event Latch-up,SEL)、單粒子翻轉效應(Single Event Upset,SEU)、單粒子瞬態效應(Single Event Transition,SET)等。SEL是指CMOS工藝中固有的寄生可控硅(Silicon Controlled Rectifier,SCR)結構受高能粒子轟擊而導通,導致電流不斷增大而使器件失效甚至燒壞;SEU是指存儲單元受高能粒子轟擊而導致器件邏輯狀態改變;SET是指組合邏輯受高能粒子轟擊而產生的毛刺信號,如被存儲單元采集,同樣會產生單粒子翻轉[6]。

SEL加固通常采用薄外延圓片材料或保護環版圖結構的加固方式,機理均是抑制可控硅效應,但保護環加固方法明顯增加版圖面積,而薄外延在抑制可控硅效應時同樣抑制了GGMOS寄生三極管的Snapback特性,對靜電放電(Electro Static Discharge,ESD)設計提出了更高的要求,本文通過TCAD仿真確認N管有源區與P管有源區的間距、P管和N管源端到各自體接觸的間距[7],保證400 K溫度下寄生可控硅結構無法導通,以較小的面積損耗實現了SEL加固;SEU加固采用經典的雙互鎖存儲單元(Double Interlocked Storage Cell,DICE)結構[8];針對SET加固,雖有各類延遲、C單元等濾除毛刺的加固方式[9],但對時序單元性能有明顯影響,且加固后仍很難保證電路滿足37 MeV·cm2/mg翻轉指標,為實現關鍵控制邏輯的37 MeV·cm2/mg翻轉指標,同時考慮到高可靠性電路設計需求,直接采用了內部自刷新的三模單元(Triple Module Redundant,TMR)進行全局三模冗余設計。

3 抗輻射單元庫開發

確認抗輻射加固方案后,抗輻射單元庫的設計流程與商用單元庫基本一致[10],具體開發流程如圖1所示,主要包括單元規格制定、單元邏輯及版圖設計、單元特征化及布局布線文件抽取、單元庫設計套件質量保證(Quality Assurance,QA)、硅驗證。

圖1 抗輻射單元庫開發流程

3.1 單元庫規格制定

單元庫規格制定主要按照設計需求確定標準單元的數目、單元的高度、P/N管尺寸的比例、驅動能力等。由于SEL加固中增加了N管與P管有源區的間距,同時考慮到加固時序單元的布線空間,單元庫高度采用了高性能單元庫常用的12 Track。P/N管尺寸比例,常規單元庫以速度為主要考慮因素,時鐘單元以延遲及轉換時間的平衡為主要考慮因素。單元種類以盡量滿足各類數字電路設計需求為主,內核普通單元提供X1/X2/X4 3種驅動能力,反向器及緩沖器類器件提供X1/X2/X4/X8/X12/X16/X24 7種驅動以提升綜合效率;I/O單元包括輸入、輸出、雙向、電源、晶振、模擬等種類,輸出包含2 mA/4 mA/8 mA/12 mA/16 mA/24 mA 6種驅動能力,具體單元種類及數量如表1所示,針對單粒子效應的加固單元加粗顯示。

表1 抗輻射單元庫種類及數量

3.2 單元邏輯及版圖設計

抗輻射單元邏輯及版圖的設計驗證流程與商用單元庫區別在于邏輯設計上時序單元為DICE及TMR結構,結構分布如圖2(a)(b)所示,通過TCAD仿真確認在LET閾值為37 MeV·cm2/mg時的敏感節點間距,以保證時序單元的抗輻射性能,加固前后時序單元(1倍驅動上升沿雙輸出觸發器,dfnrb1)常規參數仿真對比如表2所示,增加了內核及端口的加固時鐘單元用于全局信號加固,組合邏輯加固以增加驅動能力、提升翻轉臨界電荷為主。

表2 時序單元加固前后基本參數仿真對比(TT/1.8 V/25℃)

圖2 加固時序單元結構示意圖

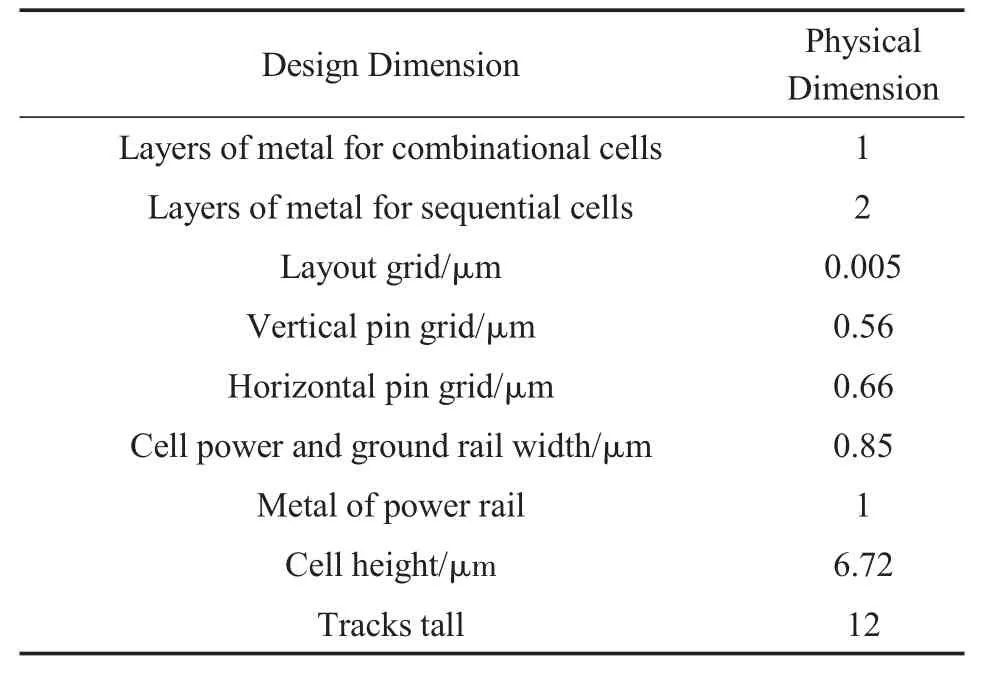

版圖設計上主要增加了抗單粒子效應的規則檢查,內核單元版圖相關信息如表3所示。

表3 抗輻射內核單元版圖基本信息

3.3 單元特征化及布局布線文件抽取

單元特征化是連接工藝與數字電路設計的橋梁,交付文件通過Synopsys Siliconsmart生成。單元特征化流程如圖3所示,其原理就是以Spice仿真為內核,基于后仿網表,選取一定范圍內的激勵和負載進行仿真,提取時序和功耗信息。時序信息包括延遲類信息(Rise/Fall Delay,Rise/Fall Transition)和建立保持類時間(Setup/Hold,Recovery/Removal,Minimum Pulse Width),功耗信息包括靜態功耗(Leakage Power)和動態功耗信息(Internal Power,Switching Power)。在抽取完相關信息后將其轉換成lib和verilog格式作為單元庫設計套件中的重要組成部分,最后將特征化信息以Datasheet形式供用戶參考。

圖3 單元特征化流程

布局布線文件通過Cadence Abstract Generator生成,基于單元版圖gds文件及包含布線規則的tf文件,按照Core、IO、Corner3個類別進行配置,通過設置Pins、Extract和Abstract菜單,完成Technology lef及單元lef的生成。

3.4 單元庫設計套件質量保證

最終生成的完整單元庫設計套件如表4所示,設計套件至少需包含網表文件cdl、版圖文件gds、時序功耗文件lib、功能仿真文件verilog、布局布線文件lef,這些文件覆蓋了正向設計全流程,任何一個文件問題均會對設計過程產生不良影響,因此必須對單元庫設計套件進行完整QA驗證。

表4 單元庫設計套件列表

完整QA驗證至少需包括設計數據一致性檢查、功能一致性檢查、時序一致性檢查以及后端設計檢查。設計數據一致性檢查主要確認cdl、lib、verilog、lef文件內單元數目、單元名稱、端口名稱是否一致;功能一致性檢查主要確認cdl、lib、verilog文件內單元功能是否一致;時序一致性檢查主要確認lib文件時序精度,確認lib、verilog時序條件描述是否一致,避免時序反標問題;后端設計檢查主要確認lef文件是否適配自動布局布線工具,確認基于所有單元隨機連接的網表不會產生錯誤,并完成布線后的整體版圖DRC及LVS檢查。

3.5 硅驗證

抗輻射單元庫硅驗證主要進行功能、性能及抗輻射能力的流片驗證。功能模塊應包含所有內核功能單元,每個單元輸出通過選擇器進行選擇,并提供功能全覆蓋的測試向量組合,功能模塊結構如圖4(a)所示;性能模塊通過鏈路測量基本單元性能,完成與晶體管級Spice仿真結果、門級靜態時序分析結果的對比,組合邏輯通過環振測試基本組合邏輯單元在不同負載下的性能,反向器環振結構如圖4(b)所示;時序邏輯通過鏈路測試鎖存器時鐘、數據到輸出的延遲,測試觸發器時鐘到輸出的延遲,結構如圖4(c)所示;移位寄存器模塊用于評價加固時序單元的抗輻射能力,單粒子試驗時通過輸出采樣確認翻轉次數,結構如圖4(d)所示;通過整個測試芯片確認IO單元輸入電平、輸出驅動、ESD能力等。

圖4 測試芯片模塊

最終完成硅驗證后的抗輻射單元庫基本信息如表5所示,在實現抗輻射指標的前提下,與同工藝節點的普通商用單元庫相比[10],對應的速度、面積、功耗增加的損耗在30%以內。

表5 抗輻射單元庫基本信息

4 結論

本文基于0.18 μm CMOS加固工藝的輻射加固方案,提出了完整的0.18 μm抗輻射單元庫的設計流程并完成測試芯片硅驗證,目前抗輻射單元庫已成功支撐多款抗輻射產品的開發,為后續大規模抗輻射數字電路設計奠定了基礎。