一種通用的時(shí)間數(shù)字轉(zhuǎn)換器碼密度校準(zhǔn)信號(hào)產(chǎn)生方法及其實(shí)現(xiàn)

李海濤 李斌康 田 耕 阮林波 趙 前 呂宗璟

(強(qiáng)脈沖輻射環(huán)境模擬與效應(yīng)國(guó)家重點(diǎn)實(shí)驗(yàn)室 西安 710024)

1 引言

時(shí)間作為物理學(xué)中7個(gè)基本物理量之一,在物理學(xué)的發(fā)展中起著至關(guān)重要的作用,精確獲取研究對(duì)象的時(shí)間信息具有重要的意義。對(duì)時(shí)間信息的獲取可以由時(shí)間數(shù)字轉(zhuǎn)換器(Time to Digital Converter, TDC)來(lái)實(shí)現(xiàn),TDC將時(shí)間間隔轉(zhuǎn)換為二進(jìn)制數(shù)字編碼,輸出到后端分析得到具體的時(shí)間信息。TDC廣泛應(yīng)用在高能物理、導(dǎo)航定位、衛(wèi)星授時(shí)、數(shù)字通信、醫(yī)學(xué)成像等眾多領(lǐng)域,特別是在高能物理實(shí)驗(yàn)中[1,2],TDC獲取的時(shí)間信息能夠間接反映粒子的動(dòng)量、質(zhì)量等信息,對(duì)鑒別粒子種類(lèi)、診斷粒子反應(yīng)過(guò)程等有很重要的作用。

TDC有多種實(shí)現(xiàn)方法,包括時(shí)間間隔擴(kuò)展法、時(shí)間幅度轉(zhuǎn)換法、直接計(jì)數(shù)法、時(shí)鐘分相法、游標(biāo)法、抽頭延遲鏈法和差分延遲鏈法等;各種方法可以獨(dú)立使用,也可以配合使用,可以實(shí)現(xiàn)從普通精度到高精度、從粗時(shí)間到細(xì)時(shí)間的時(shí)間間隔測(cè)量。從實(shí)現(xiàn)方法上來(lái)看,TDC的實(shí)現(xiàn)方法可以分為模擬方法和數(shù)字方法;從實(shí)現(xiàn)平臺(tái)上看,TDC可以在專(zhuān)用集成電路(Application Specific Integrated Circuit, ASIC)、現(xiàn)場(chǎng)可編程門(mén)陣列(Field Programmable Gate Array, FPGA)等平臺(tái)上實(shí)現(xiàn)。ASIC-TDC的測(cè)量精度和穩(wěn)定性更高,但是,ASIC-TDC都是針對(duì)某一具體應(yīng)用設(shè)計(jì),不具有普適性,并且開(kāi)發(fā)一款A(yù)SIC芯片周期很長(zhǎng);FPGA-TDC具有開(kāi)發(fā)周期短、集成度高、成本低、設(shè)計(jì)靈活等優(yōu)點(diǎn),但是其非線性較差。

隨著微電子技術(shù)、半導(dǎo)體制造工藝的發(fā)展,F(xiàn)PGA-TDC的測(cè)量精度、穩(wěn)定性等同步提高,在FPGA上實(shí)現(xiàn)高精度TDC具有重要研究意義。目前,基于FPGA實(shí)現(xiàn)的高精度TDC的研究主要集中在幾個(gè)方面:(1) TDC的實(shí)現(xiàn),基于FPGA內(nèi)部資源實(shí)現(xiàn)高精度TDC,把時(shí)間信息轉(zhuǎn)換成二進(jìn)制編碼,通過(guò)查找表輸出至后端;(2) TDC的自動(dòng)校準(zhǔn),選擇合適的校準(zhǔn)方法,校準(zhǔn)TDC的碼寬(bin size),降低FPGA制造工藝、工作電壓、工作溫度(Process Voltage Temperature, PVT)等參數(shù)對(duì)TDC性能的影響;(3)針對(duì)TDC內(nèi)部bin size的不一致性,如何平均化超寬bin,降低測(cè)量誤差,進(jìn)一步提高測(cè)試精度,單鏈多次平均測(cè)量(Wave Union,Ripple method)、多鏈單次平均測(cè)量等方法可以在已有工藝的基礎(chǔ)上,盡可能改善FPGA-TDC的非線性,提高測(cè)量精度;(4)其他特殊功能,如動(dòng)態(tài)監(jiān)測(cè)并實(shí)時(shí)校準(zhǔn)TDC的bin size,多通道TDC集成使用,針對(duì)特殊要求(如航天等)進(jìn)行TDC的冗余設(shè)計(jì)等。

論文主要研究FPGA-TDC的自動(dòng)校準(zhǔn)方法,給出碼密度校準(zhǔn)方法的誤差公式,分析了兩種常用碼密度校準(zhǔn)信號(hào)產(chǎn)生方法,提出了一種基于相干采樣理論的通用TDC碼密度校準(zhǔn)方法,通過(guò)合理設(shè)置TDC主時(shí)鐘和校準(zhǔn)信號(hào)之間的頻率差,結(jié)合輸出保持電路,產(chǎn)生校準(zhǔn)用的隨機(jī)信號(hào),確保在碼密度校準(zhǔn)過(guò)程中,隨機(jī)信號(hào)均勻分布在TDC的延時(shí)路徑上,實(shí)現(xiàn)對(duì)TDC的逐位(bin-by-bin)校準(zhǔn)。

2 TDC校準(zhǔn)方法

TDC的常用校準(zhǔn)方法主要分為平均校準(zhǔn)和逐位校準(zhǔn)兩種[3–5]。平均校準(zhǔn)可以對(duì)TDC進(jìn)行快速校準(zhǔn),但是,得到的只是所有延遲單元抽頭的平均延遲時(shí)間,無(wú)法對(duì)TDC中每個(gè)延遲單元抽頭進(jìn)行逐位校準(zhǔn),會(huì)導(dǎo)致較大的測(cè)量誤差。逐位校準(zhǔn)可以對(duì)級(jí)聯(lián)延遲鏈中每一個(gè)延遲單元抽頭進(jìn)行bin-by-bin校準(zhǔn),一般通過(guò)碼密度方法實(shí)現(xiàn),可以精確標(biāo)定每個(gè)延遲單元抽頭的延遲時(shí)間。

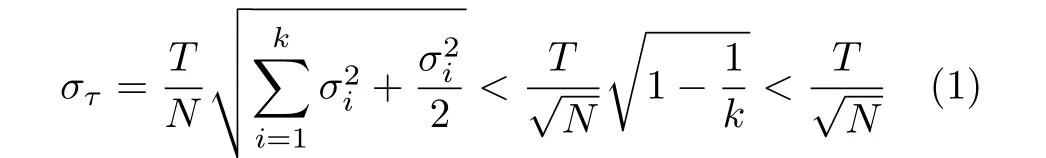

根據(jù)文獻(xiàn)[1]研究結(jié)果,在使用碼密度校準(zhǔn)方法校準(zhǔn)TDC的碼寬時(shí),為了盡可能降低延遲單元的時(shí)間誤差,需要增加校準(zhǔn)次數(shù),增加校準(zhǔn)次數(shù)就會(huì)增加校準(zhǔn)時(shí)間、增加資源占用量;使用時(shí)需要根據(jù)TDC指標(biāo)要求折中考慮。在校準(zhǔn)信號(hào)和TDC主時(shí)鐘無(wú)關(guān)的前提下,認(rèn)為校準(zhǔn)信號(hào)是隨機(jī)信號(hào),標(biāo)準(zhǔn)差和校準(zhǔn)次數(shù)之間的關(guān)系式如式(1)所示,式中,N為校準(zhǔn)次數(shù),k為級(jí)聯(lián)鏈抽頭數(shù)目,T為T(mén)DC主時(shí)鐘周期,T=5 ns,抽頭延時(shí)選擇碼寬的中間值,σi為第i個(gè)延遲單元的標(biāo)準(zhǔn)差,στ為校準(zhǔn)誤差最大值。根據(jù)式(1),已知文章實(shí)現(xiàn)的校準(zhǔn)次數(shù)為1000000次,對(duì)應(yīng)TDC的校準(zhǔn)誤差最大值小于5 ps;同理,如果校準(zhǔn)次數(shù)達(dá)到100000000次,對(duì)應(yīng)TDC的校準(zhǔn)誤差最大值小于0.5ps。從另一個(gè)角度分析,如果以5 ps步進(jìn)延時(shí)對(duì)TDC進(jìn)行校準(zhǔn),那么1000000次校準(zhǔn),總步進(jìn)時(shí)間為5 μs,相當(dāng)于對(duì)5 ns周期的時(shí)鐘遍歷1000次,且遍歷點(diǎn)不重復(fù)。

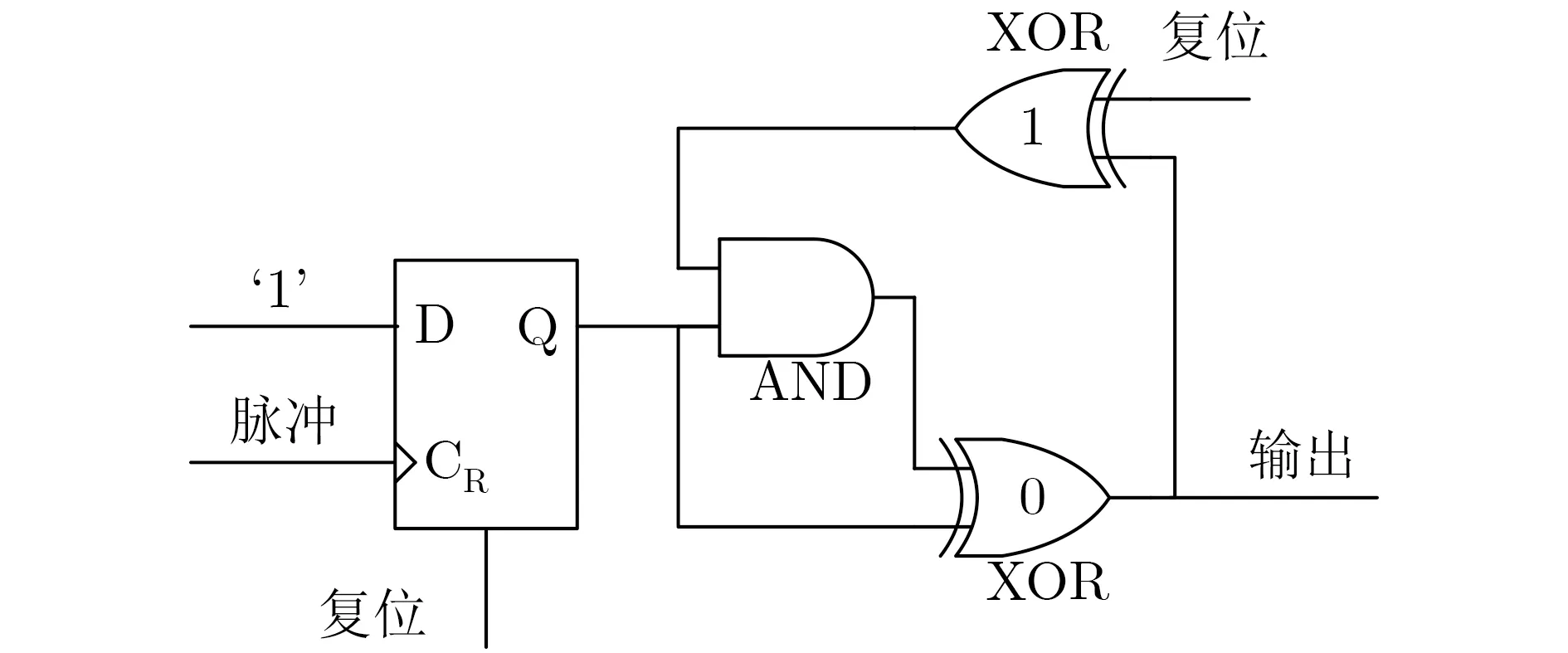

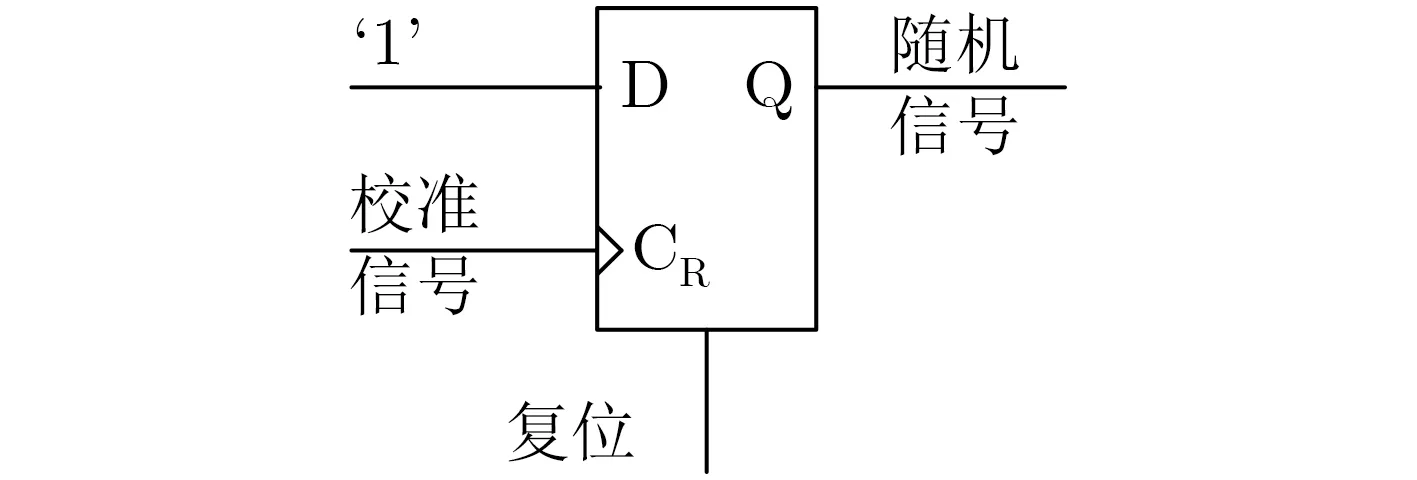

校準(zhǔn)信號(hào)產(chǎn)生:在游標(biāo)法實(shí)現(xiàn)的TDC中,給出了一種典型的起振電路,該電路利用了FPGA內(nèi)部的寄存器和門(mén)電路等資源,構(gòu)造了可控的數(shù)字振蕩電路如圖1所示[2],當(dāng)復(fù)位為‘0’,脈沖為‘0’時(shí),電路輸出為‘0’,處于穩(wěn)定狀態(tài);當(dāng)復(fù)位為‘0’,脈沖發(fā)生0–1跳變時(shí),系統(tǒng)開(kāi)始起振,電路輸出為周期振蕩波形,處于振蕩狀態(tài),震蕩周期值為門(mén)電路總延時(shí);當(dāng)復(fù)位發(fā)生0–1跳變時(shí),振蕩狀態(tài)結(jié)束,電路輸出為‘0’,回到穩(wěn)定狀態(tài)。這種電路結(jié)構(gòu)簡(jiǎn)單,門(mén)電路的延時(shí)一般在亞納秒量級(jí),可以產(chǎn)生高頻的振蕩信號(hào),通過(guò)改變信號(hào)的傳輸鏈路可以調(diào)節(jié)振蕩頻率;缺點(diǎn)是產(chǎn)生的振蕩信號(hào)受外界因素干擾明顯、振蕩頻率不穩(wěn)定且抖動(dòng)較大。一般來(lái)說(shuō),碼密度校準(zhǔn)方法的校準(zhǔn)次數(shù)較多,在一定程度上可以通過(guò)平均的方法降低這種抖動(dòng)的影響。

圖1 門(mén)控?cái)?shù)字震蕩電路

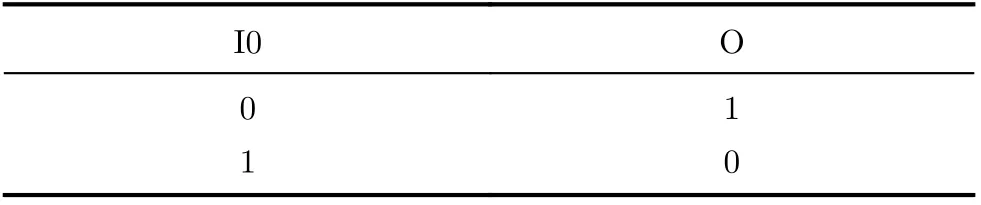

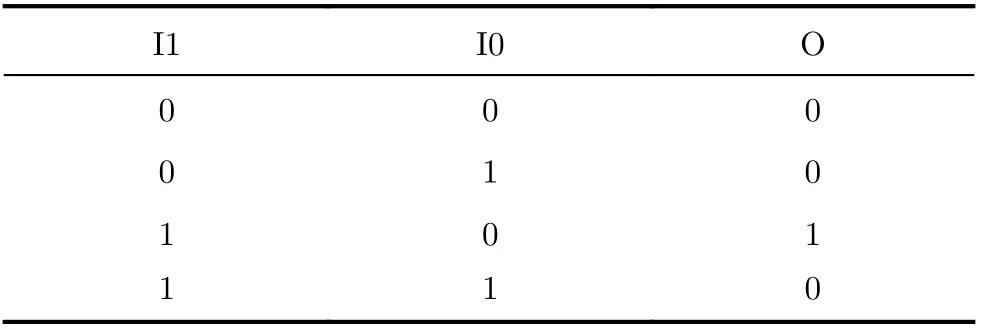

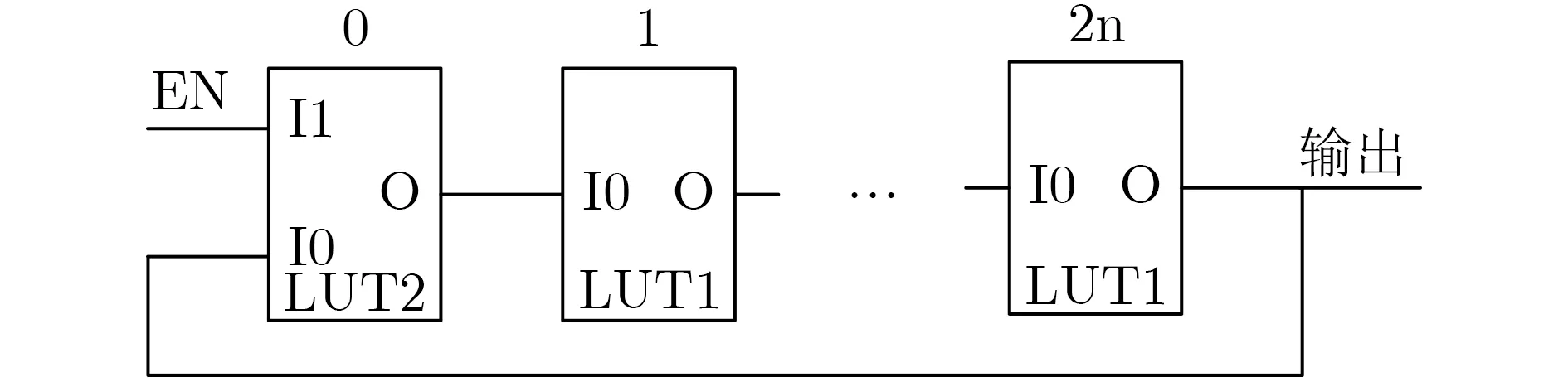

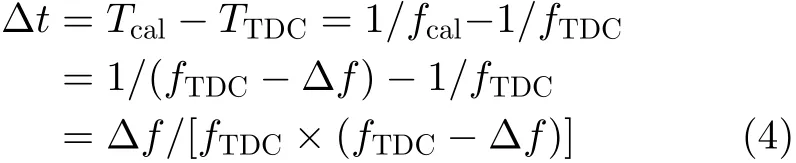

文獻(xiàn)[1]給出了一種利用FPGA內(nèi)部的查找表(Look-Up Table,LUT)資源,通過(guò)級(jí)聯(lián)查找表建立環(huán)形振蕩電路的方法。環(huán)形振蕩電路一般由奇數(shù)個(gè)反相器級(jí)聯(lián)而成,將最后一個(gè)反相器輸出反饋到第一個(gè)反相器輸入可以形成環(huán)形結(jié)構(gòu),達(dá)到振蕩的目的。FPGA是基于查找表結(jié)構(gòu)建立,擁有大量查找表資源且方便級(jí)聯(lián),可以通過(guò)配置查找表來(lái)實(shí)現(xiàn)反相器的功能[6]。由查找表LUT 1,LUT2構(gòu)成的環(huán)形振蕩器如圖2所示,總共包含一個(gè)LUT 2和偶數(shù)個(gè)LUT1,LUT1,LUT2的真值表如表1,表2所示,通過(guò)配置LUT 2內(nèi)部存儲(chǔ)值為“0010”,當(dāng)EN為‘0’時(shí),LUT2不受I0影響,輸出始終為‘0’;當(dāng)EN為‘1’時(shí),LUT 2的輸出O與輸入I0反向,實(shí)現(xiàn)反相器功能;通過(guò)配置LUT 1的內(nèi)部存儲(chǔ)值為“10”,實(shí)現(xiàn)反相器的功能。在校準(zhǔn)過(guò)程中,EN為‘1’時(shí),由查找表LUT 1與LUT 2組成的環(huán)形結(jié)構(gòu),相當(dāng)于奇數(shù)個(gè)反相器組成的環(huán)形振蕩電路;在測(cè)量或者待機(jī)時(shí),為降低功耗、降低干擾,EN為‘0’,由查找表LUT 1與LUT 2組成的環(huán)形結(jié)構(gòu),相當(dāng)于偶數(shù)個(gè)反相器,不形成振蕩。

表1 LUT1真值表

表2 LUT2真值表

圖2 利用查找表構(gòu)成環(huán)形振蕩器

3 一種新的校準(zhǔn)信號(hào)產(chǎn)生方法

前述的輸出振蕩信號(hào)作為校準(zhǔn)信號(hào)的方法,采用FPGA內(nèi)部的組合邏輯資源,基于自激振蕩原理產(chǎn)生可控周期振蕩,一般認(rèn)為產(chǎn)生的校準(zhǔn)信號(hào)與TDC主時(shí)鐘無(wú)關(guān),是隨機(jī)信號(hào)。在碼密度校準(zhǔn)過(guò)程中,如果校準(zhǔn)次數(shù)足夠多,認(rèn)為隨機(jī)信號(hào)近似均勻分布在TDC的延時(shí)路徑上,可以實(shí)現(xiàn)對(duì)TDC的高精度校準(zhǔn)。

TDC的碼密度測(cè)試與ADC的碼密度測(cè)試原理類(lèi)似,區(qū)別在于ADC的碼密度測(cè)試是對(duì)幅值隨機(jī)的模擬信號(hào)進(jìn)行量化統(tǒng)計(jì)分析,以標(biāo)定ADC的輸出數(shù)字編碼的非線性;TDC的碼密度測(cè)試是對(duì)時(shí)間隨機(jī)的數(shù)字信號(hào)進(jìn)行量化統(tǒng)計(jì)分析,以標(biāo)定TDC的延遲單元的非線性。在對(duì)ADC進(jìn)行動(dòng)態(tài)性能分析時(shí),需要對(duì)正弦波采樣數(shù)據(jù)進(jìn)行傅里葉分析,如果ADC采樣時(shí)鐘和待采樣正弦波頻率滿足嚴(yán)格的相干采樣條件,那么在進(jìn)行傅里葉分析時(shí),采樣信號(hào)的頻譜就不會(huì)出現(xiàn)泄漏現(xiàn)象;否則,采樣信號(hào)的頻譜會(huì)泄漏,主要原因之一就是ADC采樣的正弦波數(shù)據(jù)是非相干的,采樣數(shù)據(jù)點(diǎn)有重復(fù)。理論上相干采樣可以保證ADC采樣的正弦波數(shù)據(jù)之間沒(méi)有重復(fù)的,如果采樣數(shù)據(jù)量足夠大,相干采樣可以保證采樣數(shù)據(jù)點(diǎn)等效在一個(gè)正弦波波形上均勻分布。實(shí)際上這種理想條件很難實(shí)現(xiàn),只是近似成立,因?yàn)椴蓸訒r(shí)鐘頻率、正弦波頻率本身也有功率譜密度分布,并不是固定在一個(gè)頻率值上。

對(duì)ADC動(dòng)態(tài)性能測(cè)試而言,相干采樣條件如式(2),fs是采樣頻率,fin是待采樣正弦波頻率,M是采樣周期數(shù),NFFT是采樣點(diǎn)數(shù)。相干采樣條件要求M和NFFT為整數(shù),且互為素?cái)?shù),并且NFFT為2的整數(shù)次冪,可以將該條件等價(jià)為:NFFT為2的整數(shù)次冪,M為奇數(shù)或素?cái)?shù)。

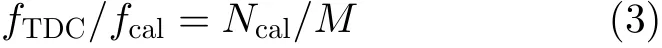

從相干采樣的角度分析TDC的碼密度校準(zhǔn)信號(hào)產(chǎn)生,借鑒ADC動(dòng)態(tài)性能測(cè)試中的相干采樣,研究TDC主時(shí)鐘和校準(zhǔn)信號(hào)的相干采樣問(wèn)題。對(duì)TDC碼密度校準(zhǔn)而言,可以根據(jù)要求對(duì)相干采樣公式進(jìn)行優(yōu)化,如式(3)所示,fTDC為T(mén)DC的主時(shí)鐘頻率,fcal為校準(zhǔn)信號(hào)頻率,M,Ncal為整數(shù)且互為素?cái)?shù),Ncal不要求是2的整數(shù)次冪,NFFT為2的整數(shù)次冪是傅里葉分析的要求,Ncal無(wú)此項(xiàng)要求。在滿足相干采樣且校準(zhǔn)次數(shù)足夠多的情況下,可以保證校準(zhǔn)信號(hào)均勻分布在TDC的延遲鏈上。

如果式(3)的fTDC,fcal兩者的頻率值非常接近,M,Ncal非常接近,Ncal/M的值接近于1。以fTDC作為基準(zhǔn),此處研究fTDC稍大于fcal的情況,fTDC–Δf =fcal,TTDC+Δt=Tcal,Δf,Δt都很小,在頻域上表現(xiàn)為頻率差值Δf,在時(shí)域上表現(xiàn)為時(shí)間間隔Δt,以fTDC作為基準(zhǔn)計(jì)算得到Δt如式(4)所示,fTDC稍小于fcal的情況同上述分析。

當(dāng)fcal,fTDC值相差比較小時(shí),以上時(shí)間差可近似為Δf/(fTDC×fTDC);當(dāng)fTDC值為200 MHz時(shí),對(duì)應(yīng)TTDC值為5 ns,如果要求TDC延遲鏈等效每隔10 ps就校準(zhǔn)一次,那么對(duì)應(yīng)的Tcal值為5.010 ns,求出對(duì)應(yīng)的fcal值約為199.6 MHz。實(shí)際上,并非每個(gè)TDC主時(shí)鐘周期都完成一次校準(zhǔn)。假設(shè)每5個(gè)TDC主時(shí)鐘周期完成一次校準(zhǔn)(其它要求不變),那么,對(duì)應(yīng)的Tcal值為5.002 ns,求出對(duì)應(yīng)的fcal值約為199.92 MHz時(shí),經(jīng)過(guò)5個(gè)TDC主時(shí)鐘周期,兩者相差10 ps。在FPGA上容易實(shí)現(xiàn)以上的頻率值,fTDC可以直接由外部時(shí)鐘源直接提供,上述計(jì)算得到的fcal頻率值可以利用FPGA內(nèi)部的混合模式時(shí)鐘管理模塊(Mixed-Mode Clock Management,MMCM)資源產(chǎn)生,這種情況下,fTDC和fcal采用同一個(gè)時(shí)鐘源,經(jīng)過(guò)FPGA內(nèi)部的MMCM產(chǎn)生校準(zhǔn)信號(hào),F(xiàn)PGA內(nèi)部的MMCM資源輸出附加的時(shí)鐘抖動(dòng)一般100 ps左右,單次校準(zhǔn)會(huì)增加TDC的時(shí)間誤差,同第2節(jié)描述,多次校準(zhǔn)可以把這種時(shí)間誤差平均化,最終實(shí)現(xiàn)對(duì)TDC延遲鏈的校準(zhǔn)。

另外一種情況是直接采用兩個(gè)標(biāo)稱(chēng)頻率值相同的時(shí)鐘源,分別作為fTDC和fcal的時(shí)鐘源,理論上兩個(gè)時(shí)鐘源的功率譜密度分布不完全相同,兩個(gè)時(shí)鐘源不可能輸出完全相同頻率值,兩者之間有很小的頻率差,可以認(rèn)為是相干采樣。前文已述,經(jīng)過(guò)MMCM之后的輸出會(huì)加入額外的時(shí)鐘抖動(dòng),因此可以把時(shí)鐘信號(hào)從專(zhuān)用引腳輸入,直接作為T(mén)DC的主時(shí)鐘、校準(zhǔn)信號(hào),可以降低傳播鏈路上的抖動(dòng)。

在碼密度校準(zhǔn)時(shí),如果校準(zhǔn)信號(hào)頻率過(guò)高且直接進(jìn)入到延遲鏈中,可能會(huì)造成TDC輸出編碼錯(cuò)誤,這就需要對(duì)校準(zhǔn)信號(hào)進(jìn)行輸出保持,以達(dá)到以下目的:(1)確保校準(zhǔn)過(guò)程中TDC的輸出編碼的有效性;(2)定義經(jīng)過(guò)輸出保持后的信號(hào)為隨機(jī)信號(hào),認(rèn)為隨機(jī)信號(hào)和TDC主時(shí)鐘無(wú)關(guān)。一種典型的輸出保持電路結(jié)構(gòu)如圖3所示,D觸發(fā)器輸入端置‘1’,把校準(zhǔn)信號(hào)作為D觸發(fā)器的時(shí)鐘信號(hào),校準(zhǔn)信號(hào)的上升沿開(kāi)始一次隨機(jī)過(guò)程,一次測(cè)量結(jié)束后對(duì)D觸發(fā)器進(jìn)行復(fù)位清零,等待校準(zhǔn)信號(hào)的下一個(gè)上升沿再次輸出高電平。由于校準(zhǔn)信號(hào)與TDC主時(shí)鐘滿足相干采樣條件,又經(jīng)過(guò)了一級(jí)輸出保持電路,輸出的隨機(jī)信號(hào)滿足碼密度校準(zhǔn)要求,可以根據(jù)式(1)計(jì)算校準(zhǔn)誤差最大值。

圖3 典型的輸出保持電路

4 實(shí)現(xiàn)及測(cè)試

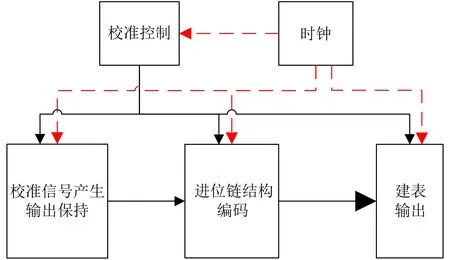

在Xilinx公司28 nm工藝的Kintex-7 FPGA上,采用級(jí)聯(lián)進(jìn)位鏈的方法設(shè)計(jì)實(shí)現(xiàn)plain TDC,共使用進(jìn)位鏈資源128個(gè),抽頭數(shù)量256個(gè),精細(xì)時(shí)間測(cè)量范圍大于5 ns。論文設(shè)計(jì)的校準(zhǔn)電路結(jié)構(gòu)如圖4所示。校準(zhǔn)電路模塊主要由校準(zhǔn)信號(hào)產(chǎn)生及保持部分、校準(zhǔn)控制部分構(gòu)成,校準(zhǔn)輸出的二進(jìn)制編碼結(jié)果進(jìn)入微分統(tǒng)計(jì)表、積分查找表(建表)等。校準(zhǔn)信號(hào)經(jīng)過(guò)保持電路之后認(rèn)為是隨機(jī)信號(hào),其產(chǎn)生及保持受校準(zhǔn)控制部分控制,隨機(jī)信號(hào)進(jìn)入到由級(jí)聯(lián)進(jìn)位鏈構(gòu)成的TDC中,精細(xì)時(shí)間測(cè)量結(jié)果通過(guò)二進(jìn)制編碼輸出到建表部分;校準(zhǔn)控制起到控制校準(zhǔn)使能、控制校準(zhǔn)次數(shù)、控制建表查詢(xún)輸出等作用;把每次獲得的校準(zhǔn)結(jié)果編碼送入微分統(tǒng)計(jì)表,根據(jù)微分統(tǒng)計(jì)表的結(jié)果建立積分查找表。在TDC測(cè)試時(shí),輸出對(duì)應(yīng)的二進(jìn)制編碼至后端分析得到具體的時(shí)間信息。

圖4 碼密度法校準(zhǔn)TDC碼寬示意

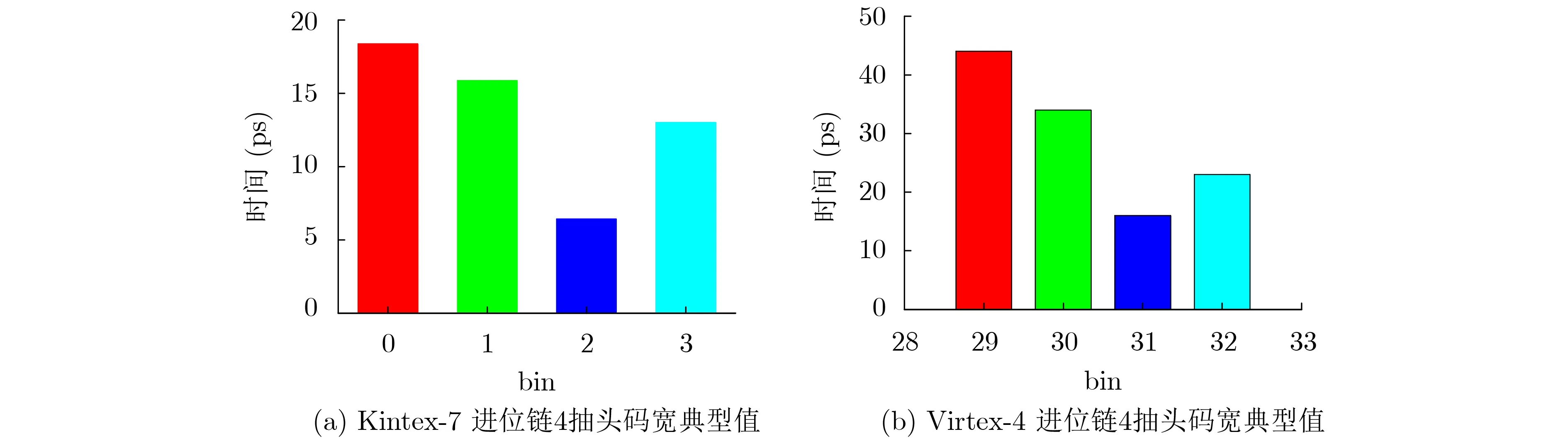

基于相干采樣理論,采用兩個(gè)獨(dú)立時(shí)鐘源分別作為fTDC和fcal的時(shí)鐘源,從專(zhuān)用時(shí)鐘引腳輸入,經(jīng)過(guò)MMCM之后,輸出作為T(mén)DC的主時(shí)鐘、校準(zhǔn)信號(hào),對(duì)進(jìn)位鏈plain TDC進(jìn)行碼密度校準(zhǔn)。Kintex-7上的單個(gè)進(jìn)位鏈一般可以輸出4個(gè)抽頭數(shù)據(jù),分別是CO0~CO3,經(jīng)過(guò)碼密度校準(zhǔn),典型的4抽頭的碼寬如圖5(a)所示,可見(jiàn)抽頭碼寬并不均勻,與文獻(xiàn)[4]中90 nm工藝的Virtex-4 FPGA的進(jìn)位鏈抽頭碼寬類(lèi)似,Virtex-4進(jìn)位鏈抽頭碼寬示意圖如圖5(b)所示。對(duì)比兩者,可見(jiàn)制造工藝的改進(jìn)的確降低了進(jìn)位鏈抽頭碼寬,但是,對(duì)進(jìn)位鏈抽頭碼寬的不均勻性改善不大。

圖5 Kintex-7進(jìn)位鏈4抽頭碼寬典型值

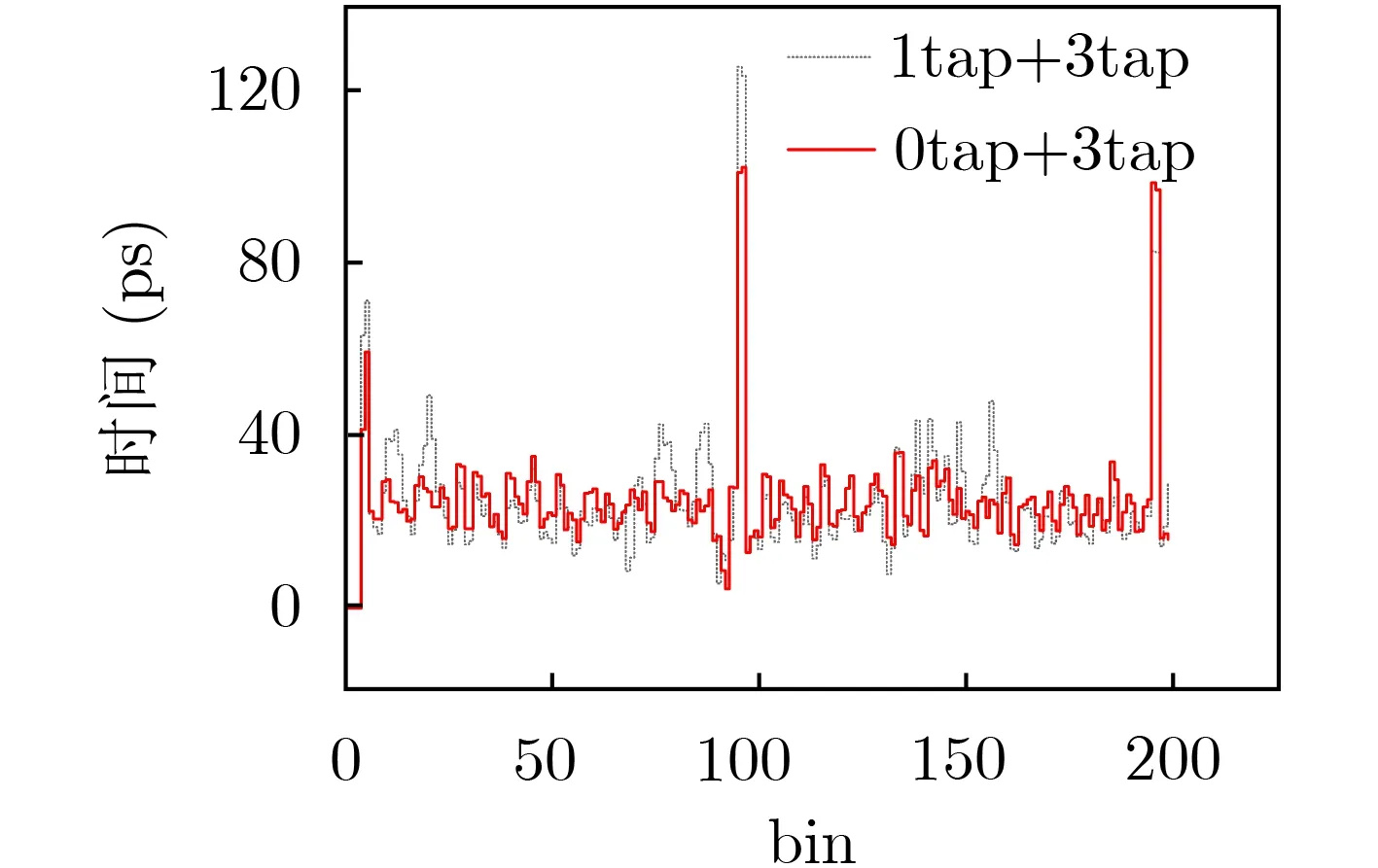

結(jié)合文獻(xiàn)[7–9]的建議,從一個(gè)進(jìn)位鏈引出兩個(gè)抽頭,將其分割為2個(gè)基本延時(shí)單元,分別是“CO0+CO3”和“CO1+CO3”兩種抽頭方式,對(duì)應(yīng)簡(jiǎn)寫(xiě)為“0tap+3tap”和“1tap+3tap”,研究了兩種抽頭方式對(duì)TDC分辨率和非線性的影響,結(jié)果如圖6所示,采用“CO0+CO3”的2抽頭方式,可以在TDC的分辨率和非線性之間取得較好的均衡。圖6顯示,每間隔100個(gè)碼址會(huì)出現(xiàn)一個(gè)超寬碼,這是因?yàn)橐粋€(gè)時(shí)鐘區(qū)域內(nèi)只有50個(gè)上下級(jí)聯(lián)的進(jìn)位鏈,每個(gè)進(jìn)位鏈引出2個(gè)抽頭,共100個(gè)抽頭,之后進(jìn)位鏈就需要跨時(shí)鐘域,不同時(shí)鐘域會(huì)導(dǎo)致超寬碼的產(chǎn)生。本文進(jìn)位鏈抽頭起始位置并不是時(shí)鐘區(qū)域的最底部,所以超寬碼出現(xiàn)在94,95,193,194抽頭處。

圖6 兩種2抽頭方式的碼寬典型值

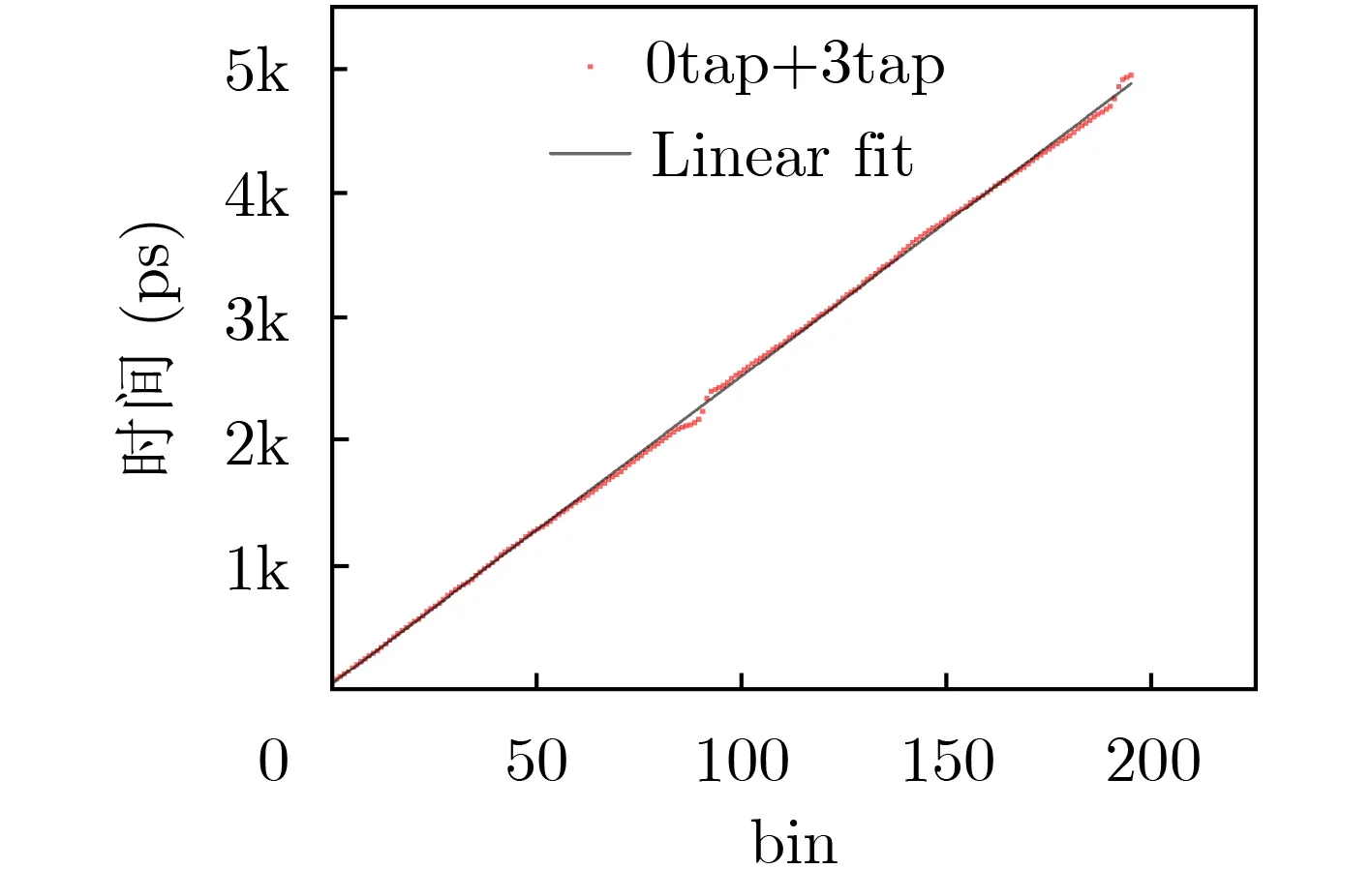

在“0tap+3tap”抽頭方式下,利用文中所述方法,校準(zhǔn)得到TDC的抽頭數(shù)量和延遲時(shí)間的值,經(jīng)過(guò)線性擬合之后的結(jié)果如圖7所示,時(shí)間分辨率為24.9 ps,對(duì)應(yīng)plain TDC輸出二進(jìn)制編碼的最低有效位(Least Significant Bit,LSB),圖7顯示的TDC的時(shí)間線性度較好,擬合優(yōu)度為0.9997。圖8(a)給出了校準(zhǔn)得到的TDC的微分非線性(Differential Non-Linearity,DNL)指標(biāo),在“0tap+3tap”抽頭方式下,DNL范圍(–0.84~3.1)LSB,DNL圖中的突出部分對(duì)應(yīng)的抽頭位置同圖6一致。圖8(b)給出了校準(zhǔn)得到的TDC的積分非線性(Integral Non-Linearity,INL)指標(biāo),在“0tap+3tap”抽頭方式下,INL范圍(–5.2~2.2)LSB。經(jīng)過(guò)對(duì)INL分析得到,在同一個(gè)時(shí)鐘區(qū)域內(nèi)自下向上級(jí)聯(lián)的進(jìn)位鏈,越向上,進(jìn)位鏈抽頭對(duì)應(yīng)的延遲時(shí)間值越小,對(duì)應(yīng)到圖8(a),抽頭位置從0到93,INL是一個(gè)緩慢下降的過(guò)程,抽頭位置從94到193,INL亦如是。對(duì)比參考文獻(xiàn)[1,2,4,10]中的TDC碼寬合非線性參數(shù)典型測(cè)試結(jié)果,本文所述校準(zhǔn)方法得到的結(jié)果與之符合較好,證明該方法可行。

圖7 “0tap+3tap”抽頭方式的TDC線性擬合結(jié)果

圖8 TDC的非線性示意

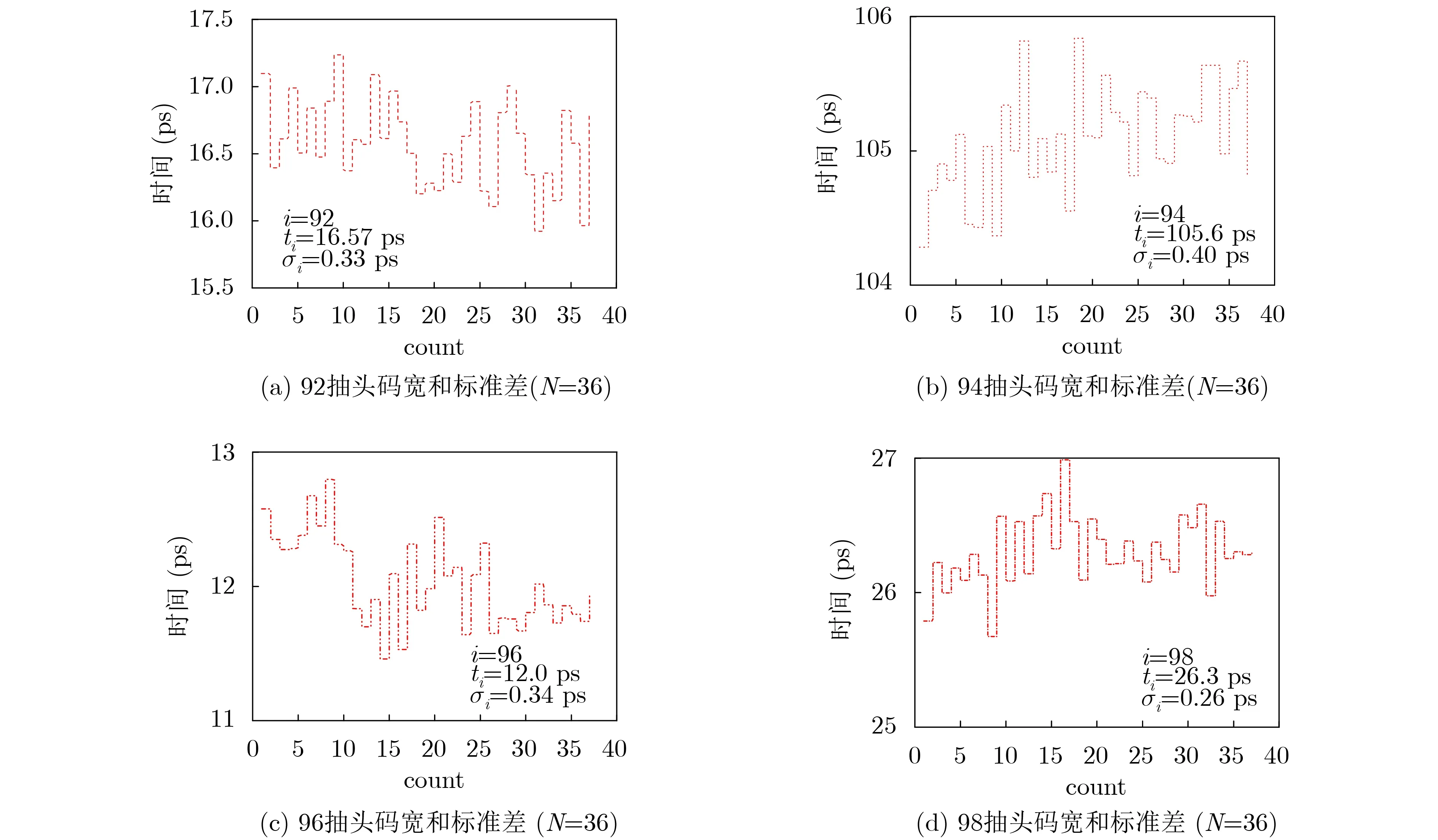

為了驗(yàn)證基于相干采樣的碼密度校準(zhǔn)結(jié)果的穩(wěn)定性和可重復(fù)性,多次校準(zhǔn)記錄同一個(gè)抽頭的延時(shí),反復(fù)測(cè)量36次(校準(zhǔn)次數(shù)N=36),其分布如圖9所示,分別顯示了i為92,94,96,98時(shí),共4個(gè)碼寬及其標(biāo)準(zhǔn)差,i表示抽頭位置,ti表示第i個(gè)抽頭碼寬,σi表示第i個(gè)抽頭標(biāo)準(zhǔn)差,其中抽頭94是跨時(shí)鐘域產(chǎn)生的。可以看到,4個(gè)抽頭的碼寬隨時(shí)間發(fā)生變化,縱軸時(shí)間變化范圍2 ps,測(cè)量36次,同一個(gè)抽頭碼寬的一致性比較好,σi優(yōu)于0.5 ps,根據(jù)前述式(1),已知文中所用校準(zhǔn)方法的校準(zhǔn)誤差最大值στ為5 ps(T=5 ns,N=1000000),σi遠(yuǎn)小于5 ps。

圖9 TDC典型碼寬和標(biāo)準(zhǔn)差

5 結(jié)論

基于相干采樣理論,本文提出并驗(yàn)證了一種通用的TDC碼密度校準(zhǔn)信號(hào)產(chǎn)生方法,確保TDC主時(shí)鐘和校準(zhǔn)信號(hào)的頻率相干,結(jié)合輸出保持電路,保證校準(zhǔn)用的隨機(jī)信號(hào)在TDC延遲路徑上的均勻分布,實(shí)現(xiàn)了對(duì)TDC的bin-by-bin校準(zhǔn)。采用Kintex-7 FPGA內(nèi)部的進(jìn)位鏈實(shí)現(xiàn)plain TDC,并利用所述的方法校準(zhǔn)plain TDC的碼寬,研究測(cè)試了2抽頭方式下的TDC性能參數(shù),在“CO0+CO3”的抽頭方式下,時(shí)間分辨率(對(duì)應(yīng)LSB)為24.9 ps,微分非線性為(–0.84~3.1)LSB,積分非線性為(–5.0~2.2)LSB,該測(cè)試方法得到的結(jié)果和經(jīng)典文獻(xiàn)[1,2,4,10]給出的測(cè)試結(jié)果符合較好。多次測(cè)試考核結(jié)果表明:文中所述方法采用的時(shí)鐘邏輯,單個(gè)延時(shí)單元的標(biāo)準(zhǔn)差優(yōu)于0.5 ps。對(duì)比兩種經(jīng)典的基于組合邏輯電路的碼密度校準(zhǔn)信號(hào)產(chǎn)生方法,本文基于相干采樣理論,提出了利用時(shí)鐘邏輯資源產(chǎn)生校準(zhǔn)信號(hào)的方法,校準(zhǔn)結(jié)果的穩(wěn)定性和重復(fù)性好。本文提出的通用碼密度測(cè)量方法同樣適用于其他類(lèi)型的TDC的碼密度校準(zhǔn)。