基于ATE的SAR型ADC修調算法與實現

楊曉強,劉若琛

(中國電子科技集團公司電子第24 研究所,重慶 400060)

0 引言

逐次逼近型模數轉換器由于其結構簡單、功耗低、效率高等特點[1],在醫療電子、可穿戴設備、便攜式儀表等領域具有廣泛應用前景,是目前高精度模數轉換器的主流研究方向之一。

SAR型ADC主要由采樣保持電路、電容陣列、比較器、控制邏輯等模塊組成。其中電容陣列精度直接決定ADC產品的最終精度,是SAR型ADC設計制造的關鍵。但由于現代集成電路加工精度限制、寄生效應等影響,批量流片加工的SAR型ADC通常無法達到12位以上直流精度[2],需通過修調技術提升電容陣列匹配度,以達到提升直流精度的目的。

1 SAR型ADC工作原理

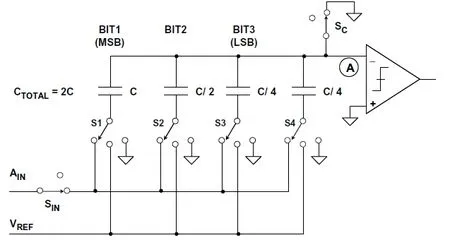

圖1為一款3位電容重分配SAR型ADC工作原理[3]。采樣階段開關SC和SIN閉合,模擬輸入電壓AIN開始對電容陣列充電;保持階段開關SC和SIN斷開,使比較器輸入負端電壓VA可以隨開關SX的位置不同而變化。如果開關S1-S4全部連接至地,則比較器輸入負端電壓VA等于-AIN;轉換階段首先將開關S1連接至VREF,此時VA等于1/2*VREF-AIN,比較器做出MSB位判斷,隨后S1繼續連接到VREF或地取決于比較器輸出高電平或低電平。按上述過程依次完成BIT2和BIT3電容后轉換階段結束,開關SC和SIN閉合,S1-S4連接至AIN,電路進入下一個采樣階段。

圖1 電荷重分配SAR 型ADC 原理

2 非線性誤差修調原理和算法

電荷重分配單元中各權重位電容之間的匹配精度直接影響SAR型ADC的最終線性度[4],因此,對電荷重分配SAR型ADC的修調即對電荷重分配單元中各權重位電容匹配度的調整。

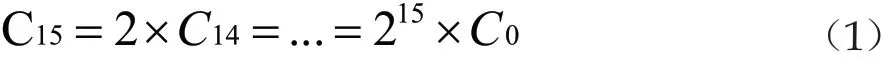

本文針對的目標器件為一款16位電荷重分配SAR型ADC。其電荷重分配單元原理如圖2所示。低十位權重電容陣列C0-C9通過橋接電容Cb與高六位權重電容陣列C10-C15連接。理想情況下,各權重電容值應滿足以下等式:

圖2 16 位電荷重分配單元原理圖

當工藝偏差導致某位權重電容CX偏大時,則該位的碼值權重降低,反之亦然。由于現代半導體工藝可保證低十位電容陣列的匹配精度,故僅需要對高六位電容進行修調。高六位可修調電容均采用多電容并聯設計,最小修調精度為0.5LSB,修調時根據需要對相應電容進行熔斷,以增大該位的權重。由于整體電容值只能減小,故其對應的位權重只能增大。

ADC的積分非線性誤差(INL)曲線可直觀反映其各位的失配程度,因此可根據其INL曲線計算電荷重分配單元中各權重電容的失配度和相應的修調值。每個主進位碼值點處的INL突變對應相應電容的失配程度。其中碼值32768處對應圖2中C15電容的失配程度;碼值16384處對應圖2中C14電容的失配程度,以此類推。

理想情況下,所有電容均應滿足式(1),電容C10-C15對應輸出碼值的INL突變均為0。如表1所示,設C10-C15對應輸出碼值的實測INL突變分別為I1-I6,則修調過程就是分別調整C10-C15位的權重,使I1-I6接近0。由于各電容值間的關系需滿足式(1),因此低電容位權重修調值還會影響其后所有高電容位權重的理論修調值。各電容位權重修調值計算如下:

表1 INL 與修調電容對應關系

其中Tx為相應修調電容位理論權重修調值,Ix為相應輸出碼值處的INL突變。。

根據修調原理,電容值只能減小,其對應的位權重只能增大。因此當均為正時,可直接對相應電容進行修調。當中的某一位為負時,還需分別增大其前面所有低電容位權重值,以使該位的理論權重修調值為0。當()為負時各電容位權重修調值計算如下:

3 基于ATE的系統軟硬件實現

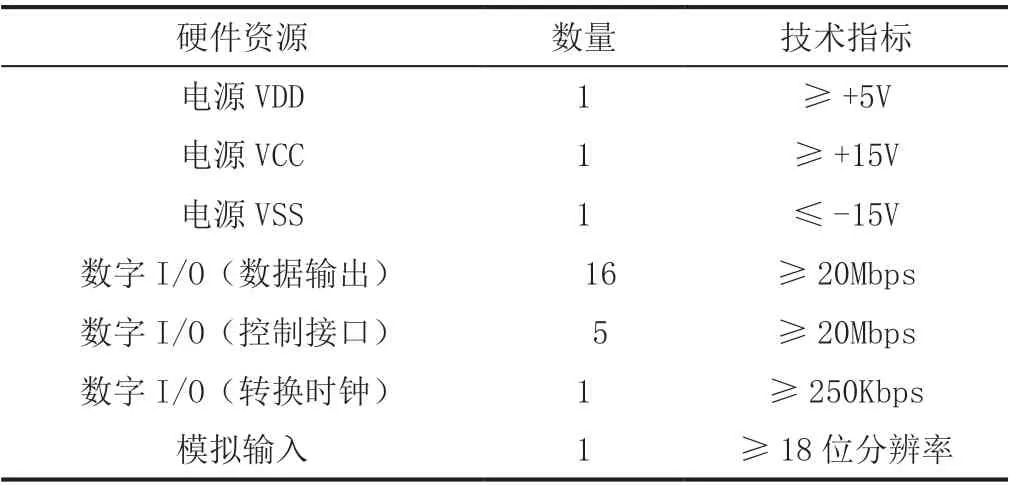

目標器件修調過程所需硬件資源見表2所示,修調數據寫入接口與數據輸出引腳復用,未單獨列出。

表2 目標器件修調過程所需硬件資源

自動修調系統基于ADVANTEST V93000型自動測試系統開發。該系統配置了256通道PS1600型1.6Gbps數字I/O單元[5],4通道MCE型寬頻段音/視頻測量單元,64通道AVI64型±30V V/I測量單元等硬件資源,可滿足目標器件修調需求。

由于各電容位權重修調值需根據未修調器件的INL曲線計算得出,而模擬輸入信號的波形和質量直接影響INL曲線測量的精度和效率,因此模擬輸入信號的設計是自動修調系統硬件設計的關鍵。

INL曲線測量一般采用碼密度直方圖法[6],模擬輸入信號可采用三角波或正弦波。由于高速高精度正弦波較三角波更容易獲取,因此在高速ADC測試中一般采用正弦波作為模擬輸入信號[7];但三角波作為模擬輸入信號時,可根據更少的采樣點數獲取更高的測量精度,因此在低速高精度ADC測試中一般采用三角波作為模擬輸入信號。目標器件為一款16位精度250Ksps采樣率ADC,因此本設計中采用三角波作為模擬輸入信號。

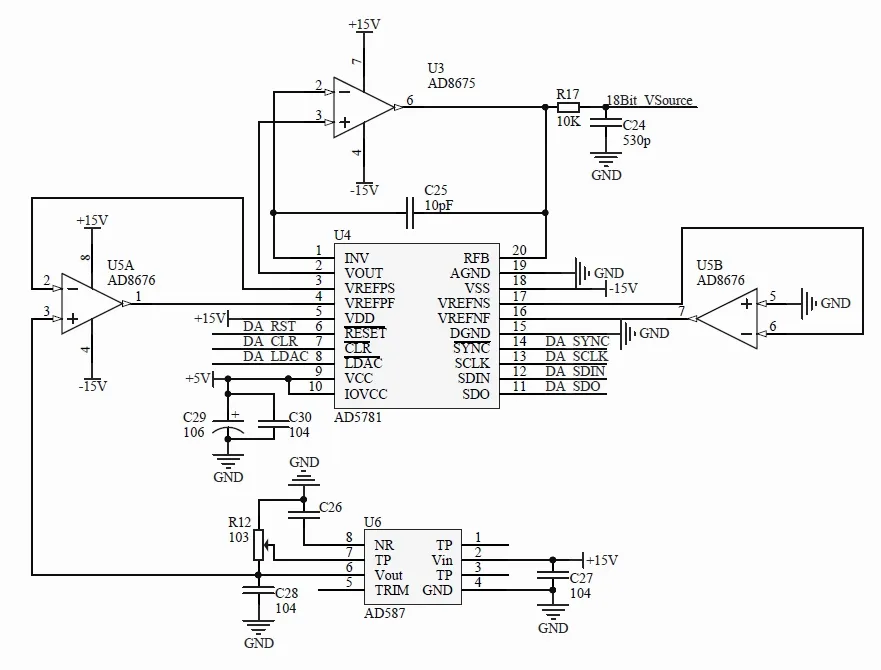

本設計中三角波由AD5781產生。AD5781是ADI公司生產的一款18位高精度數模轉換器[8],該器件可以在18位精度下保證積分非線性誤差小于±0.5LSB,滿足目標器件測量需求。AD5781使用單10V基準輸入,輸出使用高精度運算放大器配置為2倍增益,±10V輸出。輸出電壓后端連接RC濾波器濾除高頻噪聲。原理圖設計如圖4所示。

圖3 模擬輸入信號產生部分原理圖

圖4 程序流程框圖

其余硬件設計部分可直接將目標器件引腳接入相應的ATE硬件資源,不再一一贅述。

程序流程框圖如圖5所示。第一次計算得出修調碼后對目標器件進行預修調,預修調操作不執行熔絲熔斷程序,因此可多次修調。預修調后再次測試INL曲線,并根據此INL曲線判斷是否對修調代碼進行微調。當INL曲線達到指標要求時執行熔絲熔斷和固化程序,完成修調過程。

4 修調結果

修調前目標器件INL曲線如圖6所示,其中X軸為輸出碼值,Y軸為對應的INL數值。修調前INL曲線波動較大,最大INL接近6 LSB。

圖6 修調后INL 曲線

經自動修調系統修調后的INL曲線如圖7所示。修調后INL曲線相對平坦,最大INL小于2 LSB,達到技術指標要求。

5 結束語

本文簡要介紹了電荷重分配SAR型ADC的工作原理,提出了一種根據積分非線性誤差曲線計算電容陣列失配度及修調參數的方法。然后基于ADVANTEST V93000型自動測試系統設計并實現了一種16位精度的電荷重分配SAR型ADC自動修調系統,對目標器件非線性參數進行測試和修調,最終使目標器件積分非線性誤差小于±3LSB,測試和修調時間小于1分鐘,具備批量生產能力。