高壓直流輸電控制系統不同鎖相環特性對比

劉靜佳,李歡,于華龍,魏偉,張海棠,黃松強,龔英明,王子民,傅闖

(1. 直流輸電技術國家重點實驗室(南方電網科學研究院),廣州510663;2. 中國南方電網有限責任公司,廣州510663)

0 引言

目前國內在運常規直流輸電線路有30多條,直流輸電已成為影響中國大電網安全穩定運行的關鍵因素。這些直流工程中,常規直流輸電工程的閥控系統均采用以鎖相環為基礎的等間隔觸發方式,盡管其不主動控制直流系統,但其作為直流控制系統的基礎,直接影響控制系統的控制效果。而閥控系統觸發以鎖相環為基礎,其控制效果嚴重依賴于鎖相環對交流電壓的相位跟蹤能力[1-3]。

基于αβ坐標變換的傳統鎖相環(αβ-PLL),因結構簡單、易于實現、在系統對稱工況下的鎖相性能較好而被廣泛應用于高壓直流輸電工程中。但當電網電壓不平衡或畸變時其鎖相精度下降[4]。通過調整PI參數[5]或在其內部引入低通濾波器[6]來降低帶寬,可以減小諧波分量對鎖相同步過程的影響,但其動態響應速度會隨之降低。而近年來眾多文獻研究了各種新型鎖相環,基于復系數濾波器[7]、自適應陷波器[8]的鎖相環能解決電網三相電壓不平衡下的鎖相問題,但在諧波含量較大時鎖相的性能較差。基于滑動平均濾波法[9]、級聯延遲信號消除法[10]、并聯延遲信號消去法[11]的鎖相環均因濾波而導致動態響應變慢。

文獻[1]提出的基于廣義二階積分器的單相鎖相環(single-PLL),具有較強的諧波和負序電流抑制能力,其與分相觸發控制結合,能夠在三相不對稱工況下減小常規直流各閥實際觸發角的差異,控制靈活,可有效降低交流故障恢復過程發生后續換相失敗的概率。文獻[4]指出采用MDSC前置濾波器的新型鎖相環(MDSC-PLL)具有更寬的頻率適應性,在各種故障工況下均能快速準確鎖定相位,且能有效降低高壓直流輸電系統發生后續換相失敗的機率。但各文獻僅局限于其所提鎖相環之優點,缺乏各種鎖相環間的橫向對比數據。

鑒于文獻[1]所提新型單相鎖相環和文獻[4]所提新型三相鎖相環均有降低高壓直流輸電系統換相失敗機率的優勢,本文對比分析傳統基于αβ坐標變換鎖相環(αβ-PLL)、基于SOGI-QSG的新單相鎖相環(single-PLL)、基于MDSC前置濾波器的新型三相鎖相環(MDSC-PLL)3種鎖相環的優缺點,及對常規高壓直流輸電控制系統的影響,通過RTDS驗證3種鎖相環在各種典型工況下的響應特征,對比分析各鎖相環在抗諧波、抗負序、寬頻率適應性、交流故障穿越方面的優越性。

1 鎖相環在高壓直流輸電系統中的應用

常規直流換流站大多采用整流側控制直流電流、逆變側控制直流電壓的控制策略,兩側設置相同的控制器但配置不同的控制參數,輸出不同的觸發角,實現兩側協調運行。兩側閥控系統在觸發相位控制作用下,根據各自的觸發角和換相電壓波形確定換流閥的開通時刻,完成控制任務。

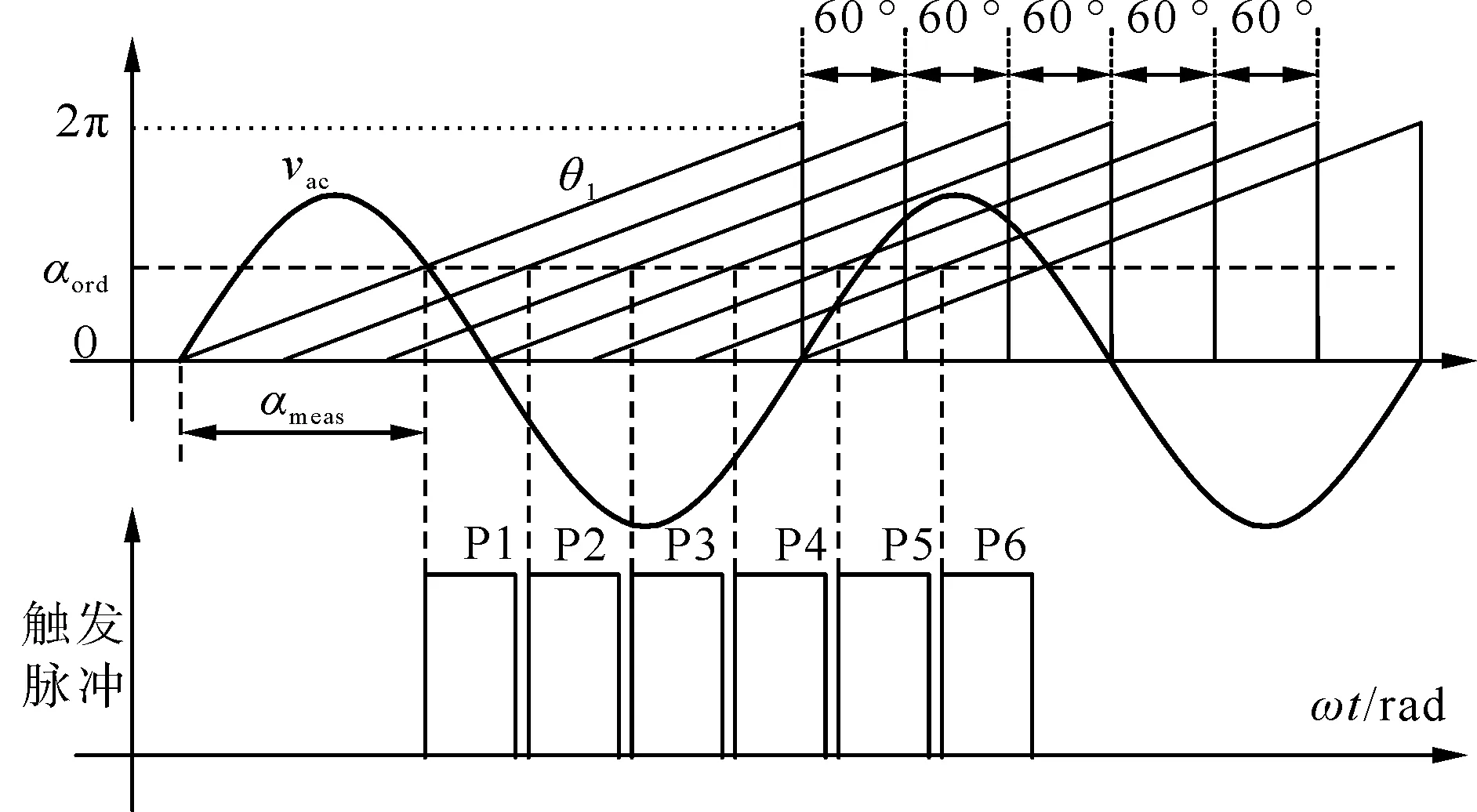

目前世界上在運常規直流輸電工程均采用該觸發控制技術,即等間隔觸發控制。工程中采用的一種等間隔觸發控制發法原理如圖1所示,利用鎖相環輸出閥1換相電壓Vac的同步相位θ,將該相位采用延遲的辦法形成等相位間隔,并直接利用觸發角指令和同步相位進行比較生成觸發脈沖。

圖1 等間隔觸發控制原理圖Fig.1 Control principle diagram of equal-inteval trigger

當鎖相環精度不高時,實際觸發角與觸發角指令值不符,即αord≠αmeas,閥實際響應特征與控制期望不符,影響直流系統的穩定運行。二者偏差過大時,甚至會出現觸發脈沖發出時,閥承受反向電壓,不具備導通條件的極端工況。

當交流系統發生故障時,交流電壓發生畸變,鎖相環若不能快速跟蹤相位,其輸出的相位角將與實際相位角偏差很大。若在逆變側,閥觸發脈沖信號極易產生較大的故障延遲,導致即將關斷的閥的關斷時間過小,閥無法恢復阻斷能力繼而持續導通,最終造成換相失敗。

由此可見,作為觸發控制的關鍵因素,鎖相環的鎖相精度將直接影響觸發脈沖的生成,進一步影響控制系統的控制效果。因此研究對比鎖相環的鎖相能力對保證直流輸電控制系統穩定、提升直流輸電控制系統故障應對能力至關重要。

2 鎖相環數學模型

2.1 基于αβ坐標變換鎖相環

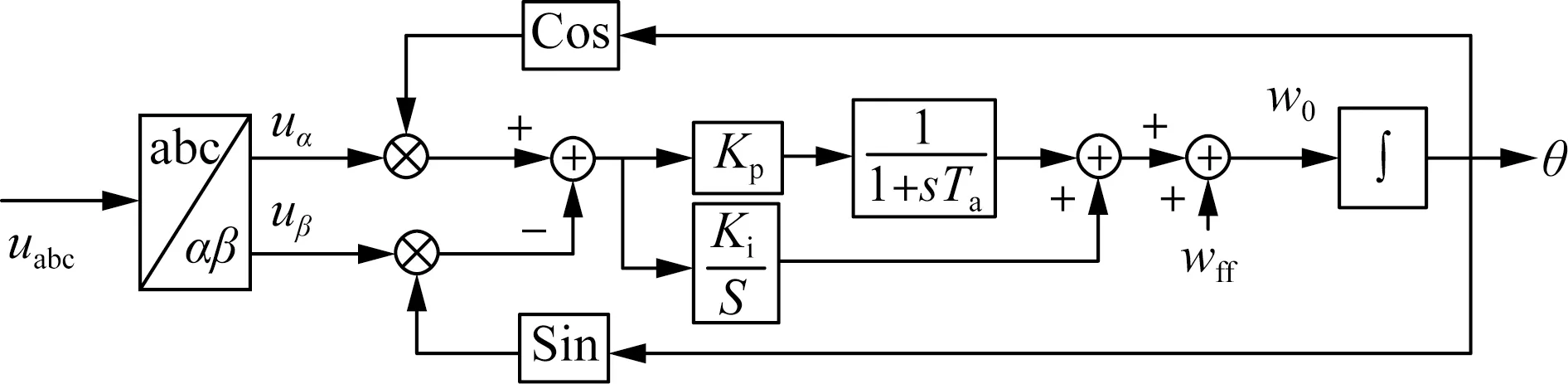

傳統基于αβ坐標變換鎖相環為高壓直流輸電系統中常用的鎖相環之一,其工作原理如圖2所示。

圖2 基于αβ坐標變換的鎖相環原理Fig.2 Principle of PLL based on αβ coordinate transformation

基于αβ坐標變換的鎖相環采用Clark變換得到αβ坐標系下的電壓分量uα和uβ,將uαcosθ-uβsinθ送入PI控制器,疊加計算步長對應的基波角頻率值,經過積分器后得到電壓相位θ,當輸出相位θ與三相交流電壓uabc相位α一致時,uαcosθ-uβsinθ為0,PI控制器停止調節,θ鎖定跟隨α。同時在比例環節后設置低通濾波環節,抑制諧波干擾。

該鎖相環結構簡單,易于實現,在系統對稱工況下的鎖相性能較好,正常情況下,PLL能準確跟蹤基頻正序電壓分量的相位;但當輸入的三相電壓不平衡或發生畸變時,鎖相環的跟蹤性能會受到諧波的影響,通常將PLL的帶寬設置得很小來減小諧波分量對鎖相同步過程的影響,但會相應地降低其動態響應速度。

2.2 基于二階廣義積分器的單相鎖相環

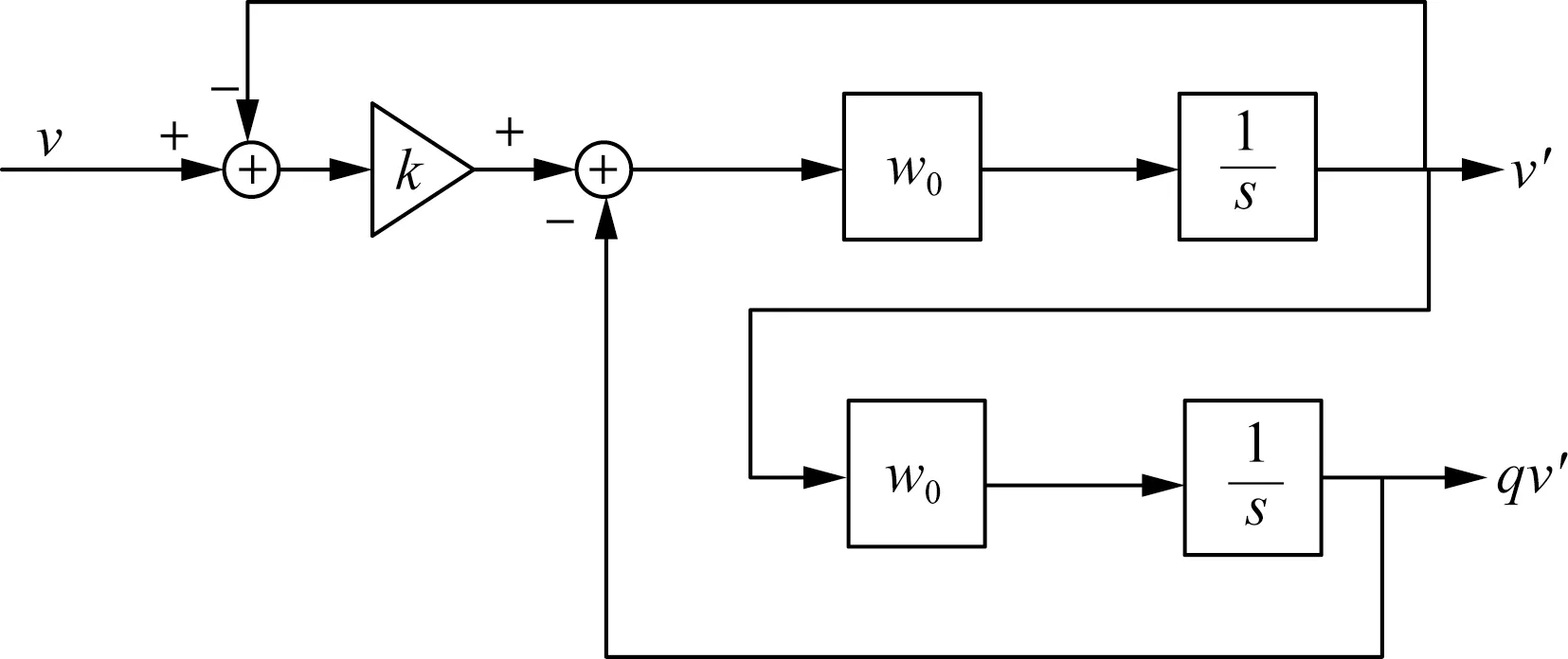

二階廣義積分器原理圖如圖3所示。

圖3 SOGI-QSG原理圖Fig.3 Principle diagram of SOGI-QSG

基于二階廣義積分器的單相鎖相環原理如圖4所示。

圖4 基于SOGI-QSG的單相鎖相環原理圖Fig.4 Principle diagram of SPLL based on SOGI-QSG

二階廣義積分器中,輸出信號v′可以實現對輸入信號v中角頻率為w0的正弦信號無靜差跟蹤,qv′總是滯后v′ 90 °。基于上述原理的單相鎖相環以v′和qv′做αβ/dq變換,變換后的d軸分量進入PI得到相位,因v′僅含有v中角頻率為w的正弦信號,因此鎖相環濾波效果良好。同時當輸入信號角頻率ω與ω0不同時,鎖相環輸出的頻率反饋至SOGI-QSG中,作為其諧振頻率,可以實現頻率自適應。

在常規直流輸電系統中,SPLL與分相觸發方案結合[1],即分別對換相電壓Vac、Vba、Vcb進行鎖相,將輸出的相位θac、θba、θcb與觸發角指令值進行比較,得到閥P1、P3、P5的觸發脈沖,將輸出的相位θac、θba、θcb延時180 °與觸發角指令值進行比較,得到閥P4、P6、P2的觸發脈沖。該觸發方式較傳統基于過零點檢測的分相觸發方式,觸發參考相位更準確,不會直接受過零點波動的影響;與目前工程常用的等間隔觸發方式相比,具有獨立的觸發相位控制電路,控制靈活,具有抗負序電壓干擾、抗諧波干擾能力。

2.3 采用MDSC前置濾波器的新型三相鎖相環

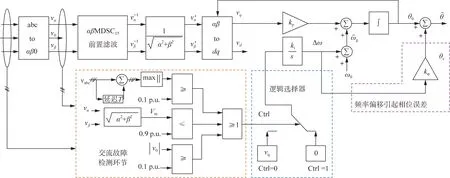

采用MDSC前置濾波器的新型三相鎖相環原理如圖5所示。

圖5 采用MDSC濾波的鎖相環原理圖Fig.5 Principle diagram of PLL with MDSC filter

該新型三相鎖相環在基于dq坐標變換鎖相環基礎上,增加了濾波、頻率適應、故障處理環節,以抵抗諧波干擾、擴寬頻率適應性、增強交流故障適應能力。

1)增加MDSC15前置濾波器,坐標變換后的αβ分量經濾波器提取純凈的基波正序分量,增加濾波功能的同時,又保證了動態響應的速度及穩定性。

2)增加頻率偏移補償,當電網頻率發生偏移Δωg時,基波電壓正序分量將產生-Δkφωg的相位偏移。因此將PI控制器積分環節的輸出作為頻率偏移量Δω,乘以kφ得到相位偏移量,將其補償到鎖相環輸出的同步相位中去,保證鎖相環在頻率發生偏移時還能準確地跟蹤電壓相位。

3)增加故障檢測環節,當發生故障時,通過邏輯選擇器將PI控制器的積分環節的輸入由vq變為0,使得鎖相環輸出的頻率固定為故障之前的頻率,實現了對鎖相環相位檢測和頻率檢測的解耦,加速PLL在故障暫態過程中對電壓相位的鎖定。

3 高壓直流工程RTDS試驗平臺

為橫向對比上述3種鎖相環的優缺點,方便各個工程因地制宜選擇合適的鎖相環,本文借助魯西背靠背直流輸電工程RTDS硬件閉環試驗平臺對上述3種鎖相環進行測試分析。

試驗平臺的系統示意圖如圖6所示。

圖6 RTDS閉環試驗平臺示意圖Fig.6 Schematic diagram of RTDS closed-loop test platform

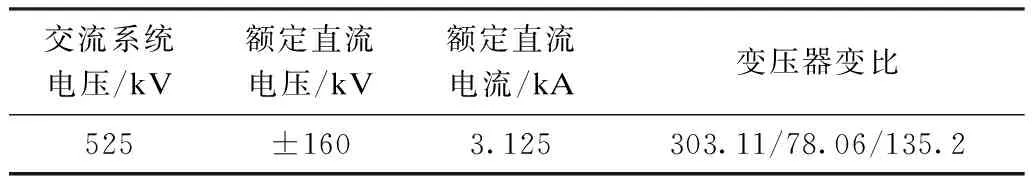

圖中左框為控制保護裝置,自上而下依次為監控層、交直流站控層、單元控制層。各裝置全部采用高壓直流輸電系列裝置—采用高性能多核DSP+大容量FPGA集成技術,滿足高壓直流輸電系統對大量信號的高精度、快速處理需求。右框為RTDS仿真設備,在RTDS軟件中搭建一次回路模型,接收控制保護裝置發出的控制指令,完成主回路一次設備的模擬運算,并輸送實時變量至控制保護裝置和錄波裝置。其中一次回路參數如表1所示。

表1 RTDS測試平臺參數Tab.1 Parameter of RTDS test platform

本文在上述測試平臺上修改單元控制層裝置中鎖相環及閥觸發邏輯涉及的DSP及FPGA程序,實現上述3種鎖相環,在相同的工況下測試各個鎖相環的鎖相性能及其對控制系統的影響。

高壓交流電網可能出現相位跳變、電壓不平衡跌落、頻率偏移、諧波以及電壓負序分量等問題。因此,本文設計以下7種測試工況來考察新型鎖相環的穩態和暫態性能。各個鎖相環中均帶有PI控制器,PI參數直接決定鎖相環的動態和穩態響應性能。因此本文先在相同的交流電壓相位階躍工況下,調節各個鎖相環的PI參數,以達到基本相同的動態響應性能,并在該參數下進行后續工況測試,最終各個鎖相環PI參數如表2所示。

表2 各個鎖相環PI參數表Tab.2 PI Parameter of PLLs

4 鎖相環RTDS測試分析

4.1 交流電壓相位階躍測試

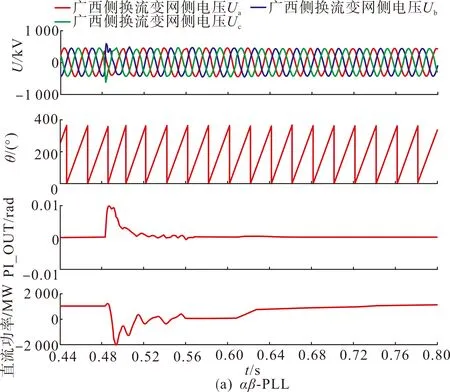

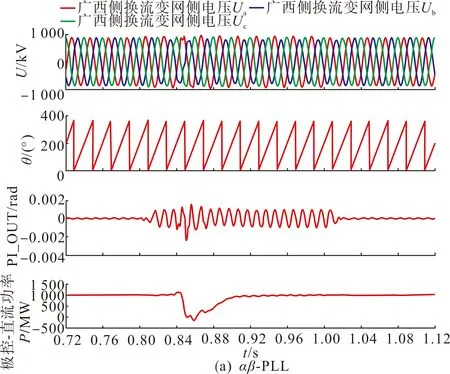

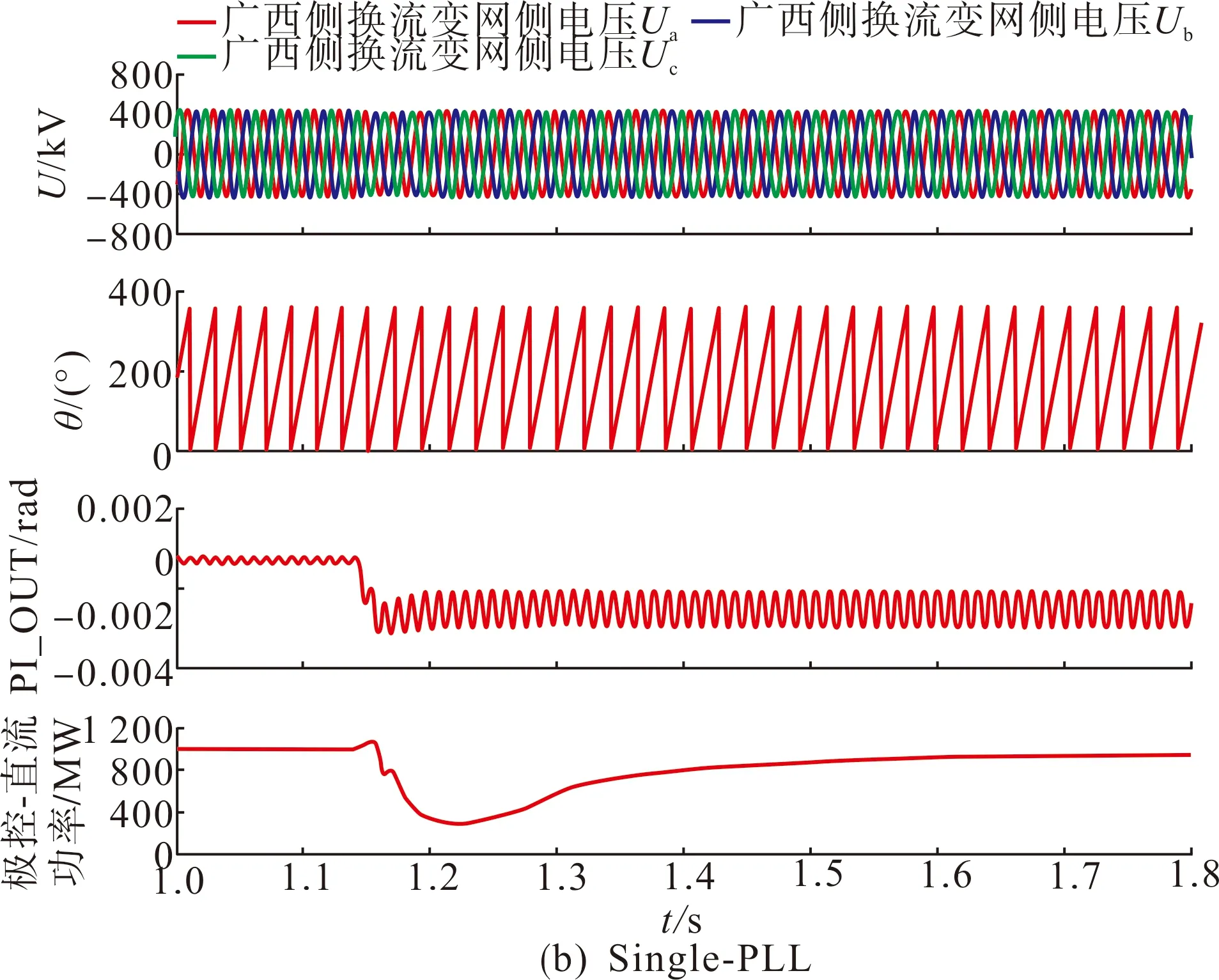

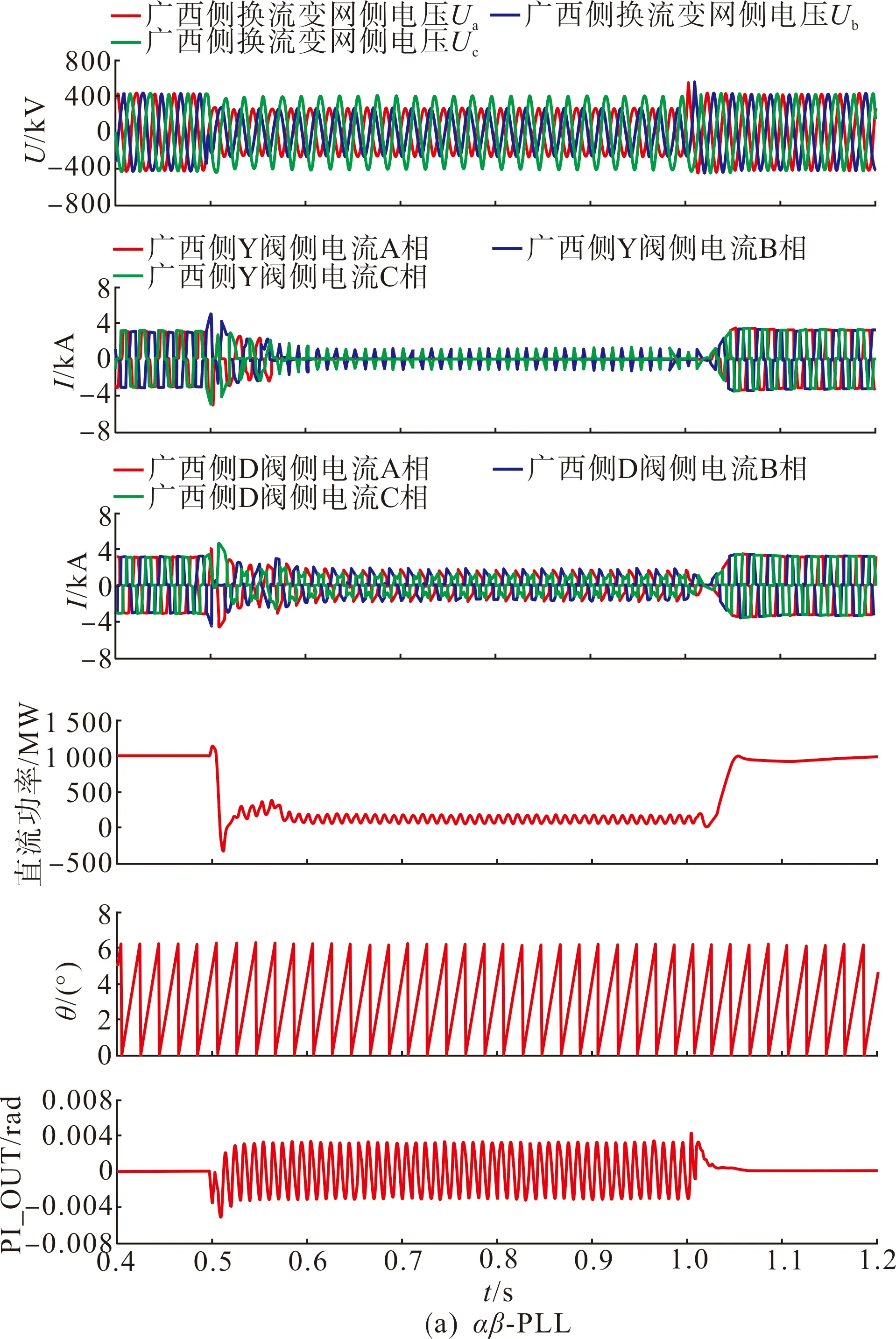

在滿功率運行時,在RTDS上更改廣西側交流電壓初始相位值由0 °突變為90 °,測試波形如圖7所示。

圖7 交流電壓相位階躍測試波形Fig.7 Test waveforms during AC-voltage phase mutation

圖中可見,當交流電壓相位階躍時,3種鎖相環均能快速跟蹤相位,PI輸出調節至穩定時間一致。

在交流電壓相位階躍時,直流功率發生波動,從階躍開始至直流功率恢復至階躍前90%,3種鎖相環均需要220 ms左右,但采用Single-PLL時直流功率由0開始增大時間明顯短于其他2種鎖相環。

4.2 抗諧波性能測試

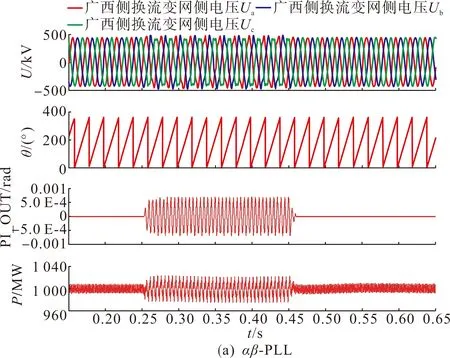

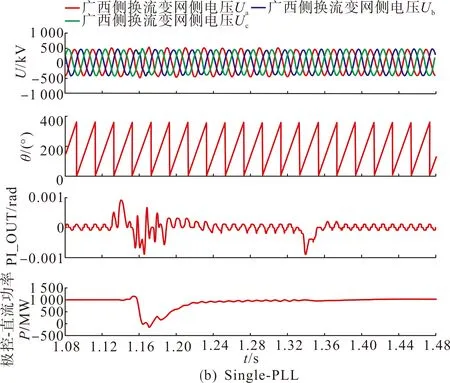

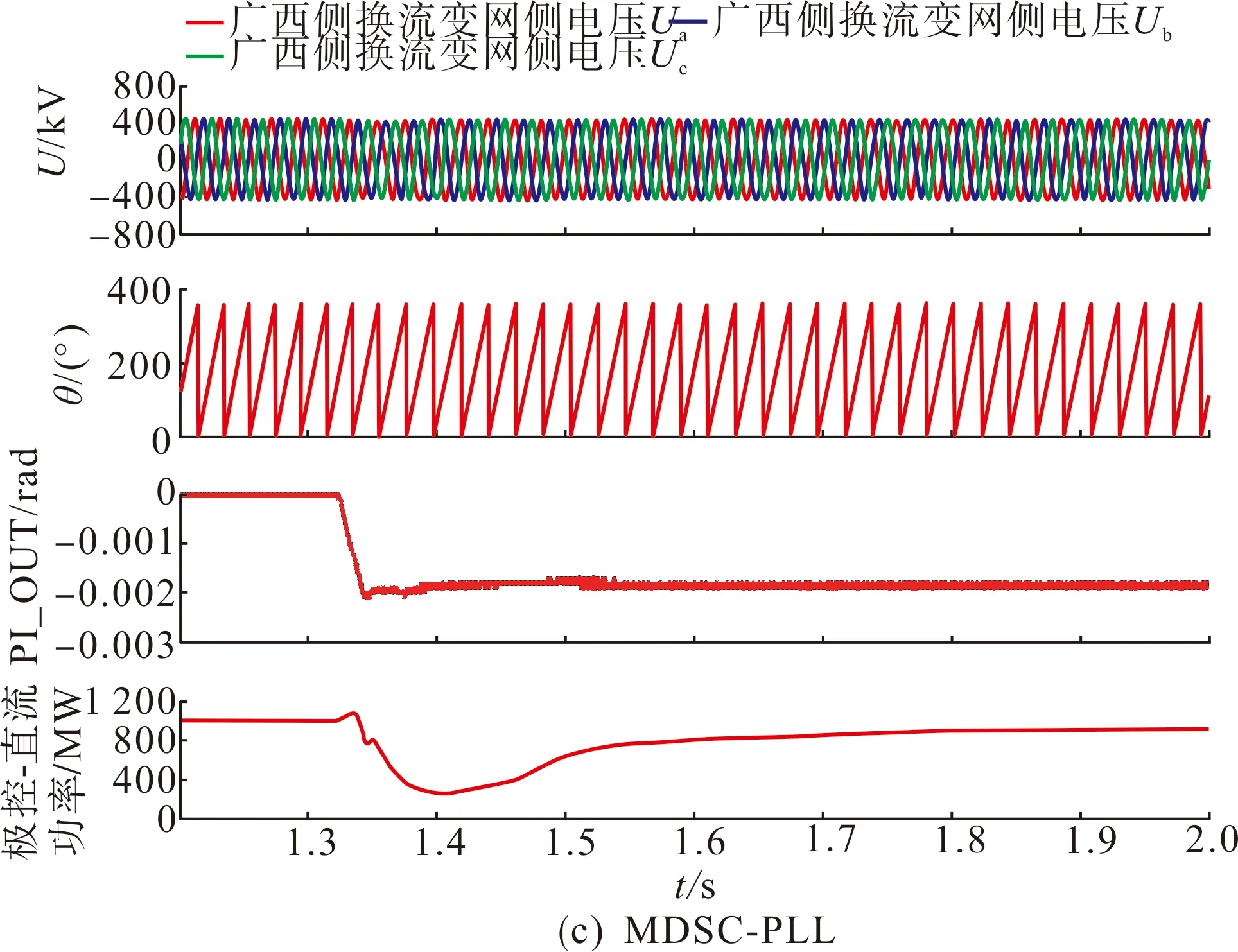

在滿功率運行時,在RTDS中設置廣西側交流電壓加入10%的5次諧波,持續時間200 ms,測試波形如圖8所示。

圖8 交流電壓帶諧波時測試波形Fig.8 Test waveforms during AC-voltage with harmonic wave

根據圖8可見,在5次諧波影響下,傳統αβ-PLL的PI輸出出現4倍頻波動,波動幅值約為0.000 7 rad;Single-PLL的PI輸出出現2頻波動,波動幅值為0.000 7 rad;MDSC-PLL的PI輸出波動最小,幅值為0.000 3 rad。

在交流系統加入諧波分量時,直流功率均會出現波動,波動量一致,諧波消除后功率均立即恢復穩定。

可見,相較于傳統鎖相環,新型單相鎖相環和MDSC-PLL均具有更優異的抗諧波干擾能力,其中MDSC-PLL性能最優。

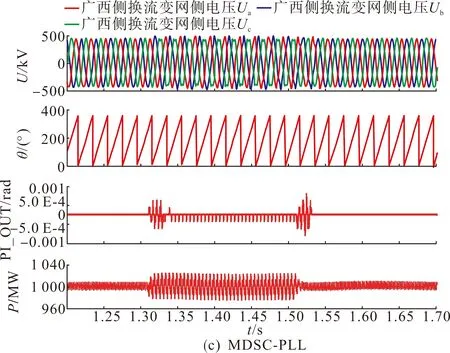

4.3 抗負序性能測試

在滿功率運行時,在RTDS中設置廣西側交流電壓加入10%的負序分量,持續時間200 ms,測試波形如圖9所示。

圖9 交流電壓帶負序時測試波形Fig.9 Test waveforms during AC-voltage with negative sequence

圖中可見,傳統αβ-PLL在負序干擾過程中有較明顯的2倍頻波動;Single-PLL和MDSC-PLL僅在負序干擾開始和結束時有波動,可快速達到穩定狀態。

在負序干擾工況下,直流功率均出現跌落,采用傳統αβ-PLL和Single-PLL時,直流功率恢復至故障前功率水平均需要95 ms左右;而采用MDSC-PLL時僅需85 ms。相較于傳統αβ-PLL,Single-PLL和MDSC-PLL具有優異的抗負序效果。

4.4 頻率階躍測試

在滿功率運行時,在RTDS中設置廣西側交流電壓頻率突變至47 Hz,測試波形如圖10所示。

圖10 交流電壓頻率階躍至47 Hz測試波形Fig.10 Test waveforms during AC-voltage frequency step up to 47 Hz

圖中可見,頻率階躍至47 Hz后,傳統αβ-PLL和MDSC-PLL的PI輸出負向偏置,無波動,能穩定跟蹤相位;Single-PLL的PI輸出負向偏置的同時,存在幅值為0.001 2的2倍頻波動。

在47 Hz頻率擾動工況下,直流功率均出現跌落,采用Single-PLL時控制系統在429 ms內恢復至故障前功率水平;MDSC-PLL需要468 ms恢復穩定;傳統αβ-PLL恢復至突變前功率水平需要509 ms。

傳統αβ-PLL和MDSC-PLL加入47 Hz頻率擾動后,無波動,對頻率偏差的適應性好。

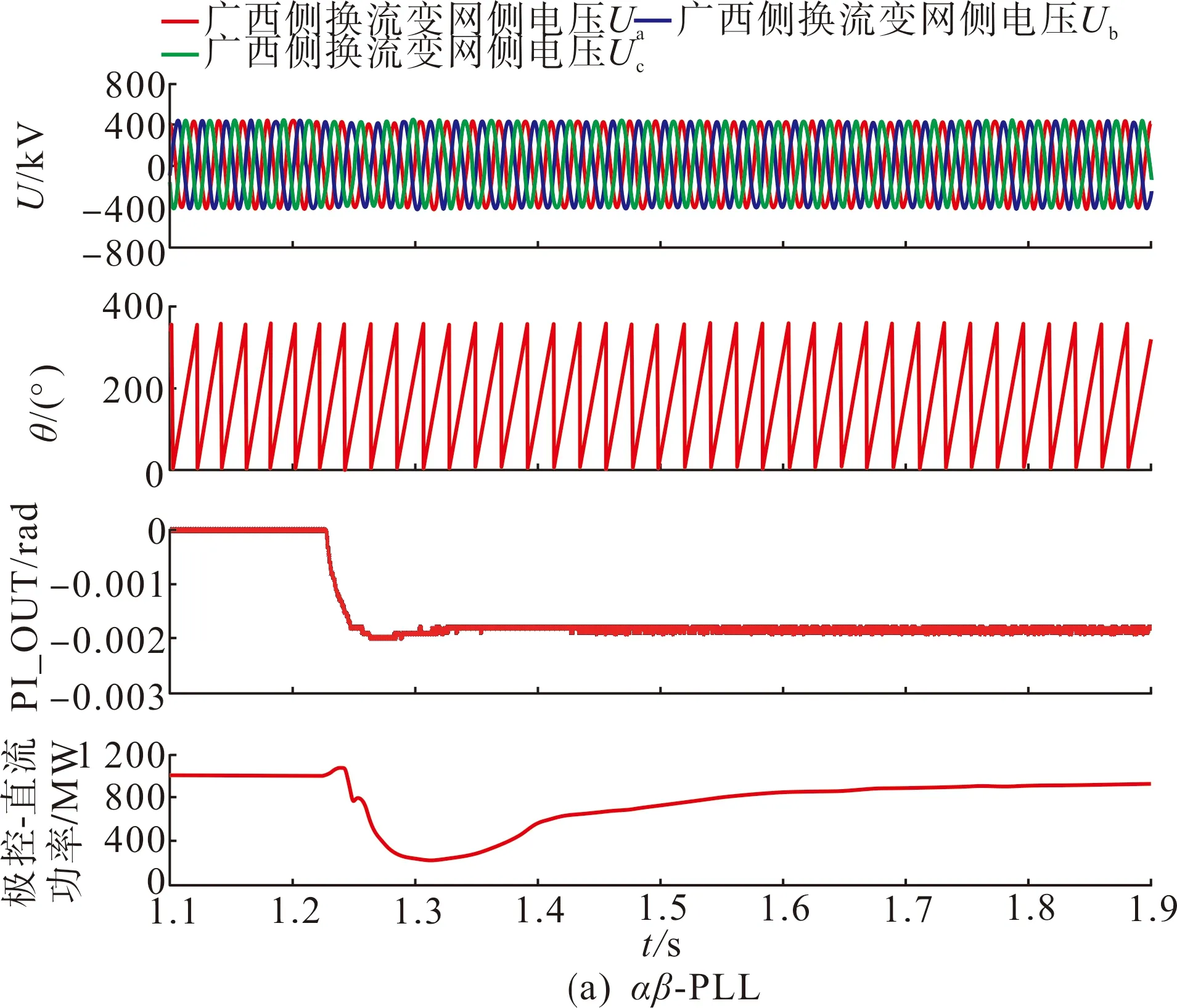

4.5 單相交流故障測試

在滿功率運行時,在RTDS中設置廣西側交流A相跌落60%,測試波形如圖11所示。

圖11 交流電壓單相接地故障時測試波形Fig.11 Test waveforms during AC-voltage single phase ground fault

圖中可見,在單相交流故障期間傳統αβ-PLL的PI輸出有較明顯的二倍頻波動;Single-PLL同MDSC-PLL僅在故障開始及恢復瞬間快速調節,無振蕩。

單相交流故障期間,采用傳統αβ-PLL鎖相環時,發生長時間換相失敗,直流功率因此大幅波動;而采用新型Single-PLL及MDSC-PLL鎖相環時,僅在故障開始瞬間發生短時間換相失敗,直流功率相對平穩。

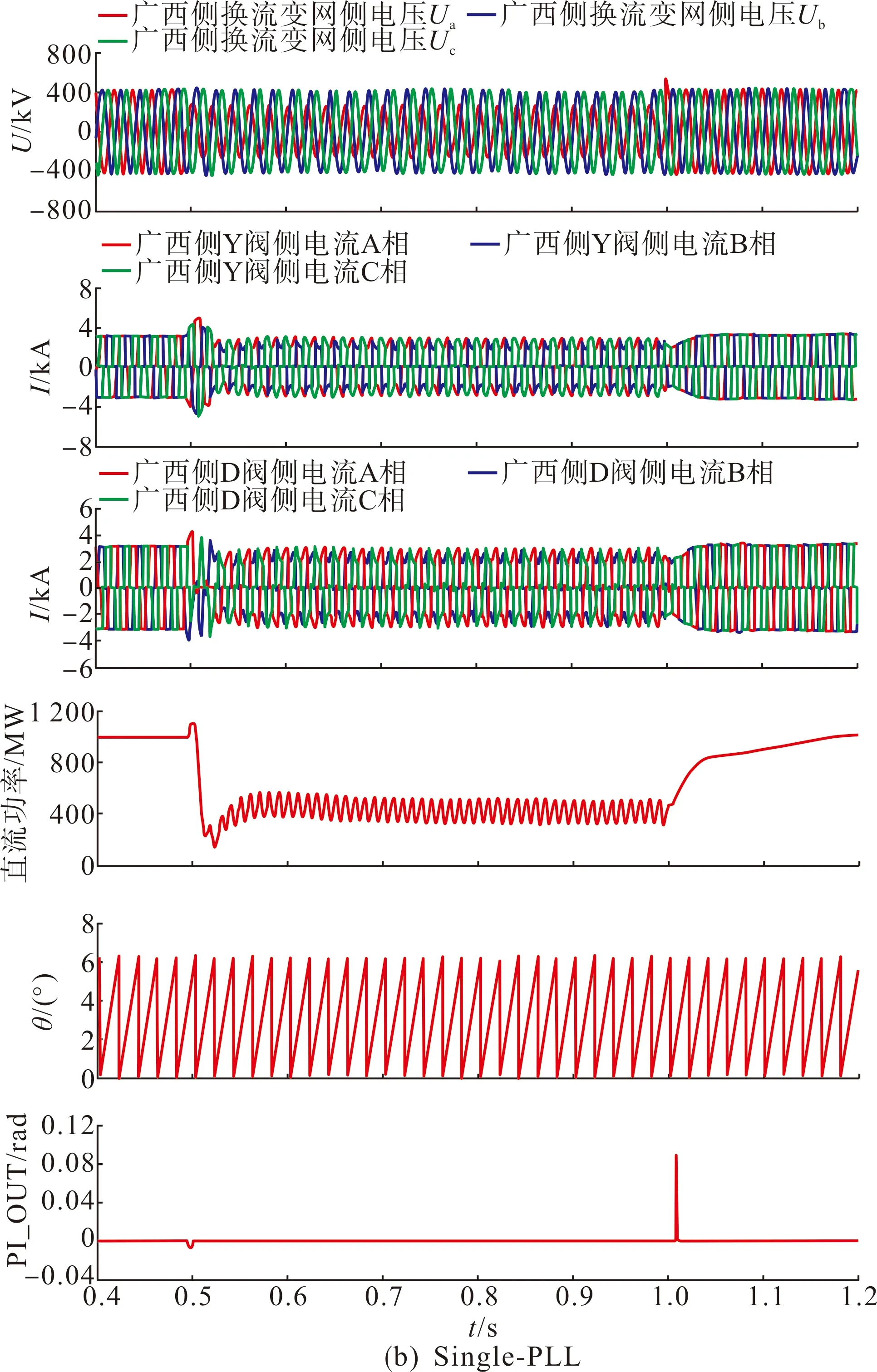

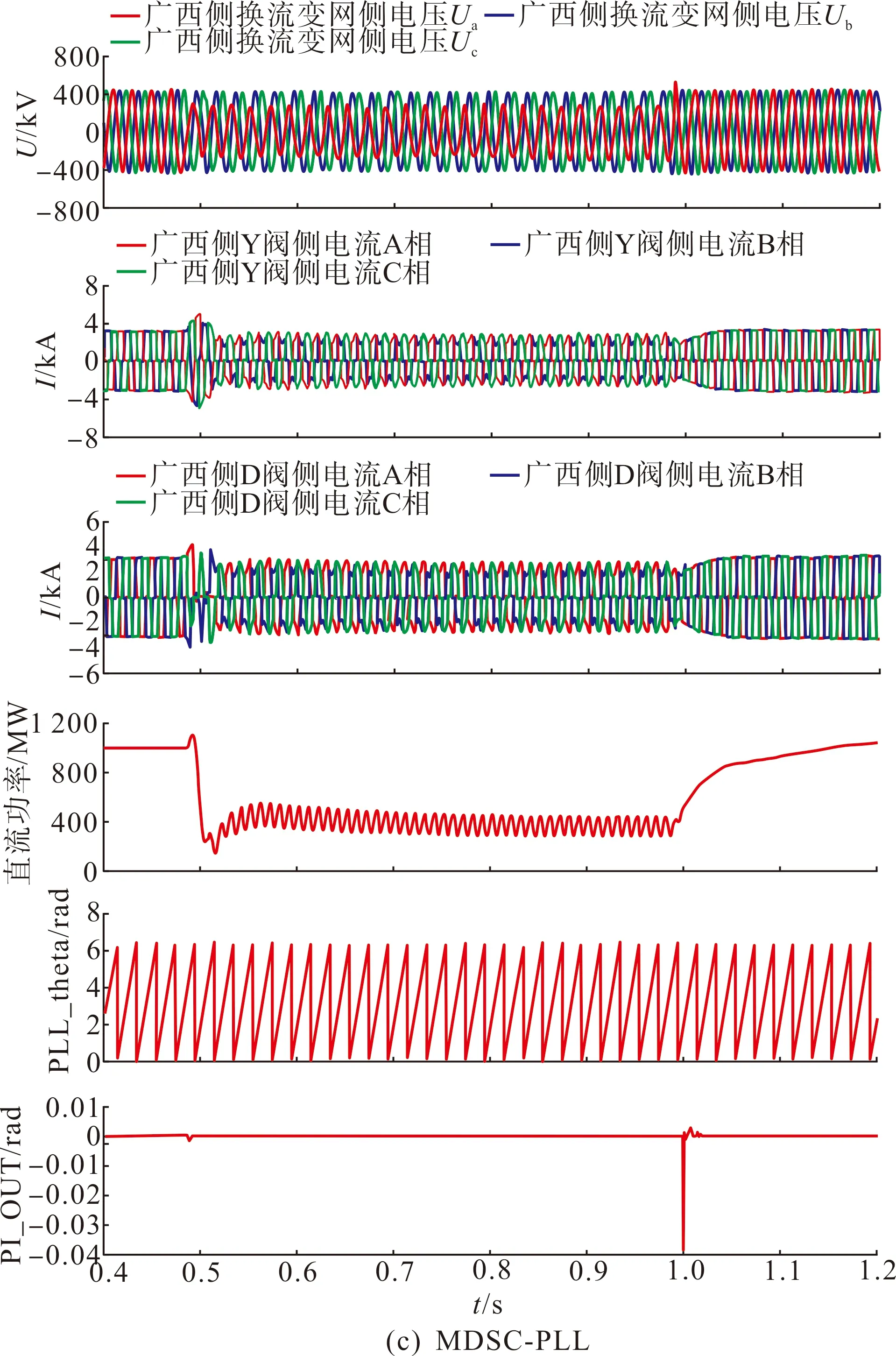

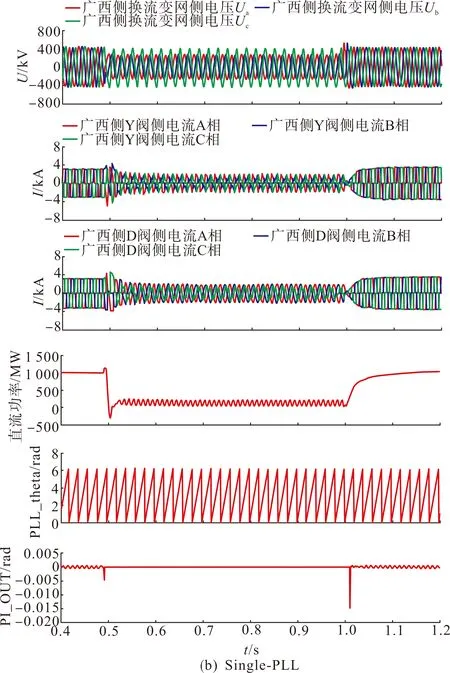

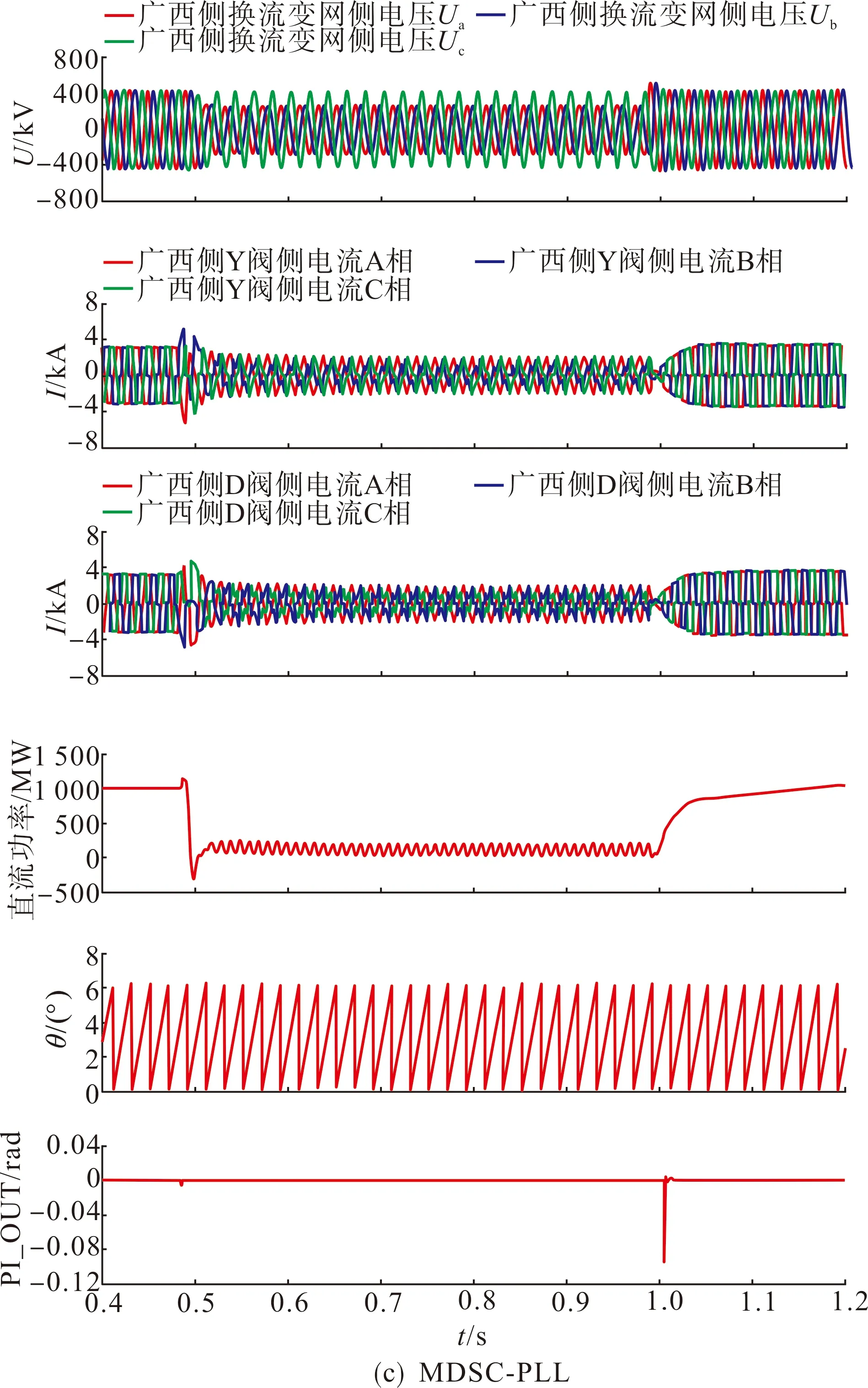

4.6 兩相交流故障測試

在滿功率運行時,在RTDS中設置廣西側交流兩相跌落60%,測試波形如圖12所示。

圖12 交流電壓兩相接地故障時測試波形Fig.12 Test waveforms during AC-voltage two phase ground fault

圖中可見,故障期間傳統αβ-PLL的PI輸出有較明顯的二倍頻波動;Single-PLL同MDSC-PLL僅在故障開始及恢復瞬間快速調節,無振蕩。

兩相交流故障期間,采用傳統αβ-PLL鎖相環時,發生長時間換相失敗;而采用新型Single-PLL及MDSC-PLL鎖相環時,僅在故障開始瞬間發生短時間換相失敗。

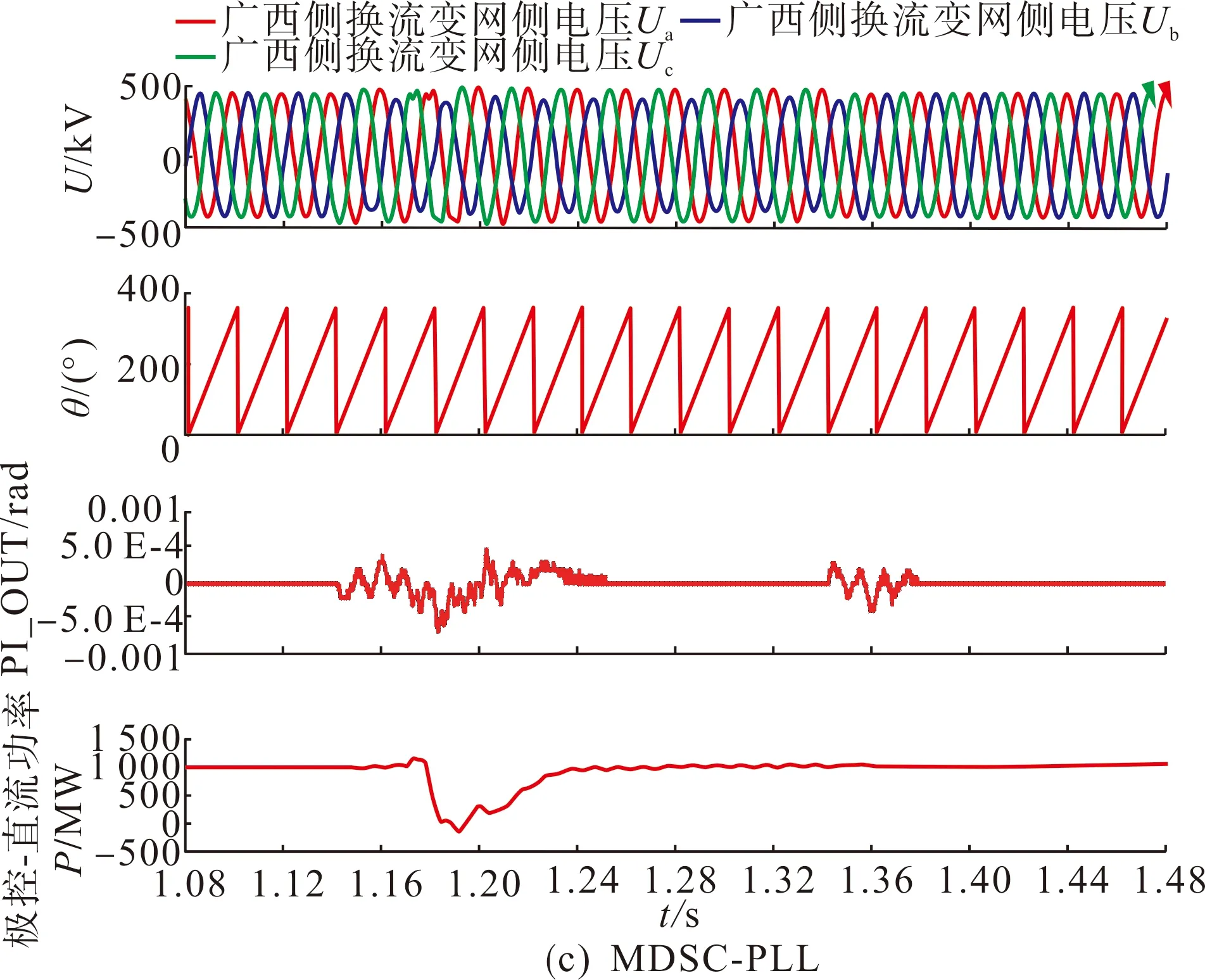

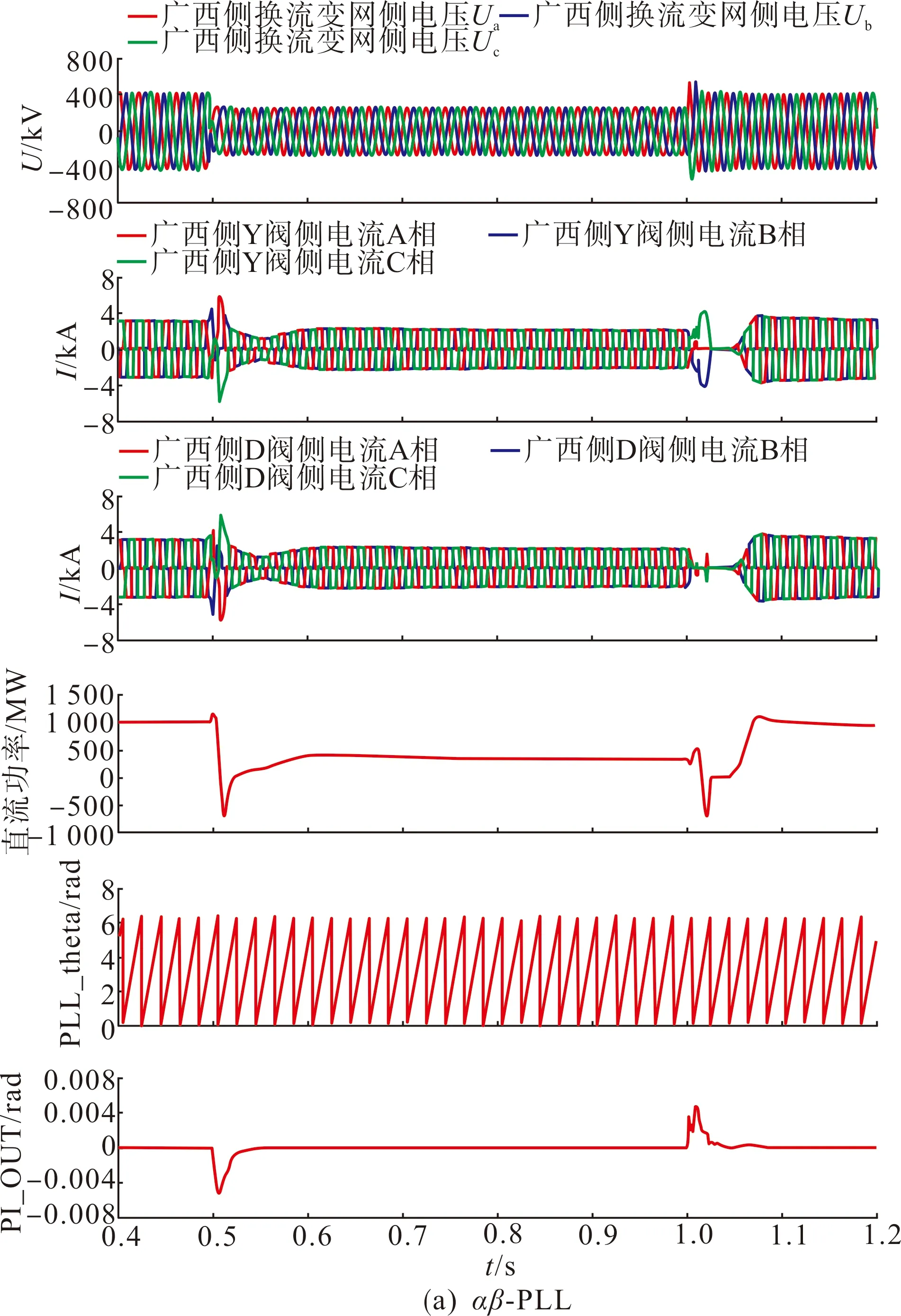

4.7 三相交流故障測試

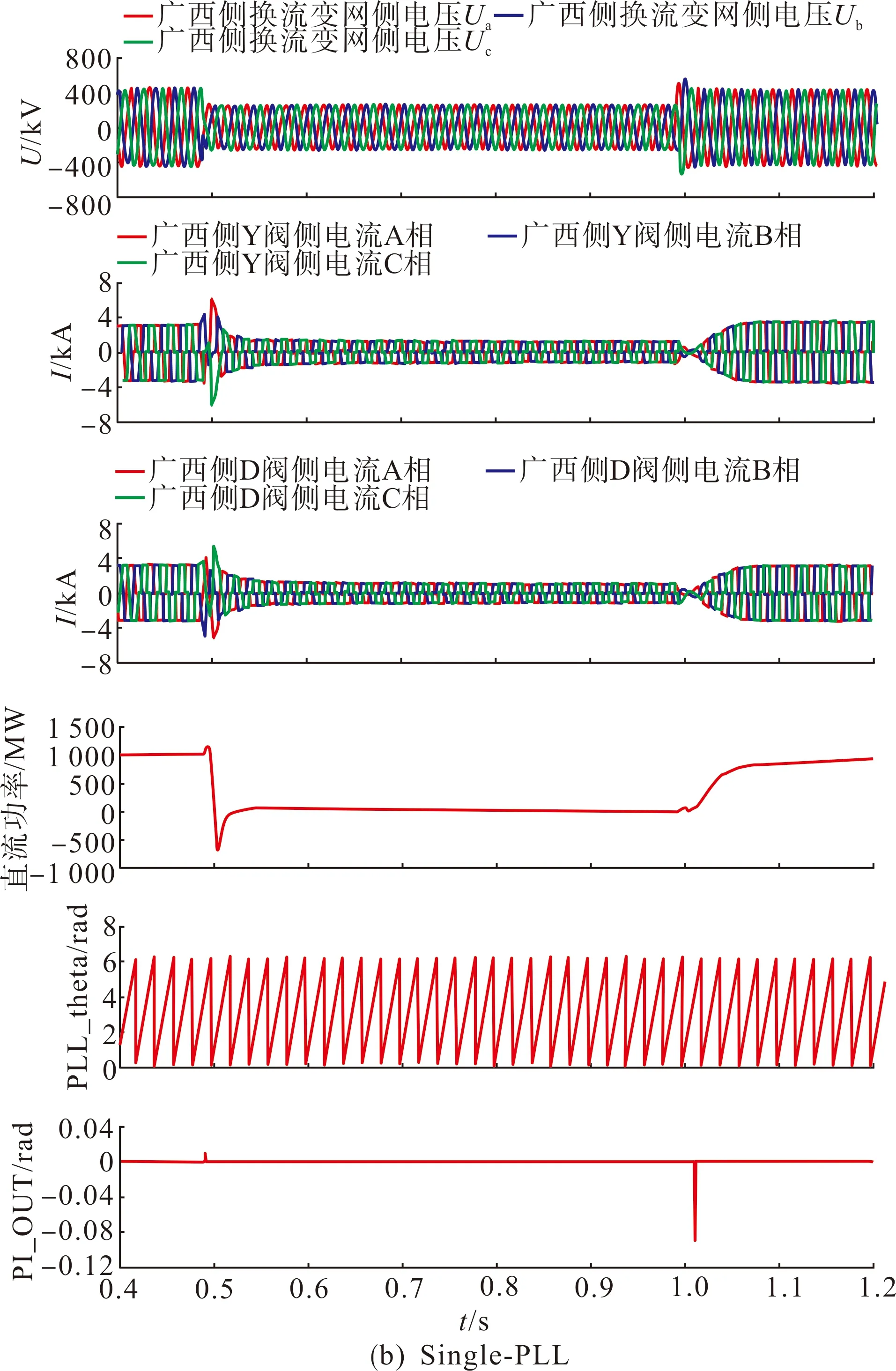

在滿功率運行時,在RTDS中設置廣西側交流三相跌落60%,測試波形如圖13所示。

圖13 交流電壓三相接地故障時測試波形Fig.13 Test waveforms during AC-voltage three phase ground fault

圖中可見,在三相對稱交流故障期間3種鎖相環均快速調節,但傳統αβ-PLL調節速度較慢。

采用傳統αβ-PLL鎖相環時,在故障開始及故障恢復時均發生換相失敗;而采用新型Single-PLL及MDSC-PLL鎖相環時,僅在故障開始時發生短時間換相失敗。受換相失敗影響,采用傳統鎖相環時,故障恢復瞬間直流功率再次發生大幅跌落。

4.8 三種鎖相環綜合對比分析

根據前述理論分析及RTDS測試結果,可得出如下結論。

1)交流電壓相位階躍,3種鎖相環響應時間相近,階躍后系統有功功率恢復速度相近;

2)抗諧波性能方面,3種鎖相環均具有一定的抗諧波干擾能力,新型MDSC鎖相環抗諧波能力最強,傳統鎖相環抗諧波干擾能力最差;

3)抗負序性能方面,新型MDSC鎖相環和新型單相鎖相環的抗負序能力均強于傳統鎖相環;

4)頻率適應性方面,新型單相鎖相環的頻率適應性較差,傳統鎖相環和新型MDSC鎖相環的頻率適應性較好;

5)交流故障期間,新型單相鎖相環和新型MDSC鎖相環的鎖相準確性更高,且能明顯減小故障期間的換相失敗次數。

由此可見,傳統鎖相環在交流系統諧波、交流故障等工況下,跟蹤相位能力較差,應用于實際工程時,需考慮增加其抗諧波干擾能力及應對交流故障處理;基于SOGI-QSG的新型單相鎖相環在高壓直流輸電中可與分相觸發控制結合,提升高壓直流輸電系統的抗諧波及抗負序能力、減少換相失敗的發生,但其頻率適應性較差,實際應用時可考慮工程實際情況增加頻率適應環節;基于MDSC的新型三相鎖相環各方面性能優異,適宜在實際工程推廣應用。

5 結語

本文分析了傳統αβ鎖相環、基于SOGI-QSG的單相鎖相環、采用MDSC的新型三相鎖相環的工作原理及優缺點,將其應用于高壓直流輸電控制系統中,并在傳統高壓直流輸電系統的RTDS硬件閉環測試平臺上,橫向對比測試了交流電壓出現常見故障時3種鎖相環的響應特性,分析了各個鎖相環的優缺點。認為傳統αβ鎖相環跟蹤相位能力較差,基于SOGI-QSG的單相鎖相環的頻率適應性較差,而采用MDSC的新型三相鎖相環各方面性能優異。本文結論可為后續工程選擇適宜的鎖相環提供理論及試驗依據。