MSK調制直接射頻合成算法的設計與FPGA實現

四川九洲電器集團有限責任公司 朱愛紅 楊偉軍 程 旗 汪小林 何 敏

根據軟件無線電發射電路的信號處理要求,提出了一種MSK調制直接射頻合成算法。在FPGA實現方面,提出了DDS直接數字合成器和分布式單端口RAM查表兩種實現方式,并在以FPGA及DAC為關鍵器件的硬件平臺上進行了驗證。電子設計自動化(Electronic Design Automatic,EDA)工具的綜合與實現結果表明,兩種方式各有優缺點,適用于不同的場景。

近年來隨著軟件可配置、可編程芯片的成熟應用,問世了多款高性能集成芯片,其中包括有力推動發射電路很大程度上接近理想軟件無線電架構的核心器件,例如高采樣低功耗的射頻DAC集成芯片以及高速超大容量高互聯帶寬的FPGA芯片。

FPGA+DAC的硬件架構可實現發射通道的主要功能,包括數字直接射頻合成、數字濾波以及數模轉換。數字直接射頻合成是是一種同時進行數字基帶信號產生和數字上變頻的聯合信號處理算法,不同于過去數字基帶調制和數字混頻功能分開處理,當前工程應用越來越趨向于將這兩種功能進行融合處理。

MSK調制是FSK調制的改進。FSK信號的兩種碼元波形沒有嚴格正交,傳輸時包絡會出現起伏,誤碼率性能較差。MSK信號則是一種包絡恒定、相位連續、帶寬最小且嚴格正交的FSK信號。因此,MSK調制方式具有功率譜密度較集中,頻帶利用率高等優點。

1 算法設計與實現

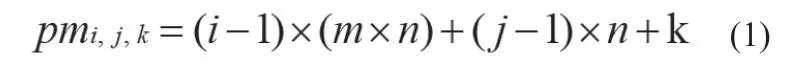

MSK調制直接射頻合成算法是在發射調制框架內按照模數轉換頻率依次輸出q×m×n個MSK數字基帶調制信號,q為發射調制框架內輸入符號個數,m為每個符號采樣點個數,n為MSK基帶調制信號路數,每路基帶調制信號的初始相位不同。在發射調制框架內先發送第1個輸入符號的第1個采樣的第1路調制基帶信號,最后發送第q個輸入符號的第m個采樣的第n路調制基帶信號,第i個輸入符號的第j個采樣的第k路調制基帶信號在發射調制框架內的位置pmi,j,k的計算公式如式(1)所示:

其中,i=1,2,…,q;j=1,2,…,m;k=1,2,…,n。

1.1 算法設計仿真

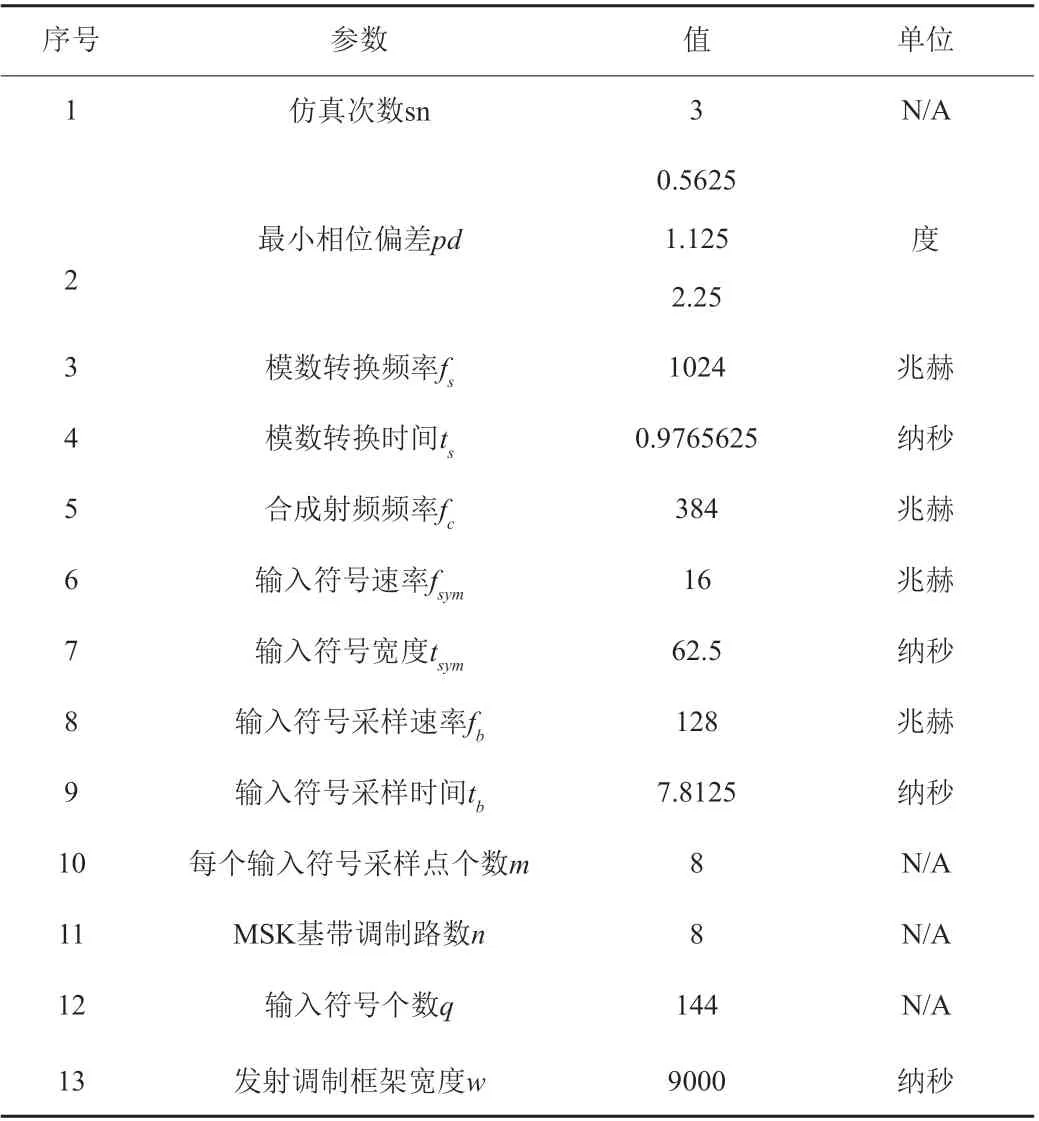

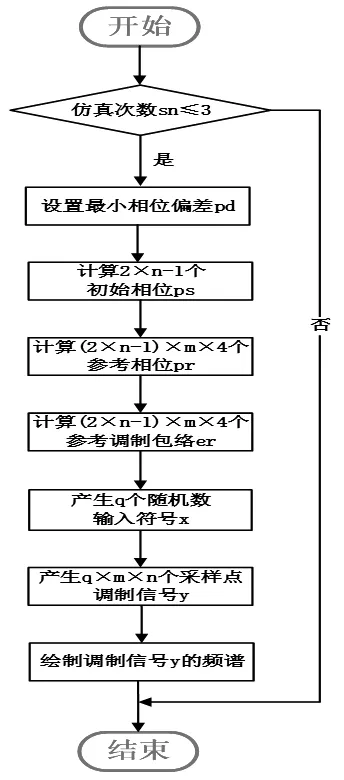

使用Matlab軟件進行算法的設計仿真,基本參數設定如表1所示,流程圖如圖1所示。

表1 設計仿真程序基本參數

圖1 設計仿真程序流程圖

1.1.1 設置最小相位偏差pd

三次仿真,pd分別設置為0.5625°、1.125°及2.25°。

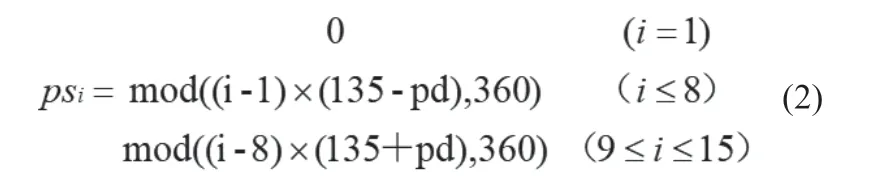

1.1.2 計算2×n-1個初始相位ps

當n為8時,15個ps(單位度)計算公式如式(2)所示:

式中,mod()為求模運算;i=1,2,…,15。

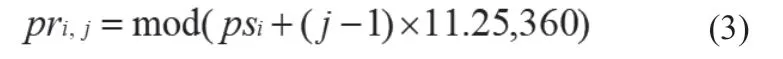

1.1.3 計算(2×n-1)×m×4個參考相位pr

當n為8且m為8時,15×32個pr(單位度)計算公式如式(3)所示:

式中,mod()為求模運算;i=1,2,…,15;j=1,2,…,32。

1.1.4 計算(2×n-1)×m×4個參考調制包絡er

當n為8且m為8時,15×32個er計算公式如式(4)所示:

式中,sin()為求正弦值運算;i=1,2,…,15;j=1,2,…,32。

1.1.5 產生q個隨機數輸入符號x

調用Matlab函數randi產生q個正態分布隨機數整數數組,該數組作為輸入符號x,數組元素取值0或1。

1.1.6 產生q×m×n個采樣點調制信號y

MSK數字基帶調制是使用差分或非差分編碼最小頻移鍵控調制方法輸出消息信號(即輸入符號)的復數包絡。本算法采用差分編碼最小頻移鍵控調制方法,調制包絡y為適應硬件平臺的DAC芯片進行了簡化,只取復數包絡的虛部。

(1)差分編碼最小頻移動鍵控調制

差分編碼最小頻移鍵控調制規則如下:

a.每個符號的調制相位累加值都等于90°

b.所有采樣點的調制相位是連續變化的;

c.每個采樣點的調制相位變化量等于90°/m,例如,本算法m為8,每個采樣點的調制相位變化量為11.25°;

d.輸入符號為‘1’,當前采樣點的調制相位在前一采樣點的調制相位基礎上累減11.25°;

e.輸入符號為‘0’,當前采樣點的調制相位在前一采樣點的調制相位基礎上累加11.25°。

(2)調制信號y的計算方法

當q為144且m為8且n為8時,調制信號y是9216個采樣點復數包絡虛部。采樣點復數包絡虛部的計算方法如下:

a.計算參考調制包絡er行地址ar;

b.計算參考調制包絡er列地址ac;

c.參考調制包絡er中行地址ar列地址ac所對應的的元素取值即為該采樣點復數包絡虛部。

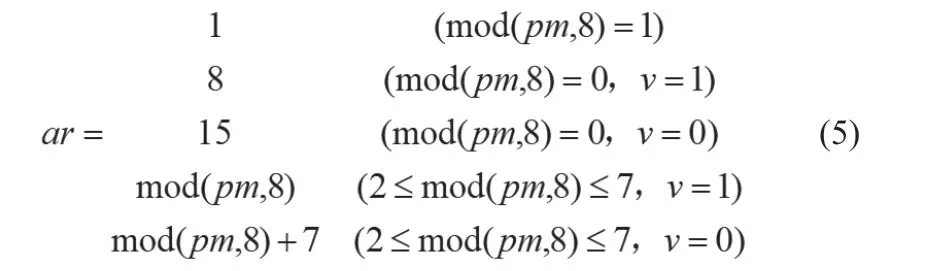

(3)參考調制包絡行地址ar的計算方法

ar為大于0且小于16的整數,由采樣點在發射調制框架中的位置pm以及該位置對應輸入符號取值v確定,計算公式如式(5):

式中,mod()為求模運算;pm為大于0且小于9217的整數。

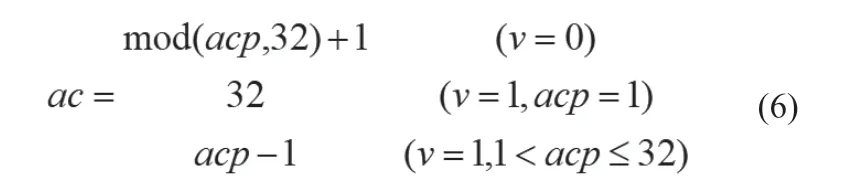

(4)參考調制包絡行地址ac的計算方法

ac為大于0且小于33的整數,第1個采樣點的ac取值等于1,其余采樣點ac取值由前一采樣點參考調制包絡列地址acp以及該采樣點在發射調制框架中的位置pm對應的輸入符號取值v確定,計算公式如式(6):

式中,mod()為求模運算;pm為大于0且小于9217的整數;

acp為大于0且小于33的整數。

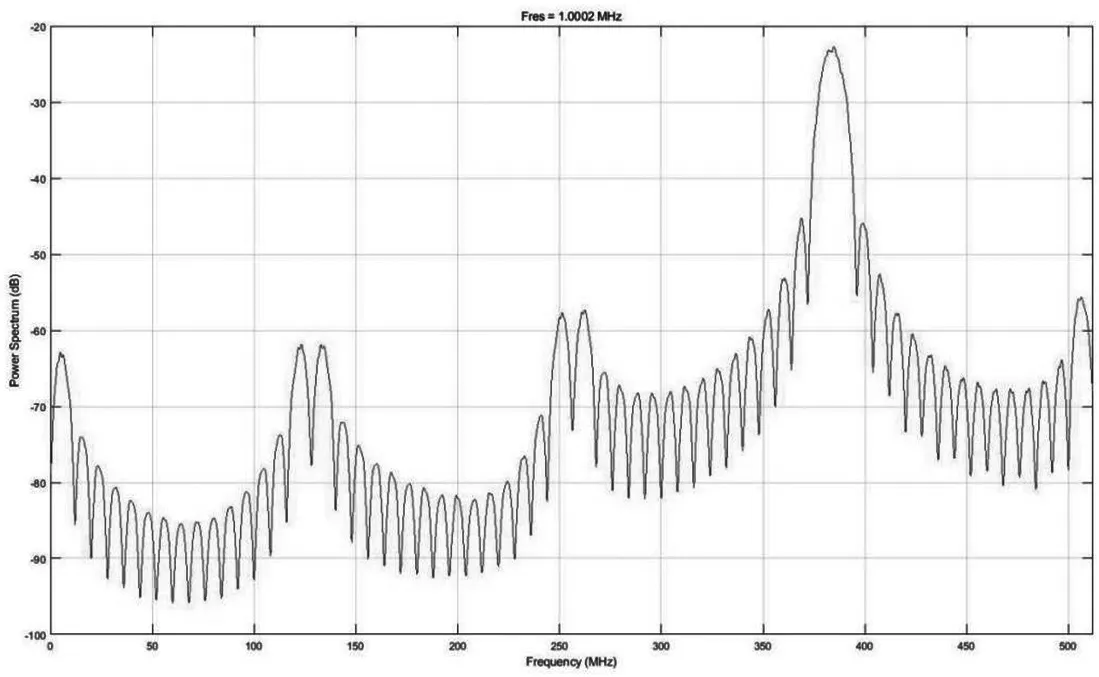

1.1.7 繪制調制信號y的頻譜

調用Matlab函數 pspectrum()繪制三種調制信號y的頻譜,如圖2~4:

圖2 Pd=0.5625°調制信號頻譜

圖3 Pd=1.125°調制信號頻譜

圖4 Pd=2.25°調制信號頻譜

最小相位偏差Pd對主瓣幅度沒有影響,但會影響第一、第二旁瓣幅度,當取值0.5625°及2.25°時,第一、第二旁瓣幅度比主瓣幅度低36dB左右,當取值1.125°時,第一、第二旁瓣幅度比主瓣幅度低46dB左右,因此最小相位偏差Pd的較優取值為1.125°,在FPGA實現中Pd取值設置為1.125°。

1.2 算法FPGA實現

使用vivado軟件進行FPGA算法設計、仿真、綜合、布局布線并產生位流文件后進行在線加載調試。

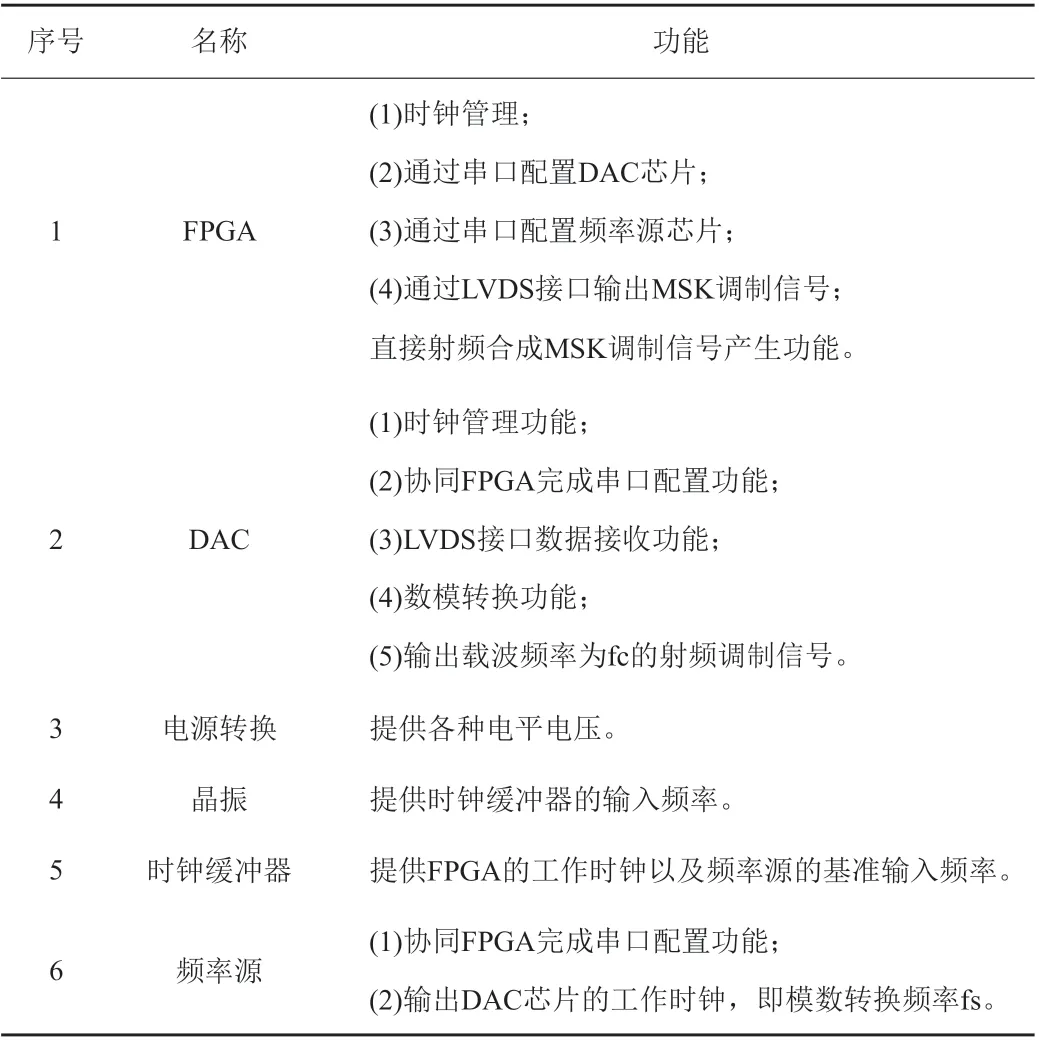

硬件平臺采用5V直流電壓供電,由FPGA、DAC、電源轉換、晶振、時鐘緩沖器以及頻率源等芯片組成,芯片功能如表2所示。

表2 硬件平臺芯片功能

表2列出的FPGA的前四項功能是為了在硬件平臺驗證MSK調制直接射頻合成算法的附加功能,本論文不做描述。實際工程實踐中,利用FPGA實現直接射頻合成MSK調制信號產生功能通常有兩種算法,一種是DDS直接數字合成器算法,另一種是分布式單端口RAM查表算法。

1.2.1 DDS直接數字合成器算法

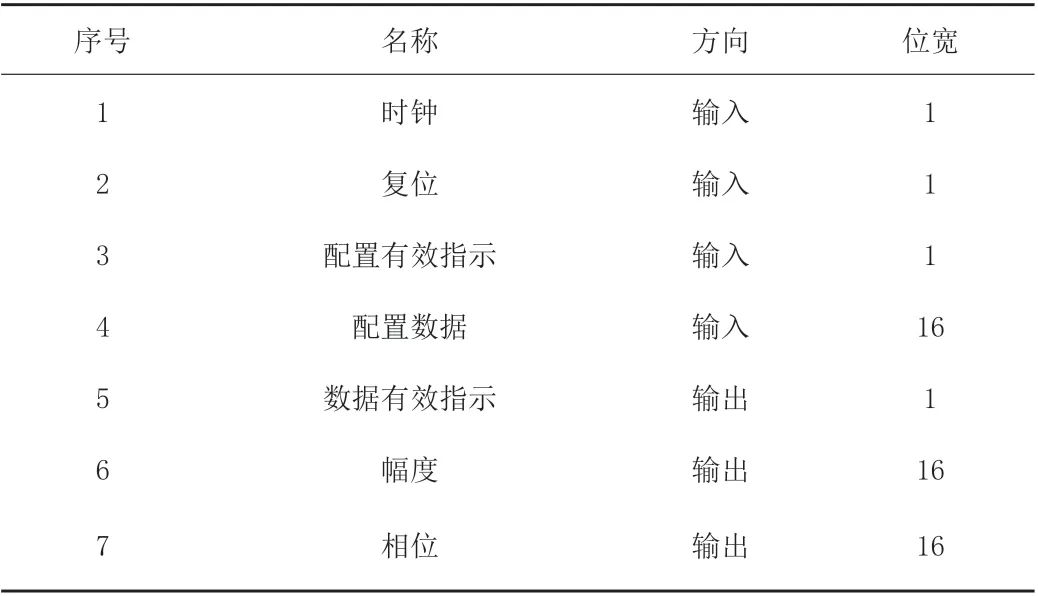

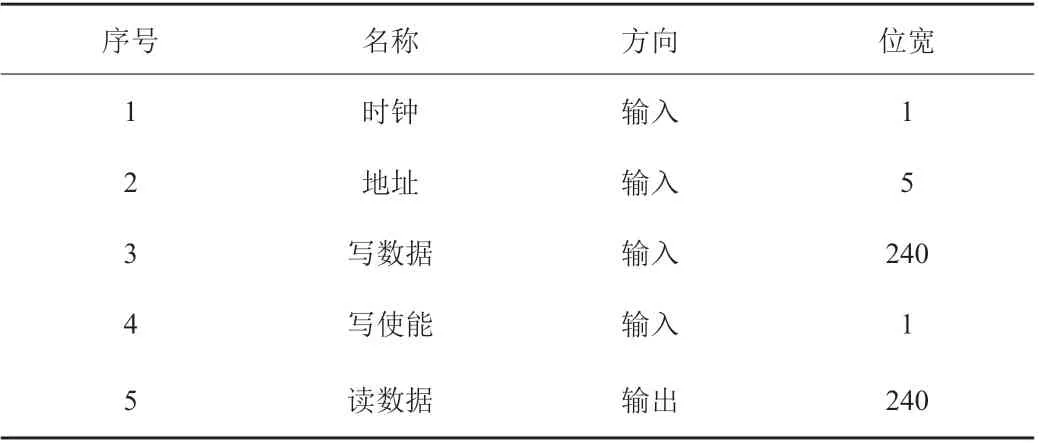

核心部件是DDS直接數字合成器(簡稱DDS),一種由FPGA廠家提供的數字信號處理調制類IP核。DDS由相位發生器和正弦/余弦查找表兩部分組成,兩部分可獨立或聯合使用。DDS配置參數如表3所示,輸入輸出端口如表4所示。

表3 DDS配置參數

表4 DDS DDS輸入輸出端口

MSK基帶調制路數n為8,因此需要例化8個DDS核。

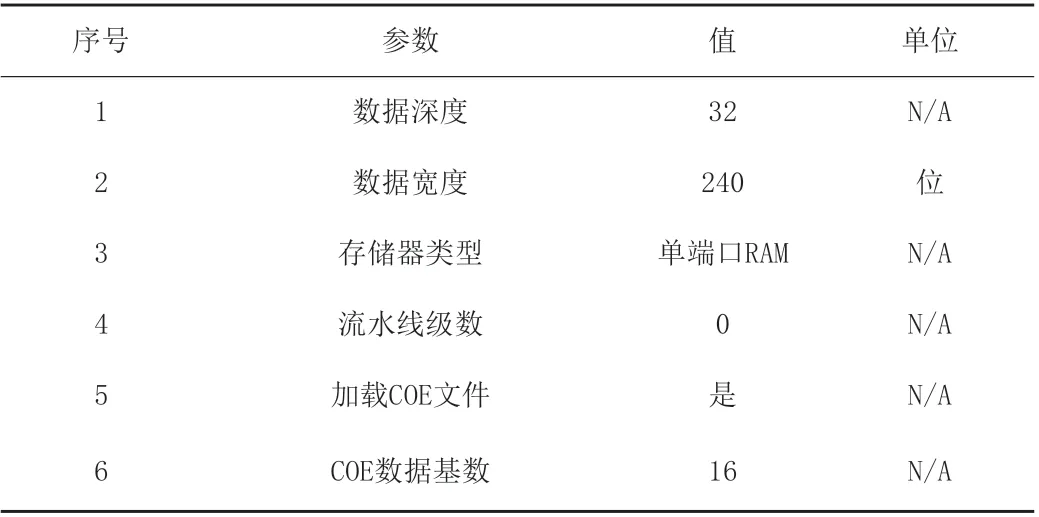

1.2.2 分布式單端口RAM查表算法

分布式單端口RAM算法(以下簡稱查表法)的核心部件是分布式單端口RAM,一種由FPGA廠家提供的存儲類IP核。分布式單端口RAM配置參數如表5所示,輸入輸出如表6所示,加載COE文件是預先將參考調制包絡er數據轉換為32行240位格式化數據獲得。

表5 分布式單端口RAM配置參數

表6 分布式單端口RAM輸入輸出端口

2 性能分析

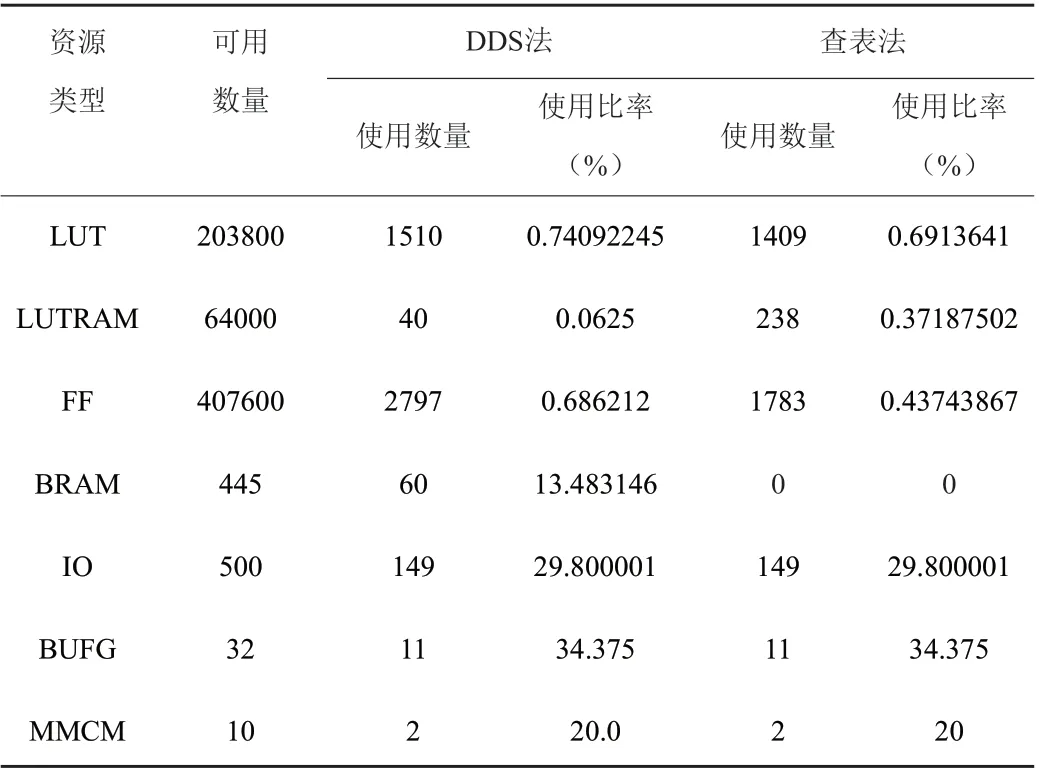

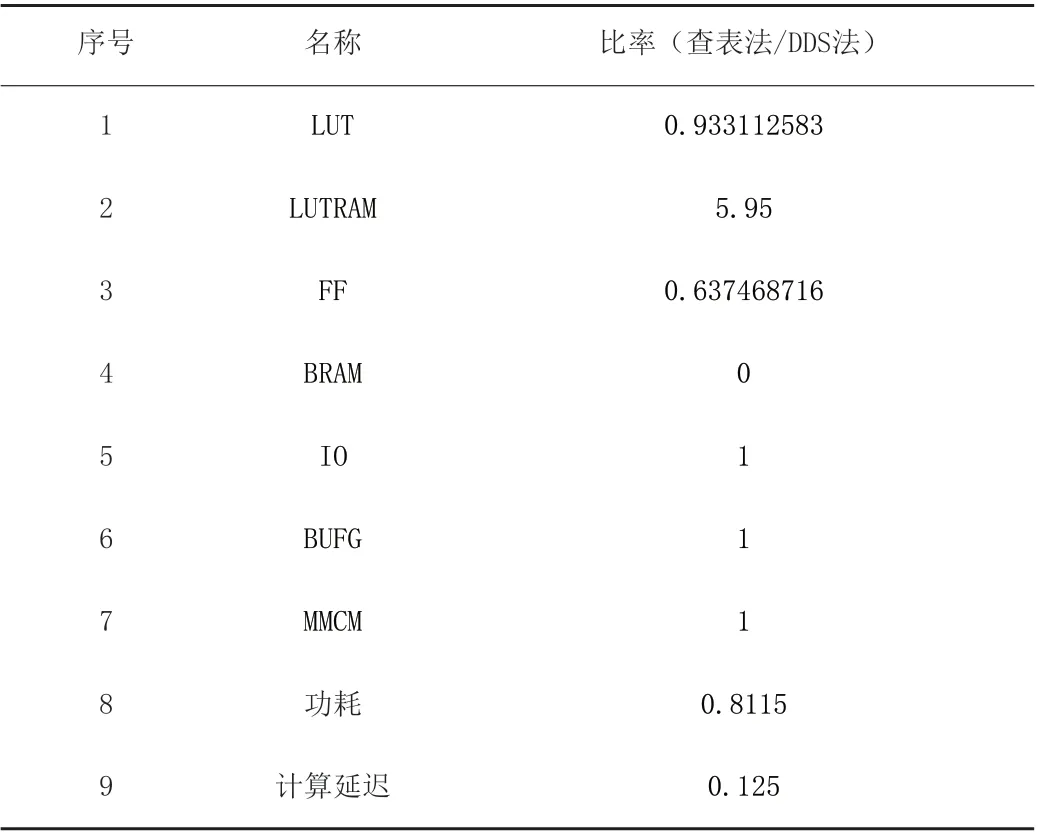

利用vivado軟件分別實現了DDS法和查表法兩種算法。預估功耗方面,查表法為0.934W,DDS法為1.151W;計算延遲方面,查表法1個時鐘,DDS法8個時鐘;兩種算法資源消耗情況如表7所示,兩種算法的資源消耗、功率消耗及計算延遲比率如表8所示。

表7 算法的資源消耗情況

表8 算法數據分析表

兩種算法的IO、BUFG及MMCM等資源消耗完全相同,查表法除了LUTRAM資源消耗明顯增多之外,LUT、FF及BRAM等資源消耗都比DDS法要少,尤其是BRAM的資源消耗等于零。另外,查表法的功耗更低。總體而言,查表法不僅總體資源消耗優于DDS法而且延遲比DDS法顯著減小;DDS法主要優勢是可復用及可擴展,支持多種調制方式。

綜上所述,DDS法適合調制方式較多的時分復用應用系統,而查表法適合高實時性、低功耗統且主要調制方式為MSK的應用系系統。