淺析CMOS圖像傳感器晶圓級封裝技術

馬書英,王 姣,劉 軼,鄭鳳霞,劉玉蓉,肖智軼

(華天科技(昆山)電子有限公司,江蘇昆山215300)

1 引言

2000年夏普推出第一款可拍照的手機,經過二十多年的發展,手機已成為人們日常生活中必不可少的工具,其中攝像是智能手機的核心功能之一,各大手機廠商均把拍攝性能作為產品的關鍵競爭指標。手機攝像頭的演變也日新月異,最初的手機是單個攝像頭,但是由于智能手機攝像頭尺寸較小,單個CMOS(Complementary Metal Oxide Semiconductor)圖像傳感器(CMOS Image Sensor,CIS)感光性能有限,為了呈現更好的拍照效果,將原先集成在一個攝像頭上的多種功能分解成多個單一功能攝像頭,如廣角、長焦、微距等,促使了后置雙攝、前置雙攝,再到3D感應模組、后置三攝、四攝、五攝等多攝視覺解決方案的出現。多攝像頭的出現在提升圖像質量的同時,促進了圖像傳感器市場規模穩步提升[1]。2019年,全球智能手機圖像傳感器出貨量超過47億顆,同比增長15%。2020年華為推出的P40 Pro+型號手機,攝像頭多達7個,這表明未來智能手機攝像頭市場仍然會保持穩步增長。

與此同時,隨著無人駕駛的興起,CIS在汽車攝像頭市場也得到了迅猛的發展。先進輔助駕駛系統(Advanced Driving Assistance System,ADAS)的普及導致每輛汽車至少有8個攝像頭,包含后視攝像、全方位視圖系統、攝像機監控系統等[2-6]。據Yole統計,2016—2018年全球車載CIS市場規模分別是5.4億美元、6.6億美元、8.7億美元,預計2023年達到32億美元,年復合增長率高達29.7%,汽車將會成為僅次于手機的第二大CIS應用領域。其他新的應用,如安防、無人機、機器人、虛擬現實、增強現實等,也將給全球CMOS市場的增長提供動力[7-8]。

圖像傳感器主要生產商有索尼、三星、豪威、安森美、格科微、海力士、思特威等,排名第一的是索尼,市場份額高達53%;排名第二的是三星電子,市場份額為18%;第三是豪威科技,市場份額為11%;第四是安森美半導體,市場份額為4%。四大生產商占據全球85%的市場。國內企業格科微在低端市場(像素小于16 M)優勢明顯,尤其是2 M、5 M等產品,市占率達到34%。思特威在安防監控攝像頭和車載攝像頭領域持續發力,相繼推出多款產品,市場反響良好,發展勢頭迅猛。

在CIS產業規模日益擴大的背景下,本文介紹了CIS的主要結構,回顧了CIS的封裝技術演變,并根據結構和應用領域的差異詳細介紹了基于硅通孔(Through Silicon Via,TSV)技術的多種CIS晶圓級封裝技術,指出了CIS晶圓級封裝技術的發展趨勢。

2 CIS結構

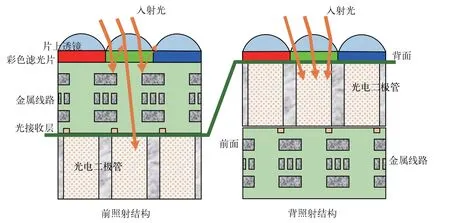

目前CIS可以分為三種結構,前照式(Front Side Illuminated,FSI),背照式(Back Side Illuminated,BSI),堆棧式(Stack)及在Stack基礎上演變的Triple Stack,如圖1所示。

圖1 CIS結構

一般的CIS像素都由以下幾部分構成:片上透鏡(Micro Lenses)、彩色濾光片(On-Chip Color Filters)、金屬排線、光電二極管以及基板。傳統的CIS是圖1中的“FSI”結構,當光線射入像素,經過了片上透鏡和彩色濾光片后,先通過金屬排線層,最后光線才被光電二極管接收。金屬是不透光的,而且還會反光。所以,在金屬排線這層光線就會被部分阻擋和反射掉,光電二極管吸收的光線就只有剛進來的70%或更少;而且反射還有可能串擾旁邊的像素,導致顏色失真。目前中低檔的CIS排線層所用的金屬是比較廉價的鋁,鋁對整個可見光波段(380~780 nm)基本保持90%左右的反射率。這樣一來,背照式CIS就應運而生了,其金屬排線層和光電二極管的位置和“FSI”正好顛倒,光線幾乎沒有阻擋和干擾地進入光電二極管,光線利用率極高,所以背照式CIS能更好地利用射入的光線,在低照度環境下成像質量也就更好,見圖2[9]。

圖2 FSI和BSI圖像傳感器

BSI感光單元的基板上不全是受光區,還有相當大的面積是電路板。如果能移除電路板,受光區域就會明顯增大,于是新的設計就是將電路板放到受光區下面,形成堆疊的結構,這種設計叫堆棧式(Stacked),堆棧式CIS見圖3[10]。它可以顯著增加每個單元的受光面積,面積越大,受光也就越多,代表輸入信號也越強。但商家更樂意將這種技術用到提高像素方面,因為即便縮小感光單元,受光面積依然可以保持不變,意味著畫質不會下降,同樣規格的感光器上可以放置更多的感光單元,從而提高像素密度和總像素數量,第一顆堆棧式感光器的總像素達到了1300萬,而畫質也有了顯著的提升。從結構上說,堆棧式應該屬于背照式的一種。

圖3 堆棧式CIS

3 CIS封裝技術演變

CIS封裝最初采用的是帶有玻璃蓋板的陶瓷封裝,例如Amkor公司的VisionPak就是一種陶瓷無鉛芯片載體。這種方案比較昂貴而且會占用很大的相機內空間。20世紀末晶圓級封裝(Wafer Level Package,WLP)技術逐步發展起來,其優勢在于尺寸小、重量輕和成本低,并逐漸引起大家的關注。2007年3月,日本Toshiba公司首次展出采用硅通孔(Through Silicon Via,TSV)技術的WLP小型圖形傳感器模組,該技術不僅提供用于模塊集成的完全密閉的器件,使由污染顆粒所導致的CIS成品率損失大大降低,還具有當時業界最小尺寸和質量、有效降低寄生效應、改善芯片運行速度和降低功耗等優點[11-12]。如今全球只有臺灣積體電路制造股份有限公司(臺積電)下屬公司精材科技、華天科技(昆山)電子有限公司、晶方科技、科陽光電4家OSAT(Outsourced Semiconductor Assembly and Testing)可以提供圖像傳感器WLP解決方案,其中華天科技(昆山)和晶方科技能夠提供12英寸圖像傳感器WLP服務。表1列舉了全球CIS各環節主要供應商。

表1 CIS各環節主要廠商

4 CIS WLP技術

CIS根據其結構和應用領域不同,采用的WLP結構也不同。華天科技(昆山)電子有限公司可以提供8英寸/12英寸基于TSV技術的全套圖像傳感器WLP技術,含激光打孔技術、平面停留技術、UT(Ultra Thin Process)半切技術和直孔技術。

4.1 激光鉆孔技術

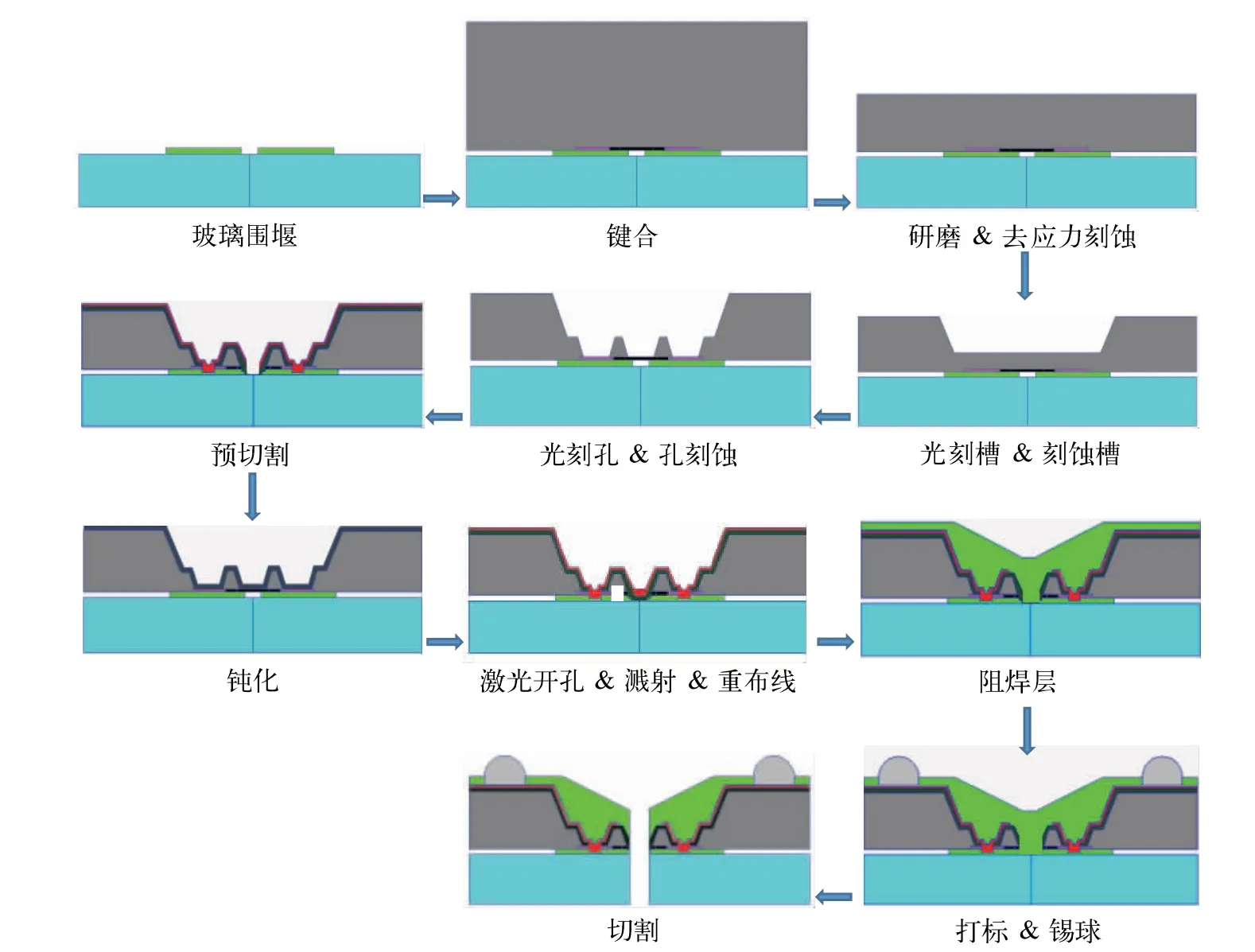

激光鉆孔技術主要應用于消費類圖像傳感器封裝,封裝工藝流程如圖4所示,先采用光刻膠在光玻璃上制作圍堰,空腔大小根據芯片傳感器區域確定,再通過晶圓永久鍵合將來料預處理好的晶圓和帶圍堰玻璃進行鍵合。鍵合片通過機械研磨達到預設厚度,再通過干法蝕刻去除應力。通過涂布曝光顯影和干法刻蝕形成雙臺階通孔,雙臺階厚度配比根據客戶要求總厚度和金屬Pad Pitch來決定。為了增強芯片可靠性,通常采用預切割方式達到芯片包邊的效果,采用機械切割打開切割道,切入圍堰[13]。再通過噴涂工藝在硅基表面形成一層聚合物絕緣層,聚合物絕緣層不但能達到絕緣效果,同時還能形成側邊保護,阻礙水汽對芯片的侵蝕。采用激光打孔技術直接穿透絕緣層和金屬Pad,再濺射Ti/Cu種子層,通過電鍍和化學鍍工藝形成互聯線路,將Pad信號引到晶圓背面,為了保護線路在表面涂布一層阻焊層,光刻形成焊盤開口,再通過印刷工藝形成焊球,最終通過切割形成單顆封裝完成的芯片。圖5是激光鉆孔技術封裝成品的外觀圖和SEM圖。

圖4 激光鉆孔封裝工藝流程

圖5 激光鉆孔技術封裝成品外觀圖和SEM圖

4.2 平面停留技術

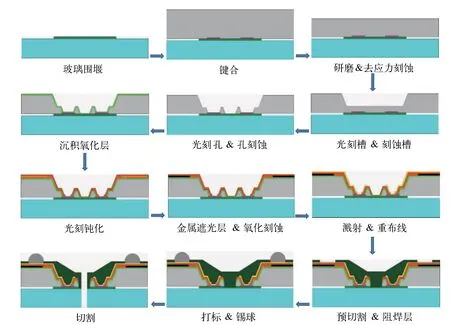

平面停留工藝和激光打孔工藝流程類似,主要應用于安防監控芯片和車載影像芯片,通過光刻使金屬重布線層(Redistribution Layer,RDL)和金屬Pad直接接觸連接,該連接方式接觸面積更大,可靠性更好,同時解決了部分BSI/Stack Wafer不能打孔的問題。平面停留工藝流程如圖6所示,涂布完絕緣光刻膠后通過光刻顯影去除金屬Pad上方的絕緣膠,再通過整面干法刻蝕方式去除Pad最表層的二氧化硅絕緣層從而暴露Pad,后續制程和激光打孔工藝類似[14-15]。圖7是平面停留技術封裝成品的外觀圖和SEM圖。

圖6 平面停留工藝封裝工藝流程

圖7 平面停留技術封裝成品的外觀圖和SEM圖

對比兩種封裝技術,激光打孔結構的流程相對簡單,成本更低,但要求來料晶圓的金屬Pad下方不能有線路或者其他功能設計,對晶圓制造工藝也有要求,功能層不能有Low-k材料,否則激光打孔會引起延裂,從而導致產品失效。由于RDL和金屬Pad是通過激光打出的孔形成環形接觸,可靠性表現不如平面停留工藝[16-17]。華天科技(昆山)電子有限公司采用平面停留工藝封裝的車載圖像傳感器芯片在國內率先通過汽車行業AEC-Q100認證。

4.3 UT半切技術

UT封裝技術主要適用于Pad間距較小(不大于110μm)且芯片Seal Ring在Pad內側的產品,其封裝流程如圖8所示。

圖8 UT半切封裝技術流程

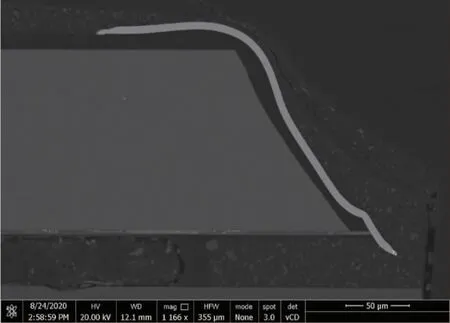

首先制備空腔玻璃,將空腔玻璃與晶圓正面鍵合。利用研磨工藝對背面減薄,通過干法蝕刻去除研磨產生的應力層并且對硅基進一步減薄。再采用光刻和刻蝕工藝去除Pad上方的硅基,并在表面覆蓋一層鈍化膠。然后采用半切技術利用高速旋轉的角度刀將Pad打開并切入鍵合膠層,之后進行重布線并制作引出端焊球,最終切割成單個封裝體。圖9為UT半切結構封裝后的SEM切片圖。UT封裝技術的優勢在于可以增加后續所做線路與Pad的接觸面積,同時Pad及金屬線路的尾端通過阻焊膠(Solder Mask Film,SEM)包邊,有效提升了產品可靠性。另外,UT封裝技術采用一步硅刻蝕后,再利用半切技術將Pad側面打開,可以減少Pad上方氧化層刻蝕工序,并且也避免了激光打孔對Pad損傷的風險,可以節約成本,減少制樣周期,增加產品的可靠性。

圖9 UT結構SEM切片圖

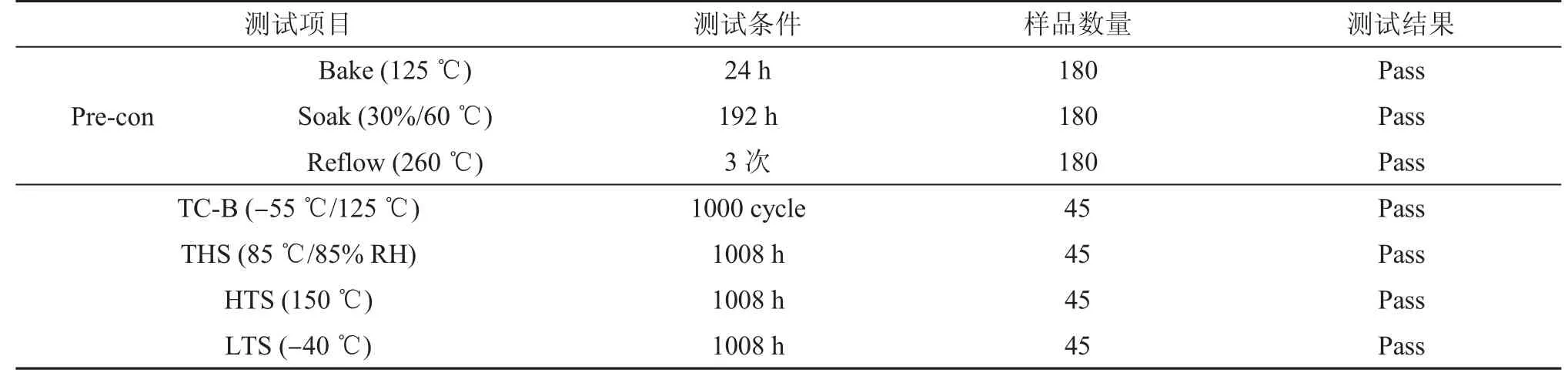

目前UT封裝技術主要應用于消費類、安防類等產品,且能滿足該類產品的信賴性要求。按照JEDEC(Joint Electron Device Engineering Council)標準進行可靠性驗證,每種條件各投了45個產品,具體可靠性項目如表2所示,實驗結果顯示可靠性結果Pass,且未發現分層,斷裂等失效[18]。但是UT封裝技術也存在局限性,如果產品的Seal Ring在Pad外側,則無法采用該類封裝結構。

4.4 直孔結構封裝技術

隨著CMOS制造工藝的演變,由原先的FSI變成BSI,再演變到如今的Stack和Triple Stack技術,金屬Pad中的Low-k材料非常易碎,給封裝帶來很大挑戰。為了滿足新興的CIS晶圓級封裝,華天科技(昆山)電子有限公司開發了垂直通孔封裝技術。該技術可以滿足I/O(Input/Output)數目更多、可靠性要求更高、金屬Pad結構更復雜的芯片的封裝需求。直孔封裝工藝流程如圖10所示,首先將來料預處理晶圓和做好圍堰的玻璃進行晶圓級永久鍵合,通過機械研磨和去應力刻蝕達到規定的厚度。采用Bosch刻蝕工藝形成垂直通孔,直孔蝕刻是關鍵工藝步驟,直孔刻蝕中常見的Scallop、Footing、Notch等問題都會對產品電性能產生較大影響。刻蝕完成后采用超聲波清洗去除表面由刻蝕生成的氟化物,清洗效果將直接影響后續的二氧化硅沉積。直孔技術無法采用光刻膠涂布形成絕緣層,因為孔側壁無法掛膠,因此需要采用PECVD(Plasma Enhanced Chemical Vapor Deposition)沉積二氧化硅絕緣。由于CIS無法耐受超過230℃的溫度,因此需要開發低溫PECVD技術,解決膜孔底覆蓋率、低溫膜應力和膜層結合力差的問題。接著是再布線工藝,區別于其他WLP技術,直孔技術需要采用高腔PVD(Physical Vapor Deposition)沉積Ti/Cu種子層,從而滿足孔底覆蓋率要求,電鍍工藝也需要重新優化,增加前處理保證孔底浸潤性,實現孔內線路的連續[18-21]。圖11為直孔結構SEM圖。直孔技術由于通常應用在車載等高端領域,為了保證球高均一性,通常采用植球工藝。直孔技術也通過可靠性驗證,測試項目如表3所示。

表3 直孔技術可靠性測試項目

圖10 直孔封裝工藝流程

圖11 直孔結構SEM圖

5 結論

本文介紹了幾種常見的圖像傳感器晶圓級封裝技術,可以滿足FSI、BSI和Stack三種不同CIS的晶圓級封裝需求。由于晶圓級封裝具有小尺寸、低成本的特點,越來越多不同像素的CIS采用晶圓級封裝技術,目前2 M/5 M像素產品是主流,未來隨著晶圓級封裝技術的不斷更新迭代,8 M/13 M像素產品也有望實現晶圓級封裝。