傳感器陣列數據鏈路故障診斷橋接模塊設計

龔靜康,王治

(杭州應用聲學研究所,浙江 杭州 310013)

近年來,數據通信鏈路傳輸技術發展迅速[1],無論是單向、雙向交替還是雙向同時傳輸技術均得到快速發展,但是隨著傳輸數據量的增大,容易導致數據通信鏈路傳輸過程中出現異常,異常原因包括數據丟包、鏈路中斷、傳輸時鐘不匹配等,常規通信鏈路傳輸異常檢測方法操作流程復雜,需要專業的技術人員操作。大規模傳感器陣列的數據傳輸異常檢測難度進一步增加,常規檢修方法已不能滿足工程應用要求。

因此確保快速有效地對大規模傳感器陣列進行故障診斷、定位和排除,并確保檢測數據穩定快速傳輸,是提高現場維修人員維修效率的根本方法。當前市場也存在多種故障診斷設備[2-5],但是并不存在專門針對大規模傳感器陣列的數據鏈路故障檢測設備。

文中針對上述問題,設計并制作了一種基于網絡處理器的數據鏈路診斷橋接模塊,該模塊可以快速確定數據傳輸鏈路中故障的位置及故障原因。

1 系統設計

故障診斷橋接模塊主要任務為接收待檢測設備數據和整理、下發控制命令,模擬待檢測設備數據發送、控制和檢測時鐘等。系統主要由處理器MPC8560及外圍設備組成,外圍設備包括網絡處理芯片、NOR FLASH、DDR、ETHPHY、FPGA、FIFO 和電源模塊。

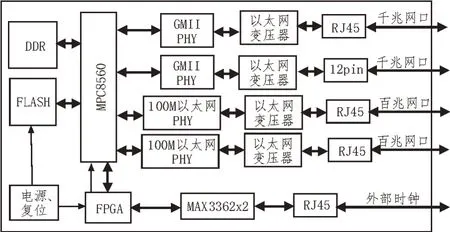

故障診斷總體架構如圖1 所示。故障診斷橋接模塊以Freescale 公司PowerQUICC III?系列高性能網絡處理器MPC8560 為核心設計,CPU 主頻為833 MHz,支持16 位UTOPIA 2 層接口,ATM 通信數據帶寬可達622 Mbps。故障診斷橋接模塊主要接口包括與主控PC 機通信的1 000 M 以太網接口、與待檢測設備數據交互的100 M 以太網接口。通過GMII接口外擴兩個1 000 M 以太網PHY,實現與主控PC機網絡通信與調試功能;通過GMII接口外擴兩個1 00 M以太網PHY,實現與鏈路中通信功能;擴展32 MB Flash 程序存儲器和64 MB DDR SDRAM 存儲器,并使用一片FPGA 作為處理器上電控制和復位,處理器通過與FPGA 進行通信實現同步采集時鐘的產生和時鐘診斷。

圖1 故障診斷橋接模塊總體架構示意圖

2 詳細設計

2.1 處理器單元實現

大規模傳感器陣列下的數據傳輸量大,百兆以太網傳輸并不能滿足數據傳輸的實時性要求,千兆以太網具有速率高、成本低和穩定性好等優點。當前信息化技術的快速發展,已有多種處理器單元下的千兆以太網接口設計方案[6-9]。此外還有較多的基于FPGA 的千兆以太網數據傳輸設計方案,但是成本相對較高[10-13]。

為了降低應用成本,滿足并保證設備的可靠性要求,文中設計的處理器單元包括MPC8560 及其周邊電路,主要實現網絡收發,命令控制等功能。處理器通過千兆網口與工控機主板進行數據交互,接收主控軟件命令以及相關數據上傳。處理器通過與FPGA 交互完成時鐘的相關功能。處理器通過百兆網口完成與數據鏈路中的數據交互,數據鏈路檢測等功能。

1)處理器時鐘設計

MPC8560 外部時鐘為3.3 V LVTTL 電平,頻率為33 MHz,精度要求為+/-50 ppm。

2)UART 端口設計

MPC8560 有一個UART 端口,通過RJ45 插件,用于調試。

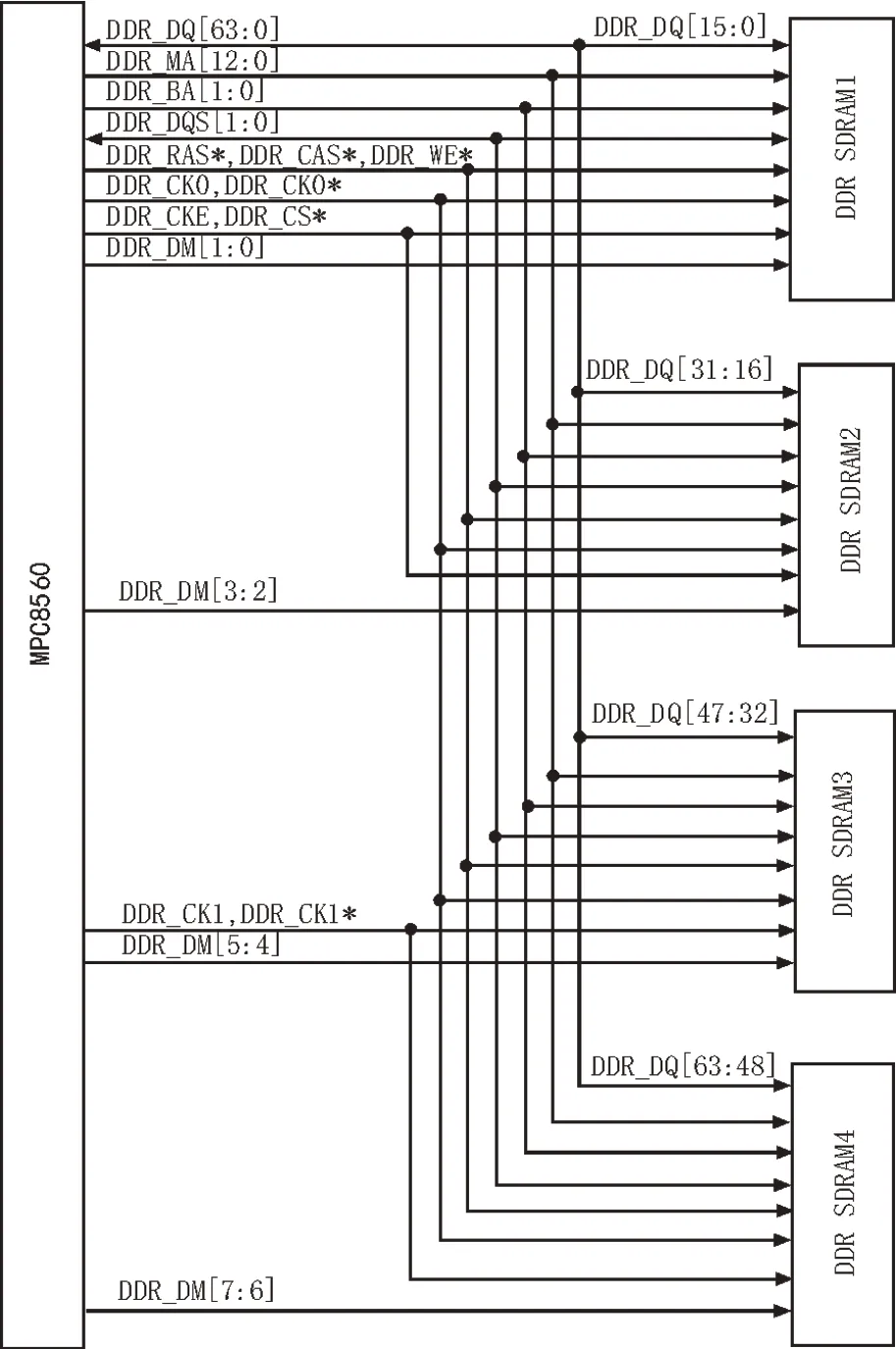

3)DDR SDRAM 設計

DDR SDRAM(Double Data Rate SDRAM,雙倍速率同步動態隨機存儲器),由處理器直接控制,為系統程序的執行提供內部存儲資源。MPC8560 處理器外擴了4 片DDR SDRAM 芯片MT46V16M16,組成了總容量為1 Gb,并具有64 位數據口線的DDR 模塊,以滿足系統對數據處理和程序運行的需要。MPC8560 通過各信號線完成對4 片DDR SDRAM 芯片的控制與信息交互,實現對程序和數據的存取。處理器與4 片DDR SDRAM 芯片之間的口線連接如圖2 所示。

圖2 DDR SDRAM連接框圖

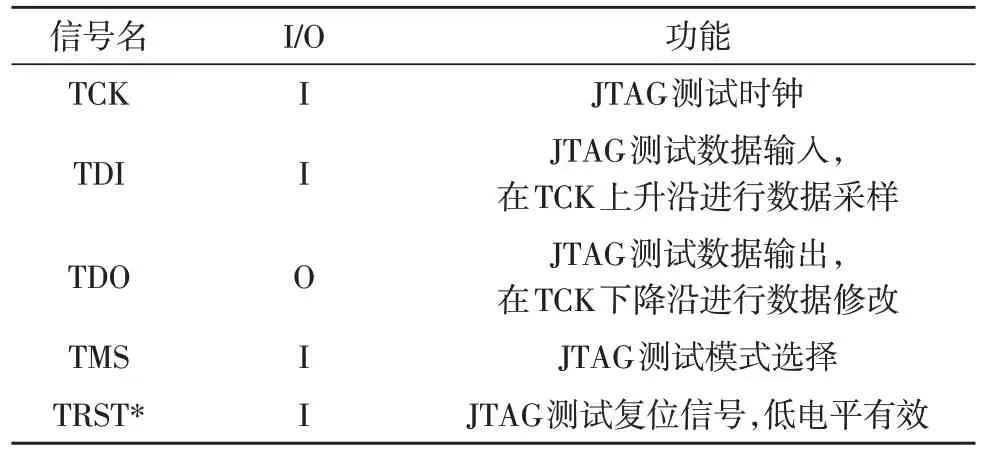

4)MPC8560 處理器的JTAG 接口信號線功能如表1 所示,主要實現以下3 種功能:

表1 JTAG接口信號線功能表

①獲取MPC8560 的運行信息,以完成對處理器芯片的調試;

②通過JTAG 接口實現處理器的復位;

③對FLASH 芯片進行程序燒錄,完成程序的修改與升級。

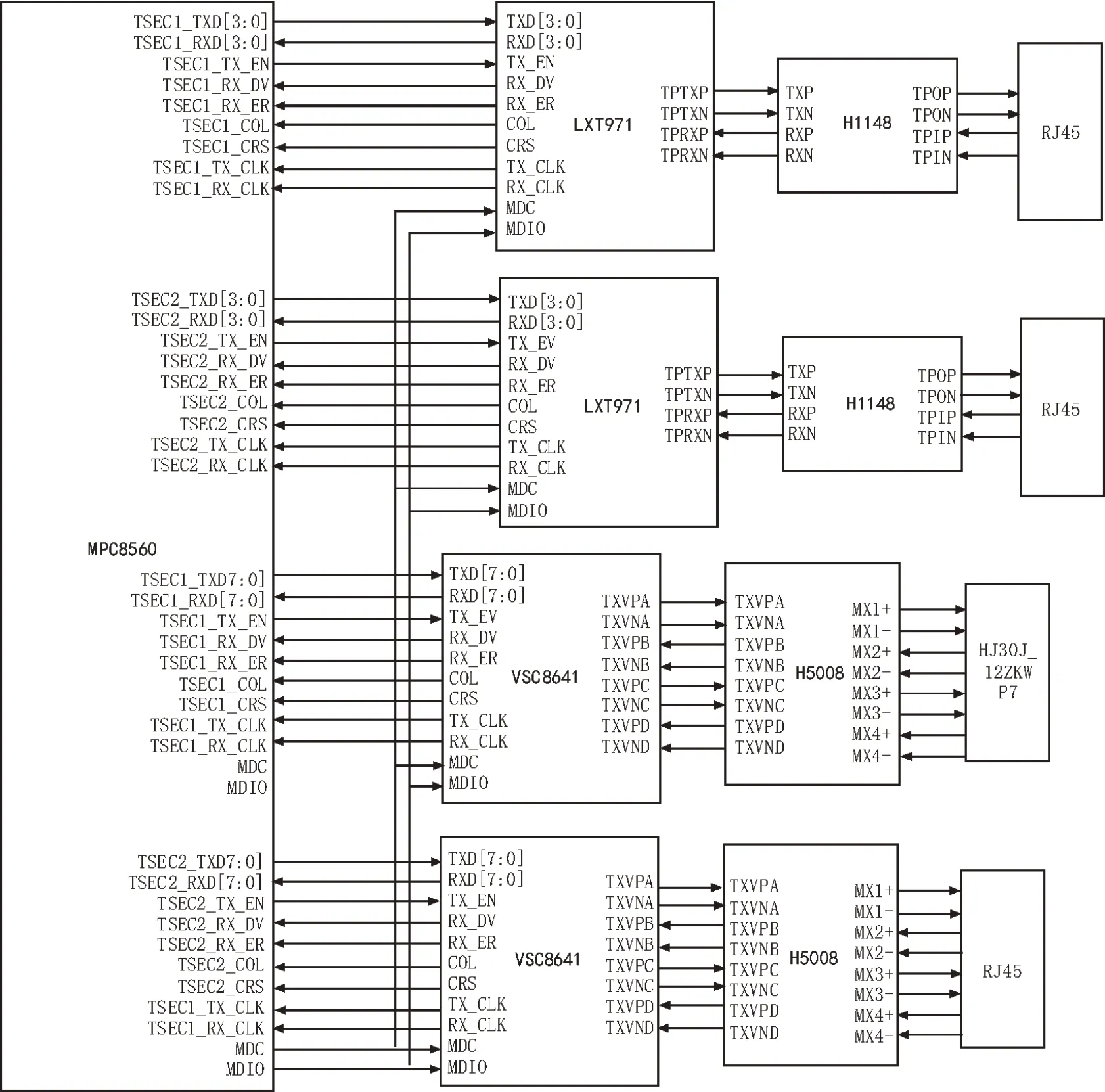

5)以太網接口設計MPC8560 自帶10/100/1 000 Mbps 以太網控制器(TSEC),該系統利用該控制器擴展了兩路1 000 M 以太網接口和兩路100 M 以太網接口。TSECs 和FCC2 分別使用GMII 接口模式和MII 接口模式與以太網PHY 芯片進行交互[14]。

該系統選用VSC8641 作為1 000 M 以太網PHY芯片,LXT971作為100 M以太網PHY芯片與MPC8560 處理器相連。以太網接口的連接框圖如圖3 所示。

圖3 以太網接口連接框圖

2.2 電源模塊說明

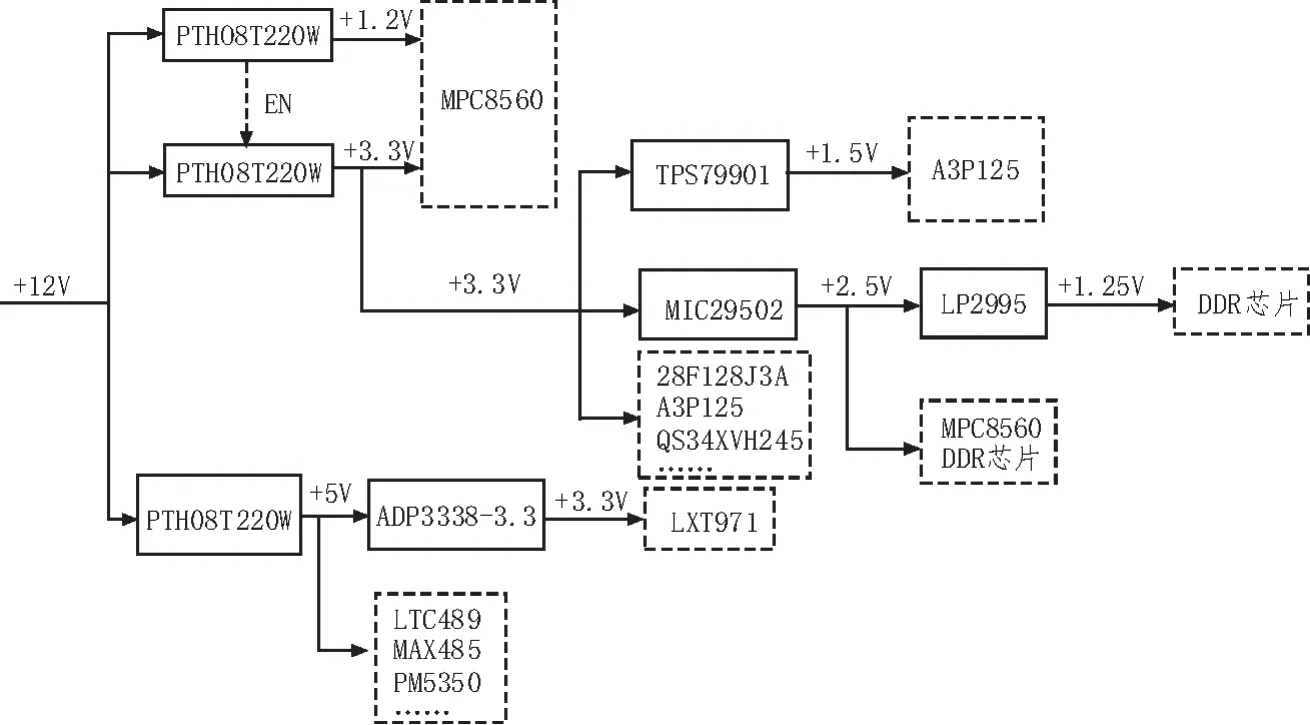

電源模塊以12 V直流電源輸入,通過PTH 08T220W非隔離寬輸出調節電源模塊產生+1.2 V、+3.3 V、+5 V的直流電壓,其中+1.2 V和3.3 V滿足MPC8560的供電需求,另外將+3.3 V 的電壓輸出通過TPS79901 和MIC29502 降壓分別得到+1.5 V和+2.5 V的輸出,其中+1.5 V的電壓輸出給A3P125供 電,+2.5 V 給MPC8560 DDR 芯片供電,同時將+2.5 V再次降壓,得到+1.25 V的電壓輸出,滿足DDR芯片的供電需求。+5 V 的電壓輸出通過ADP 3338-3.3 降壓芯片,得到正+3.3 V 的電壓輸出,滿足LXT971 的供電需求。供電架構框圖如圖4 所示。

圖4 供電架構框圖

2.3 單元配合描述

FPGA 與處理器通過GPIO 進行交互。采用5 個處理器GPIO 接口總線實現通信。處理器通過兩個千兆網口與工控機連接,獲取主控軟件命令和數據上傳,并實現調試功能;串口與工控機相連,實現處理器通信調試;兩個百兆網口連接數據鏈路,完成其他測試功能。

2.4 時鐘分配

該系統各芯片采用的時鐘如表2 所示。

表2 各芯片采用的時鐘分配示例表

2.5 系統復位設計

數據鏈路故障診斷橋接模塊功能復雜,模擬電路和數字電路集成在同一電路系統中,并統一供電。電源上電時,需要一個復位信號初始化數字電路中的存儲單元,如數字寄存器,模擬電路中積分器等,以確保芯片進入正常的工作狀態,因此系統上電復位信號的設計至關重要[15]。

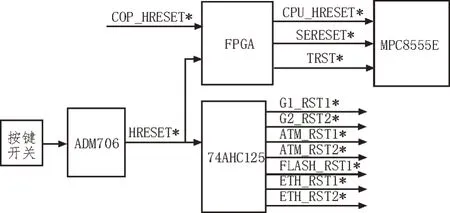

文獻[15-17]分別針對彈載系統、磁阻傳感器和電能表的系統復位問題設計了復位電路,成本低、但增加了系統復雜度。文中整個復位模塊的設計以復位芯片ADM706 為核心,配合74AHC125 和FPGA實現對整個系統的復位控制。系統內的復位線路如圖5 所示。

圖5 系統復位信號設計框圖

其中,ADM706 是ADI 公司設計的一款電壓監控復位芯片,可在3.3 V 電源穩定后發送復位脈沖,實現對系統的啟動復位。在系統運行過程中,ADM706 可通過監測按鍵開關的開關情況,當按下按鍵開關后,ADM706 產生復位脈沖HREST*,并將其發往FPGA 和三態緩沖器74AHC125,實現對系統的硬復位。FPGA 通過HRESET 和調試復位信號COP_HRESET*生成處理器復位信號CPU_HRESET*,控制處理器復位。74AHC125 芯片輸出的復位信號包括1 000 M 以太網PHY 芯片復位信號G_RST1/2*、100 M 以太網PHY芯片復位信號ETH_RST1/2*、ATM PHY 復位信號ATM_RST1/2*、FIFO 芯片復位信號FIFO_RST和FLASH 復位信號FLASH_RST*。除了硬件復位外,在進行JTAG 調試時,可通過JTAG 接口的復位信號之間實現對MPC8560 的e500 核心的軟復位。通過多種復位方式保證系統運行的可靠性與穩定性。

3 實驗測試

3.1 設計結果

按照上述設計方法,故障診斷橋接模塊設計完成布板后的成品如圖6 所示。

圖6 故障診斷橋接模塊印制板

3.2 測試方法和測試結果

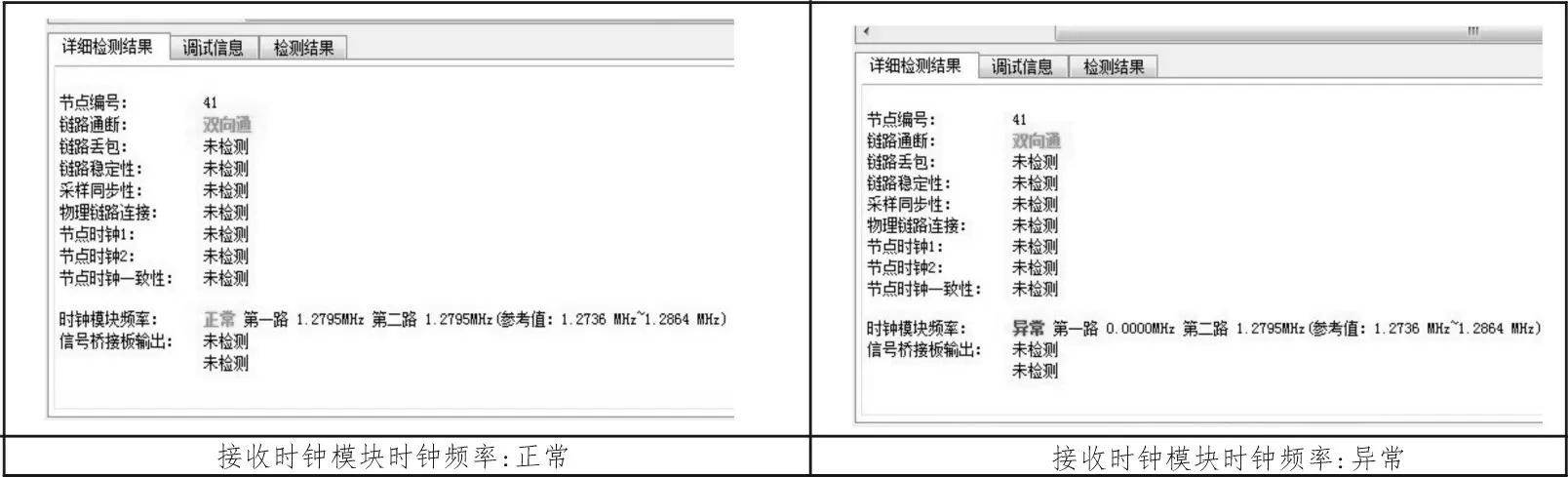

3.2.1 時鐘狀態檢測驗證

運行時鐘控制與狀態分析軟件,通過信號發生器模擬時鐘信號的無時鐘、過慢、過快、正常等狀態,查詢故障診斷橋接模塊獲取到的時鐘狀態,觀察是否正確;將第41 個節點的第一路時鐘斷開,通過數據鏈路故障診斷橋接模塊及相應的上位機軟件進行觀測,能夠顯示第一路時鐘頻率為0,即斷開狀態,判斷異常。時鐘狀態異常前后檢測對比結果如圖7所示。

圖7 時鐘狀態檢測

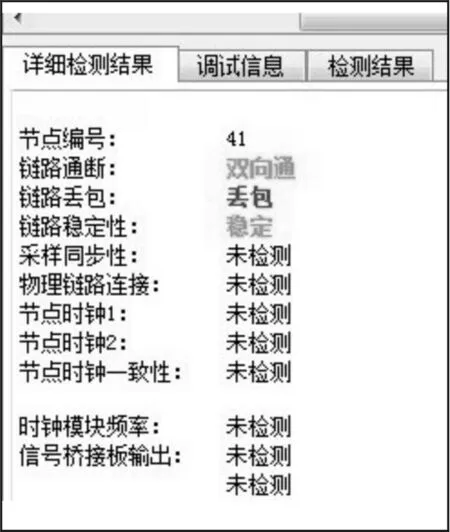

3.2.2 數據丟包檢測

故障診斷橋接模塊接入鏈路中,運行采集傳輸系統數據采集分析軟件,給所有通道輸入動態范圍內的信號,并任意變化,觀察是否存在數據包丟失現象。搭建含有丟包節點的采集傳輸系統,將第41 號節點設計為丟包節點,連接到故障檢測數據傳輸鏈路模塊,加電測試,通過相應的上位機軟件并進行觀測,檢測結果如圖8 所示,檢測結果表明,該節點的數據鏈路通信正常,但是存在丟包問題。

圖8 鏈路丟包及鏈路穩定性

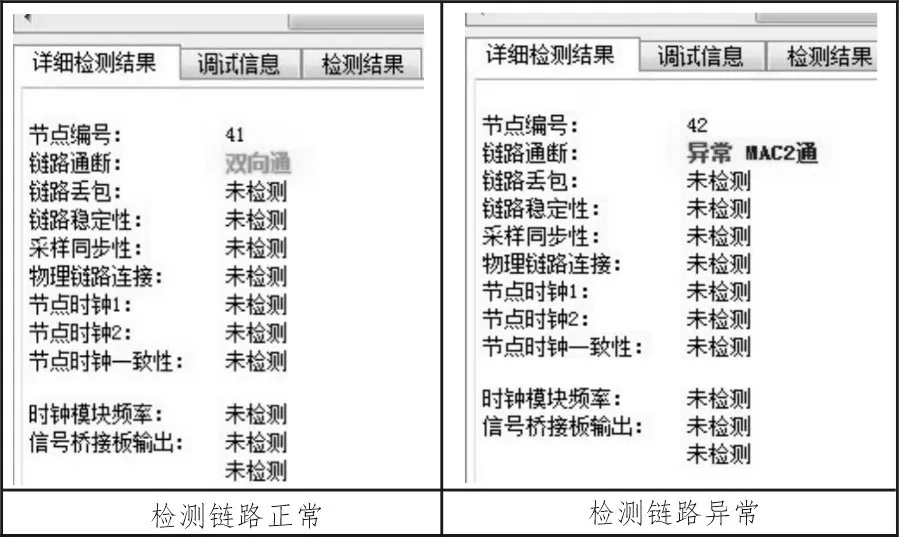

3.2.3 傳輸鏈路故障檢測

斷開鏈路中第41 號節點處的傳輸鏈路,通過數據鏈路故障診斷橋接模塊及相應的上位機軟件進行觀測,斷開前后檢測對比結果如圖9所示,其中異常情況下已不能顯示第41號節點,并指示鏈路斷開狀態。

圖9 鏈路檢測

4 結論

該文針對工程應用中數據傳輸鏈路中常見的故障問題,設計了故障診斷橋接模塊,并通過實驗驗證該電路的有效性。通過該模塊的設計,實現大規模傳感器陣列故障的準確檢測、數據穩定的傳輸,進而大大縮減了維修人員維修設備時的故障排查時間,提高了檢修效率。