一款DC~40 GHz 六位數控衰減器芯片設計

李光超,周睿濤,蔣 樂,張 鎮,豆興昆

(中科芯集成電路有限公司,江蘇無錫 214000)

近年來,MMIC 單片集成微波電路[1-4]憑借其體積小、重量輕、性能優良、可靠性高、可批量生產等優點在微波通信等領域的整機系統中得到廣泛的運用。隨著軍用和民用技術的飛速發展,微波通信等領域的整機系統對超寬帶MMIC 數控衰減器的性能提出更高的要求,在確保實現高衰減精度的同時,還必須保證低衰減附加相移[5-6]。傳統的砷化鎵數控衰減器需要外加TTL 驅動器,增加了應用的復雜性,而內置驅動的砷化鎵數控衰減器[7-9]使用靈活,在應用方面更加簡單,可靠性更高,裝配難度更低,鍵合線更少,小型化和實用化更容易。

文中研制了一款超寬帶集成數字驅動的6 位數控衰減器,工作頻率為DC~40 GHz,衰減位由0.5 dB、1 dB、2 dB、4 dB、8 dB、16 dB 6 個基本衰減位組成,通過對不同拓撲結構進行分析,并合理地安排每一個衰減位,最終在該頻段實現了設計指標。

1 電路設計

1.1 衰減器電路設計

數控衰減器由微波開關器件、傳輸線、電阻、偏置和控制電路構成,通過切換電壓來控制開關的通斷,使信號經過不同的路徑傳播,從而產生插損的變化。數控衰減器的主要技術指標有工作頻段、插入損耗、衰減量、衰減精度、衰減附加調相、電壓駐波比等。為此,必須選用合適的電路拓撲,對各種指標進行綜合的優化設計。

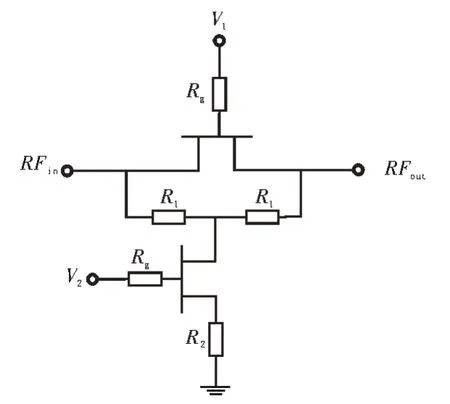

數字衰減器有以下4 種常見衰減拓撲結構形式:開關T型、開關橋T型、開關π型和SPDT選通式型[10-12]。根據技術指標的要求,0.5 dB、1 dB 位使用簡化開關T 型衰減器[13],如圖1 所示,該結構的優點是對于小衰減位通態插損小、附加調相小、面積小。2 dB、4 dB位使用開關T 型和開關π型衰減器,如圖2 和圖3 所示,該結構的優點是對于中衰減位,通態插損小、附加調相小、面積小。8 dB、16 dB 位使用SPDT 選通式型衰減器,如圖4 所示,該結構的優點是對于大衰減位附加調相小、衰減精度高。

圖1 0.5 dB、1 dB電路拓撲

圖2 2 dB電路拓撲

圖3 4 dB電路拓撲

圖4 8 dB、16 dB電路拓撲

為降低6 個衰減位級聯后的相互影響,一般在設計每一個衰減位時要求各個衰減位在頻帶內的駐波足夠小,一般駐波最好小于1.2。6 個衰減單元級聯時,應把受相鄰端口影響較小的放在多個衰減位的兩端,而把受相鄰端口影響較大的放在中間。最終,6 位單片衰減器拓撲圖如圖5 所示。

圖5 6位數控衰減器電路拓撲

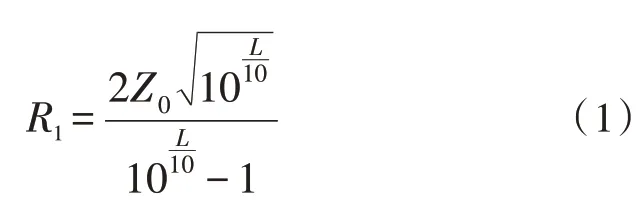

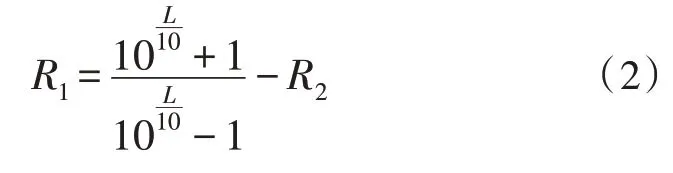

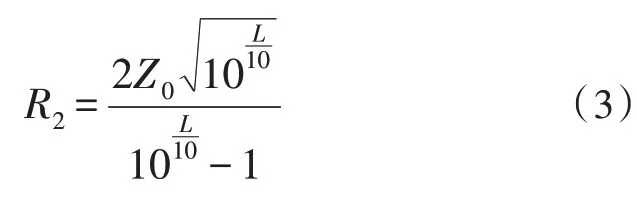

簡化開關T 型衰減器R1初始值可通過式(1)得 出[14-15],其中Z0為特征阻抗,其值為50 Ω,L為插入損耗。

開關T型衰減器R1和R2初始值可由式(2)、(3)得出:

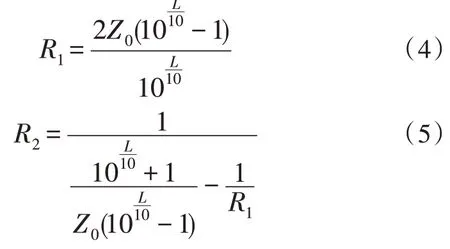

開關π型衰減器、SPDT 選通式型衰減器R1和R2初始值可由式(4)、(5)得出:

1.2 驅動器電路設計

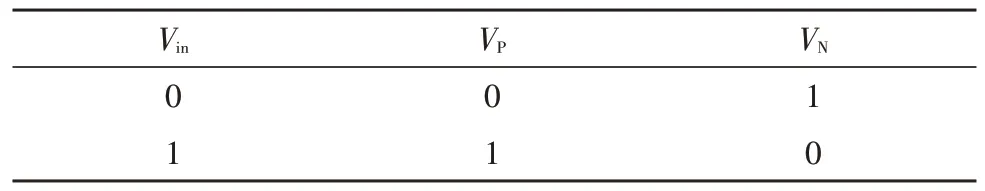

驅動器電路的功能是將單個控制信號0 V或+5 V轉換為一對電平值為-5 V 和0 V 的反相控制電平,以此控制多個pHEMT 開關管的導通和截止,從而實現數控衰減器衰減量的改變。將TTL 信號的輸入低電平0 V 視為“0”,輸入高電平+5 V 視為“1”,輸出低電平-5 V 視為“0”,輸出高電平0 V 視為“1”。單位數字驅動器真值表如表1 所示。

表1 驅動器真值表

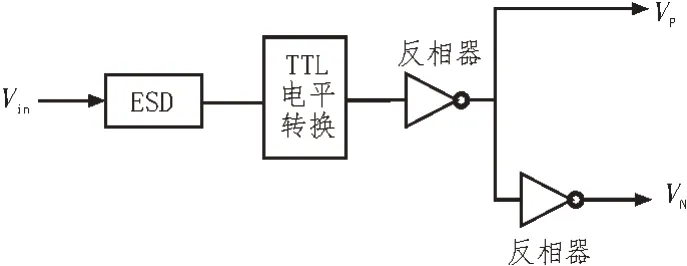

根據數控衰減器的工作狀態,基于增強型和耗盡型pHEMT 直流模型設計了一種數字驅動器,結構原理如圖6 所示。驅動器主要由ESD 電路、TTL 電平轉換電路、反相器電路等構成。其中ESD 電路用于數字驅動器的靜電防護;TTL 電平轉換電路用于將TTL 電平轉化為適合反相器的輸入電平;反相器電路用于實現輸出一個與TTL 電平同相、一個與TTL反相的電平。

圖6 數字驅動器原理圖

2 仿真和測試結果

2.1 仿真結果

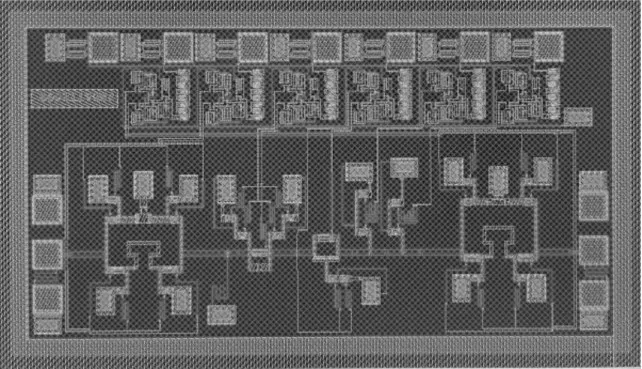

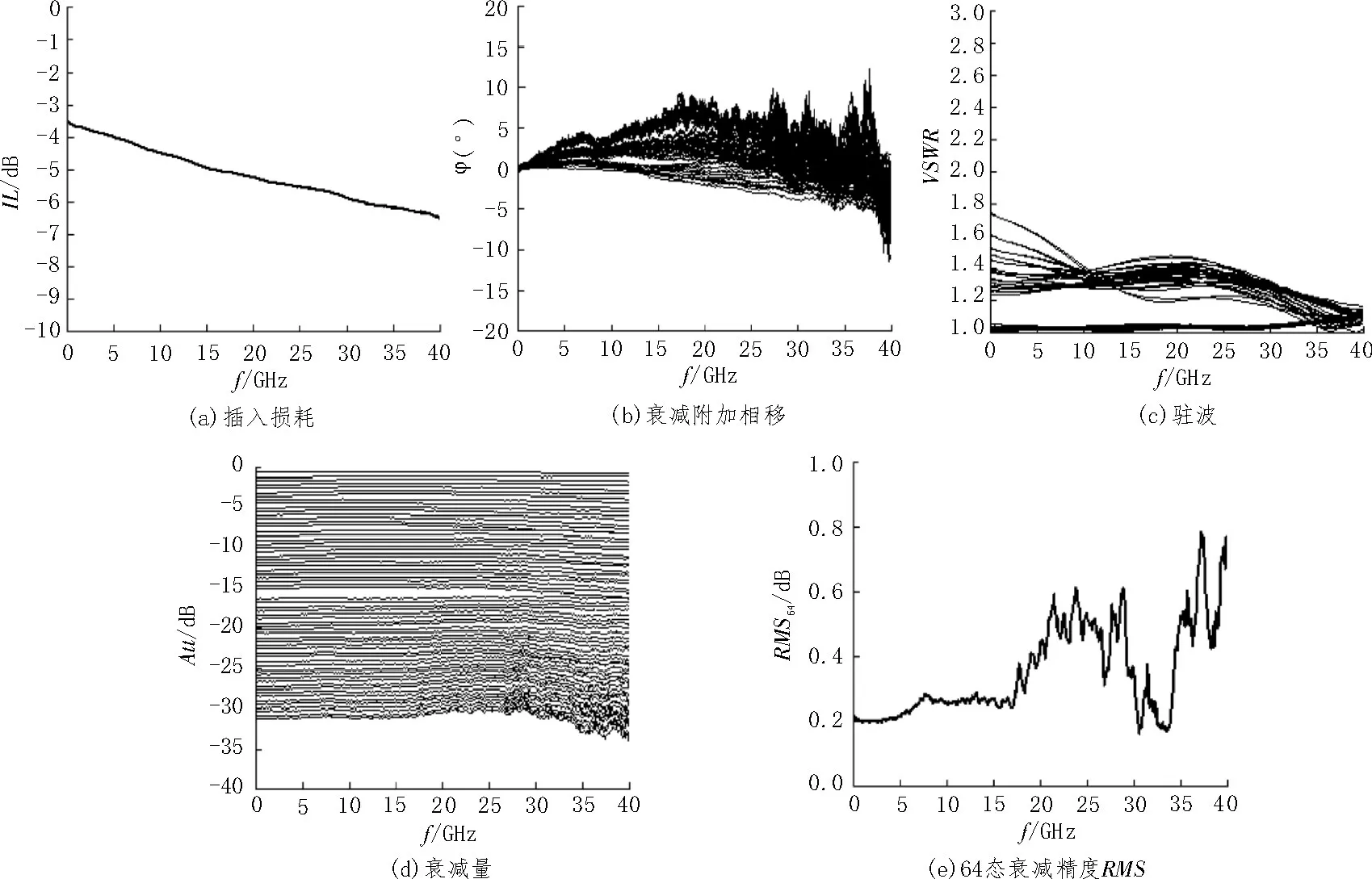

數控衰減器芯片基于GaAs pHEMT 0.15 μm 工藝研制,選用ADS 2016 軟件完成單個電路的仿真和整體版圖的設計,6 位數控衰減器芯片整體版圖如圖7 所示,仿真結果如圖8 所示。圖8(a)、圖8(b)和圖8(c)分別是數控衰減器基態插入損耗、全態衰減附加調相和駐波;圖8(d)和圖8(e)分別是數控衰減器衰減量和64 態衰減精度RMS。

圖7 6位數控衰減器芯片整體版圖

圖8 6位數控衰減器芯片仿真結果

2.2 測試結果

流片完成的6 位數控衰減器芯片如圖9 所示。

圖9 6位數控衰減器芯片

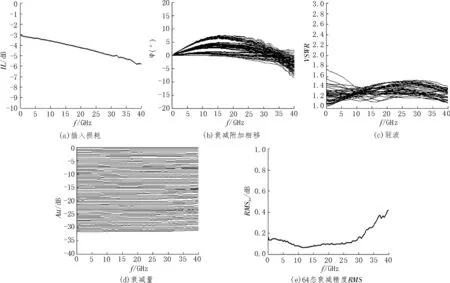

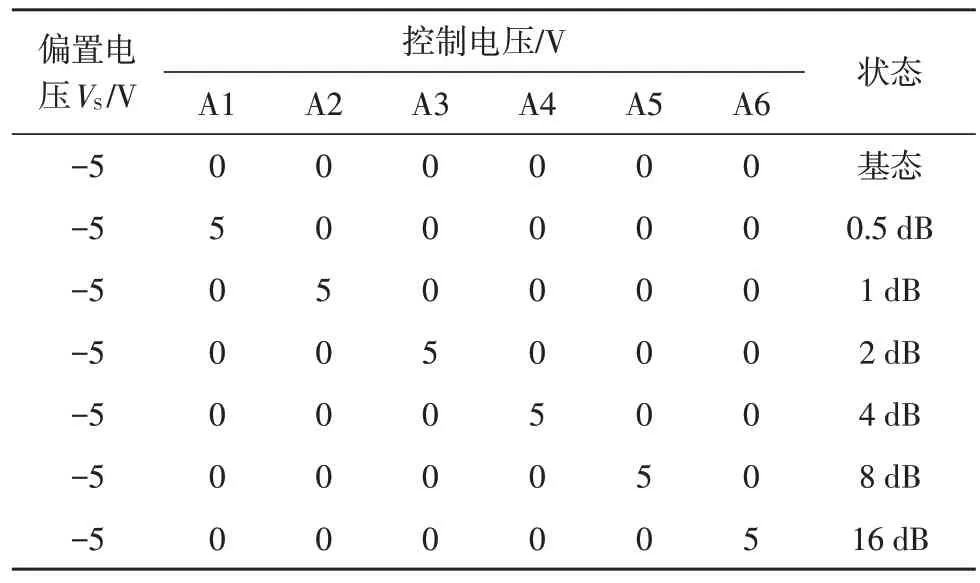

芯片的電性能采用Cascade 探針臺、ACP-GSGI50 微波探針、Agilent 5225B 矢量網絡分析儀、數字多路電源和直流電源進行在片測量,芯片的偏置電壓和真值表如表2 所示。測試結果如圖10 所示。圖10(a)、圖10(b)和圖10(c)分別是數控衰減器基態插入損耗、衰減附加調相和駐波,圖10(d)和圖10(e)分別是數控衰減器衰減量和64 態衰減精度RMS。

表2 偏置電壓和真值表

圖10 6位數控衰減器芯片測試結果

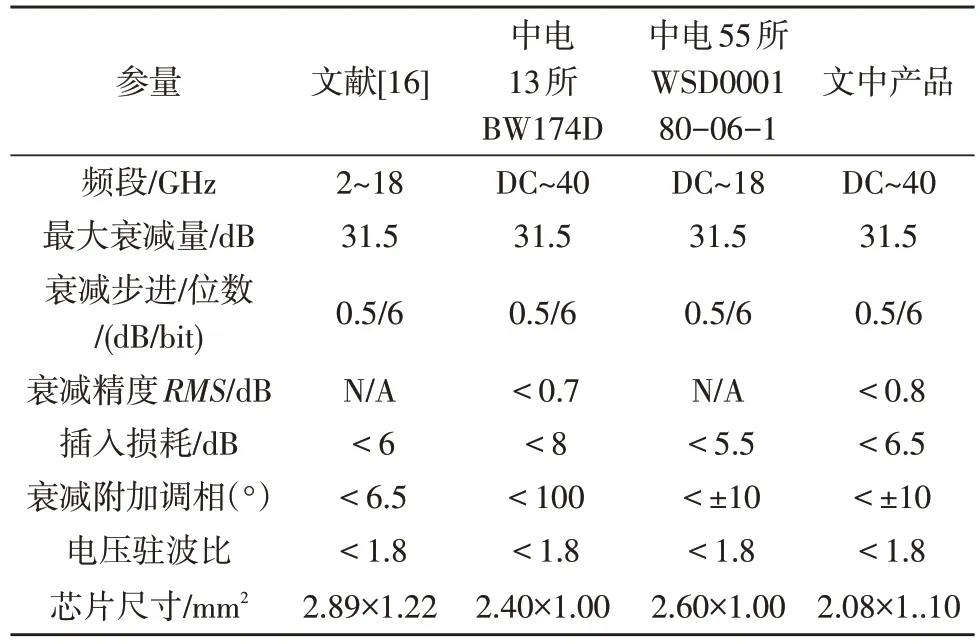

通過仿真和實測結果的對比可以看出,實測結果比仿真結果稍有惡化,插入損耗仿真小于6 dB,實測小于6.5 dB。衰減附加調相仿真小于±8°,實測小于±10°。輸入駐波仿真小于1.8,實測小于1.8。64 態衰減精度RMS仿真小于0.5 dB,實測小于0.8 dB。經過初步分析可知,實測和仿真存在偏差的主要原因在于:1)金屬層加工精度的誤差。2)開關管小信號S 參數的測量誤差。3)版圖面積壓縮導致某些微帶線之間的耦合效應。表3 為所設計的衰減器和同類產品及文獻[16]的比較。

表3 測試結果與同類產品的比較

3 結論

文中成功研制了一款集成數字驅動的超寬帶數控衰減器芯片,工作頻段為DC~40 GHz,芯片為-5 V電源工作,TTL 控制方式控制,控制電壓為0/5 V。插入損耗小于6.5 dB,均方根衰減精度(64態)小于0.8 dB,衰減附加調相小于±10°,兩端口全態衰減態的輸入輸出駐波比小于1.8,芯片尺寸為2.08 mm×1.1 mm×0.1 mm。