基于C6678的STAP并行處理系統(tǒng)設(shè)計(jì)

廉志凌

(中國(guó)電子科技集團(tuán)第三十八研究所 合肥 230031)

0 引言

空時(shí)自適應(yīng)信號(hào)處理技術(shù)(STAP)是1973年由Brennan和Reed提出的,該方法將傳統(tǒng)的處理由陣元域推廣到了脈沖和陣元二維數(shù)據(jù)域,性能遠(yuǎn)優(yōu)于空時(shí)級(jí)聯(lián)處理方法,被認(rèn)為理論上是最優(yōu)的。具體工程實(shí)現(xiàn)時(shí),根據(jù)文獻(xiàn)Klemm的研究,要使STAP處理的輸出信雜噪比損失小于3dB,用來(lái)估計(jì)雜波協(xié)方差矩陣的獨(dú)立同分布(IID)訓(xùn)練樣本數(shù)必須大于處理器維數(shù)的兩倍。當(dāng)空域采樣數(shù)N和時(shí)域采樣數(shù)K較大時(shí),全空時(shí)處理很難獲得足夠的樣本,同時(shí)空時(shí)處理所需的設(shè)備量和運(yùn)算量驚人,從而使得準(zhǔn)最優(yōu)的降維處理成為一種必然選擇。

降維處理方法包括固定結(jié)構(gòu)降維處理和自適應(yīng)降維處理,固定降維處理算法中的比較經(jīng)典的就是mDT-SAP算法。該算法在時(shí)域先對(duì)各天線的輸出針對(duì)不同的多普勒頻率用窄帶濾波器抑制大量的非同多普勒雜波,剩余同多普勒雜波由后續(xù)的空域自適應(yīng)處理完成,該方法在副瓣雜波區(qū)是準(zhǔn)最優(yōu)的。

為了驗(yàn)證mDT-SAP的處理性能,本文搭建了以TI公司C6678處理芯片為主處理器的硬件系統(tǒng),設(shè)計(jì)了基于RapidIO通信的核間通信機(jī)制,實(shí)現(xiàn)了系統(tǒng)的自適應(yīng)調(diào)度和并行處理。

1 硬件平臺(tái)設(shè)計(jì)

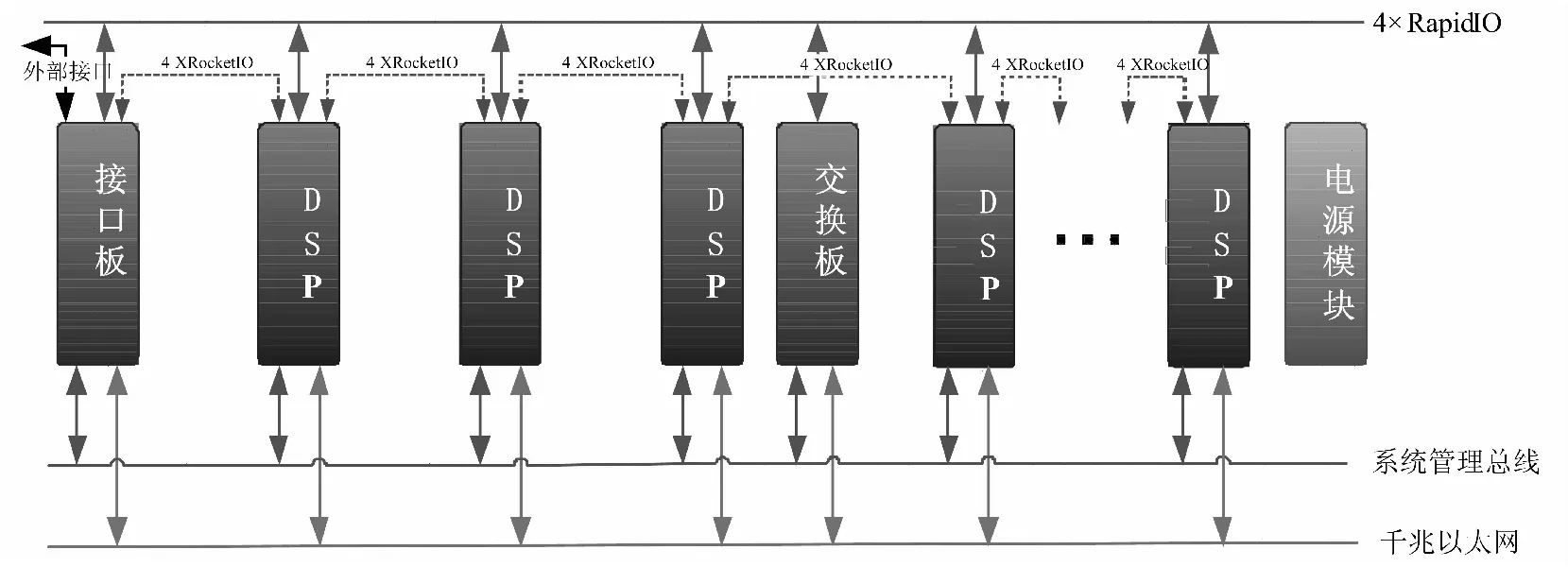

硬件系統(tǒng)的設(shè)計(jì)需要綜合考慮系統(tǒng)的體積、重量、功耗、處理能力,以及系統(tǒng)可擴(kuò)展能力。綜合以上因素,本系統(tǒng)的設(shè)備量包括:一塊接口板,一塊交換板,以及若干信號(hào)處理板。信號(hào)處理板的板卡數(shù)量可根據(jù)實(shí)際需求調(diào)整,信號(hào)處理系統(tǒng)架構(gòu)圖如圖1所示。

圖1 信號(hào)處理系統(tǒng)架構(gòu)圖

接口板的主要作用是將接收到的光信號(hào)轉(zhuǎn)換為電信號(hào),然后在FPGA內(nèi)完成DBF并將合成結(jié)果發(fā)給信號(hào)處理板的第一片C6678。

交換板布有1848芯片,板卡之間大容量的數(shù)據(jù)交換均需要通過(guò)該板卡完成。

每塊信號(hào)處理板板載4片C6678處理芯片,用來(lái)完成所有的信號(hào)處理算法實(shí)現(xiàn),主要特性如下:

1) 單片C6678可外掛8GB的DDR3,工作頻率為800MHz;

2) 每片C6678通過(guò)RapidIO Switch和PCIe Switch分別實(shí)現(xiàn)與背板的RapidIO及PCIe的總線互聯(lián),構(gòu)成數(shù)據(jù)傳輸通路;

3) FPGA實(shí)現(xiàn)背板的RocketIO,Link,板內(nèi)PCIe以及RapidIO總線的接口轉(zhuǎn)換;

4) 系統(tǒng)可通過(guò)CPLD監(jiān)控單板狀態(tài),實(shí)現(xiàn)單板配置,復(fù)位等。

信號(hào)處理板采用的C6678處理器內(nèi)部包含8個(gè)運(yùn)算核,最高頻率可達(dá)到1.25GHz。在主頻1GHz情況下,其標(biāo)稱的定點(diǎn)運(yùn)算能力達(dá)到256GMACs,浮點(diǎn)運(yùn)算能力達(dá)到128Gflops。每個(gè)C6678核內(nèi)置32KB L1程序Cache,32K L1數(shù)據(jù)Cache以及512K L2Cache,8個(gè)4096KB SRAM。

2 算法原理

2.1 全空時(shí)自適應(yīng)濾波的原理

簡(jiǎn)單起見,設(shè)雷達(dá)天線為水平排列的一維線陣,單元個(gè)數(shù)為,一個(gè)相干處理間隔內(nèi)的脈沖個(gè)數(shù)為。則第個(gè)陣元第次快拍的數(shù)據(jù)為(,),第個(gè)脈沖的陣列數(shù)據(jù)矢量X()為

()=[(1,),(2,),…,(,)]

(1)

將(),=1,2,…,排成×1的列矢量,即

(2)

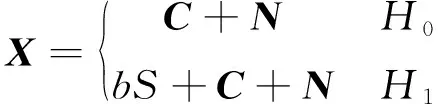

假設(shè)表示無(wú)目標(biāo)信號(hào),只有雜波和噪聲,表示既有信號(hào),又有雜波和噪聲,則有表達(dá)式

(3)

其中為目標(biāo)回波復(fù)幅度;和分別表示雜波和內(nèi)部熱噪聲矢量;為歸一化信號(hào)空時(shí)導(dǎo)向矢量。根據(jù)最大信雜噪比準(zhǔn)則,最優(yōu)權(quán)矢量通過(guò)求解如式(4)線性約束最優(yōu)化問題得到

(4)

解得=μ,其中=1()

2.2 3DT-STAP的原理

3DT算法采用相鄰三個(gè)多普勒通道作為時(shí)域自由度,天線子孔徑作為空域自由度,共同構(gòu)造空時(shí)二維導(dǎo)向矢量,再結(jié)合雜波協(xié)方差矩陣分解獲取相應(yīng)的權(quán)矢量,對(duì)空時(shí)兩維數(shù)據(jù)進(jìn)行二維濾波,從而抑制雜波,檢測(cè)動(dòng)目標(biāo)。該方法可以在距離-多普勒域形成相對(duì)比較窄的凹口,有利于檢測(cè)地面低速目標(biāo),同時(shí)由于用了更多的自由度,無(wú)論在主瓣區(qū)還是在副瓣區(qū)都能取得比較好的性能。

從數(shù)學(xué)的角度,3DT處理可以等效成采樣數(shù)據(jù)矢量通過(guò)一個(gè)×3的降維矩陣的線性變換過(guò)程,其中和3分別為降維前后的數(shù)據(jù)維數(shù)。 降維前后的數(shù)據(jù)矢量和信號(hào)導(dǎo)向矢量有如式(5)關(guān)系。

(5)

降維后的雜波協(xié)方差矩陣為

(6)

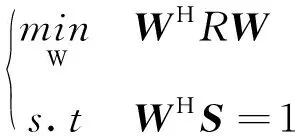

根據(jù)線性約束最小方差準(zhǔn)則(),相應(yīng)的最優(yōu)權(quán)矢量為

(7)

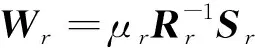

圖2 mDT-STAP信號(hào)處理流程圖

3 信號(hào)處理軟件設(shè)計(jì)

信號(hào)處理的處理架構(gòu)為1+,即1片C6678負(fù)責(zé)數(shù)據(jù)分發(fā),片C6678負(fù)責(zé)處理,處理芯片之間的任務(wù)分配,采用輪詢策略。信號(hào)處理的軟件設(shè)計(jì)包括數(shù)據(jù)分發(fā)、片間通信和并行處理三個(gè)方面。

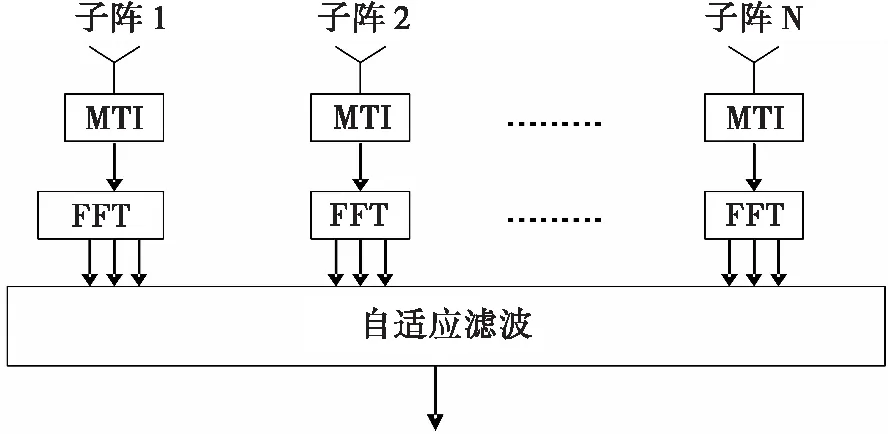

3.1 數(shù)據(jù)分發(fā)

信號(hào)處理板的第一片C6678芯片收到接口板發(fā)過(guò)來(lái)的數(shù)據(jù)之后,以脈沖為基本單位進(jìn)行數(shù)據(jù)分發(fā)。由于DSP的最小處理單位為一個(gè)波位,第一片6678在進(jìn)行數(shù)據(jù)分發(fā)時(shí),先判斷當(dāng)前脈沖所在的波序號(hào),相同波序的數(shù)據(jù)分發(fā)給同一處理芯片。

考慮到雷達(dá)設(shè)計(jì)時(shí)序時(shí),不同方位的脈沖數(shù)不同,從而每個(gè)波位的數(shù)據(jù)量也不盡相同,這樣在以波位為單位的調(diào)度和處理時(shí),會(huì)造成負(fù)載的不均衡。因此我們?cè)谠O(shè)計(jì)分發(fā)策略時(shí),采用自適應(yīng)調(diào)度策略,即每次進(jìn)行數(shù)據(jù)分發(fā)時(shí),都會(huì)判斷對(duì)應(yīng)DSP的忙閑狀態(tài),并將數(shù)據(jù)分發(fā)給處于‘閑’狀態(tài)的DSP,具體流程如圖3所示。

圖3 數(shù)據(jù)分發(fā)流程

3.2 通信機(jī)制

為了提高效率,減少不必要的時(shí)間和存儲(chǔ)空間的開支,信號(hào)處理采用裸系統(tǒng)運(yùn)行,將全部資源用于處理數(shù)據(jù)。這樣也就帶來(lái)了一個(gè)新的問題,如何快速有效地在DSP芯片之間進(jìn)行通信呢?

我們基于已有的RapidIO協(xié)議,建立了一套完整的片間通信機(jī)制,該機(jī)制已應(yīng)用于某工程,運(yùn)行良好,主要工作原理如下:

1)上電后,每塊信號(hào)處理芯片需要向第一片C6678的固定內(nèi)存地址發(fā)送狀態(tài)標(biāo)識(shí)1,表示該板卡做好準(zhǔn)備接收數(shù)據(jù)。

2)第一片C6678在分發(fā)數(shù)據(jù)時(shí),只將數(shù)據(jù)分發(fā)給狀態(tài)標(biāo)識(shí)為1的板卡,若輪循至某板卡,而該板卡狀態(tài)標(biāo)識(shí)非1,則跳過(guò)該芯片,發(fā)送給下一芯片。

3)C6678處理芯片接收完一個(gè)完整的波位數(shù)據(jù)時(shí),將其對(duì)應(yīng)內(nèi)存地址的狀態(tài)置為0,不再接收數(shù)據(jù)。

4)處理芯片處理完當(dāng)前波位數(shù)據(jù),將狀態(tài)標(biāo)識(shí)置為1,準(zhǔn)備下一次處理。

3.3 DT-STAP的并行處理

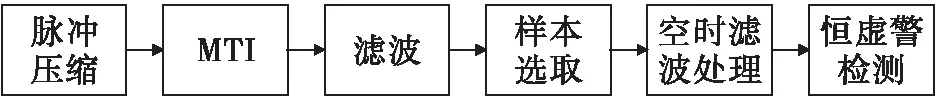

3DT-STAP處理包括脈沖壓縮、MTI、多普勒濾波、樣本選取、空時(shí)自適應(yīng)濾波處理以及恒虛警檢測(cè),流程如圖4所示。

圖4 處理流程

工程實(shí)現(xiàn)時(shí),為了減少系統(tǒng)的設(shè)備量,降低成本,我們希望充分發(fā)揮C6678的處理能力,采用8核并行處理架構(gòu)。事實(shí)上,由于信號(hào)處理為串行處理架構(gòu),即必須保證一個(gè)節(jié)點(diǎn)完成后再進(jìn)行下一個(gè)節(jié)點(diǎn)的運(yùn)算,因此對(duì)3DT-STAP整體上進(jìn)行分解,從而實(shí)現(xiàn)8核并行處理,顯然不可能。

我們的實(shí)現(xiàn)策略是,在每個(gè)處理節(jié)點(diǎn),將任務(wù)平均分到8個(gè)運(yùn)算核,實(shí)現(xiàn)并行處理,然后在每個(gè)節(jié)點(diǎn)之后再8核同步一下,保證該處理節(jié)點(diǎn)任務(wù)徹底完成。這樣就可以發(fā)揮C6678的8核并行處理能力了。

在將每個(gè)處理節(jié)點(diǎn)數(shù)據(jù)分解到8個(gè)核的過(guò)程中,因?yàn)槊總€(gè)處理節(jié)點(diǎn)的數(shù)據(jù)處理方式不一樣,在分解時(shí)需要對(duì)數(shù)據(jù)進(jìn)行解耦,保證每個(gè)核的數(shù)據(jù)輸入對(duì)其它核沒有依賴,處理結(jié)果也不會(huì)影響其它核。對(duì)3DT-STAP算法進(jìn)行分析之后,每個(gè)處理節(jié)點(diǎn)的任務(wù)分解策略如下:

1) 脈沖壓縮:由于不同脈沖的處理順序并無(wú)要求,且相互獨(dú)立,可以分核按照脈沖個(gè)數(shù)進(jìn)行任務(wù)劃分,每個(gè)核處理總脈沖數(shù)的八分之一。

2)多普勒濾波:不同距離單元的數(shù)據(jù)相互獨(dú)立,因此按照距離單元進(jìn)行劃分,每個(gè)核處理距離單元總數(shù)的八分之一。

3)空時(shí)自適應(yīng)處理:因?yàn)椴煌l道之間數(shù)據(jù)處理相互獨(dú)立,故自適應(yīng)濾波的處理分頻道進(jìn)行。

4 實(shí)測(cè)數(shù)據(jù)處理

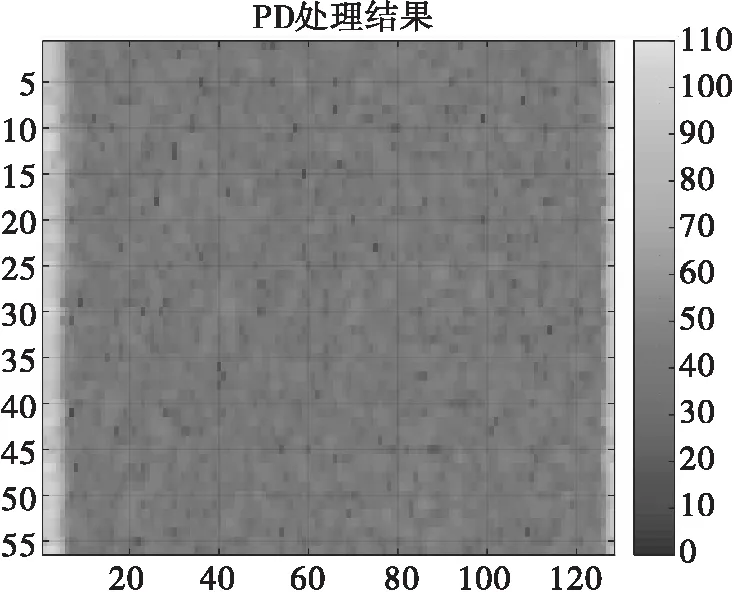

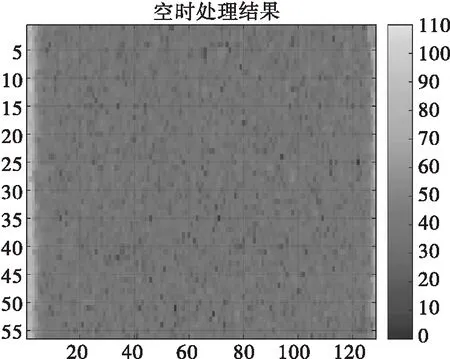

圖5為某實(shí)測(cè)數(shù)據(jù)經(jīng)過(guò)PD處理后的距離-多普勒二維譜,圖6為該批數(shù)據(jù)經(jīng)過(guò)STAP處理的距離-多普勒二維譜,圓形區(qū)域?yàn)榕湓嚹繕?biāo)所在位置。從兩圖的對(duì)比可以看出,經(jīng)過(guò)3DT-STAP處理之后,主瓣雜波和副瓣雜波區(qū)域被明顯削弱,使得處于副瓣雜波區(qū)域的目標(biāo)能量顯著增強(qiáng),有效提高了目標(biāo)的信雜噪比(約為3 dB)。

圖5 PD處理結(jié)果

圖6 3DT處理結(jié)果

5 結(jié)束語(yǔ)

本文搭建了一套基于c6678信號(hào)處理板用于實(shí)現(xiàn)3DT-STAP的硬件系統(tǒng),提出了一套自適應(yīng)的數(shù)據(jù)分發(fā)機(jī)制和芯片之間的通信機(jī)制,并在深入理解3DT-STAP算法的基礎(chǔ)上,結(jié)合C6678的處理器特點(diǎn),提出了基于處理節(jié)點(diǎn)的8核并行處理算法。需要指出的是,本文的處理架構(gòu)和并行處理思想不僅適用于3DT-STAP處理,對(duì)于常規(guī)的PD處理及類似算法均可適用。最后,實(shí)測(cè)數(shù)據(jù)的處理結(jié)果驗(yàn)證了本系統(tǒng)的正確性和有效性。