基于動態亞閾值的延遲型PUF 電路設計

張笑天, 汪鵬君,2, 張躍軍, 張會紅

( 1. 寧波大學電路與系統研究所,浙江 寧波 315211;2. 溫州大學電氣與電子工程學院,浙江 溫州 325035)

物聯網的不斷發展助推了便攜式設備數量呈現大規模增長的趨勢,片上系統(System on Chip,SoC)技術的進步縮短了電子產品開發周期并使之在便攜式設備中得到了廣泛應用。然而在用戶對便攜式設備需求增長的同時,信息安全問題也日益凸顯。攻擊者可通過逆向工程等攻擊方式竊取設備中的存儲數據[1],損害了用戶與設備廠商的利益。物理不可克隆函數(Physical Unclonable Function, PUF)電路利用集成電路制造工藝偏差產生數字密鑰,可有效降低侵入式攻擊風險[2]。但隨著人工智能技術的不斷發展,通過機器學習對PUF 進行模型攻擊已成為可能,PUF 面臨新型安全問題[3]。此外,由于資源受限型系統中電路面積、電池能量等資源有限,新穎的輔助電路和加密技術無法有效使用,其安全強度受到限制,因此兼具低能耗與高安全性的PUF 電路設計已成為信息安全領域中的關鍵研究方向[4]。

文獻[5]提出了一種低能耗SRAM 型PUF 電路,具有良好的隨機性,但隨著溫度、電壓的變化,該PUF 電路的穩定性下降。文獻[6]提出了一種亞閾值電流型PUF 電路,具有較低能耗,但其穩定性對溫度變化敏感。文獻[7]提出了一種亞閾值電流型PUF 電路,能有效抵御機器學習攻擊且具有較高穩定性,但是電路面積過大,能耗開銷很大。文獻[8]提出了一種亞閾值延遲型PUF 電路,利用差分對稱設計,提高輸出穩定性,雖然通過降低電壓減少了能耗,但顯著增加了電路延時,并且仍然面臨被模型攻擊的風險。因此,傳統的低功耗PUF 電路已難以進一步提升安全性。

采用亞閾值邏輯是常規低功耗設計方式之一,已有廣泛應用。亞閾值特性也可用于提高PUF 電路輸出函數復雜度。為進一步提高低能耗PUF 電路安全性,本文提出了一種基于動態亞閾值的延遲型(Dynamic Subthreshold Delayed, DSD)PUF 電路設計方案,并采用TSMC 65nm CMOS 工藝進行驗證。該方案將電荷分享效應與動態亞閾值邏輯相結合,能有效降低電路能耗并具有良好的抵御模型攻擊特性。

1 仲裁器PUF 電路與動態亞閾值邏輯

1.1 仲裁器PUF

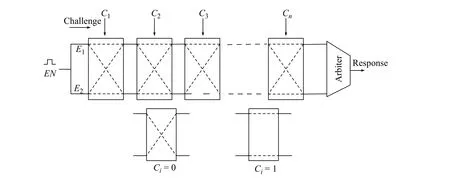

仲裁器PUF(Arbiter PUF, APUF)[9]原理如圖1所示。信號傳輸電路上下對稱,C1、C2、···、Cn信號決定E1和E2傳播至仲裁器的路徑選擇情況。因工藝偏差,E1與E2的傳播路徑延時不相等,它們將在不同時間點到達仲裁器。仲裁器根據這種延遲差輸出具有隨機性的PUF 響應,其電路輸出模型函數如式(1)所示。由于激勵會改變信號傳輸方向,因此w(n)需乘以系數 φ (j)。 φ (j)的計算式如式(2)所示。

圖 1 仲裁器PUF 結構Fig. 1 Architecture of the arbiter PUF

式(1)和式(2)中:r為輸出結果;w(n)對應各子路徑延遲差;sgn 定義為正值取1、負值取0 的函數;j的取值為1~n;C1~Cn為對應激勵信號,其取值均為0 或1。式(1)和式(2)體現了APUF 輸出模型函數是一種線性疊加函數,攻擊者可對APUF 進行建模并預測輸出結果[10]。

1.2 動態亞閾值邏輯

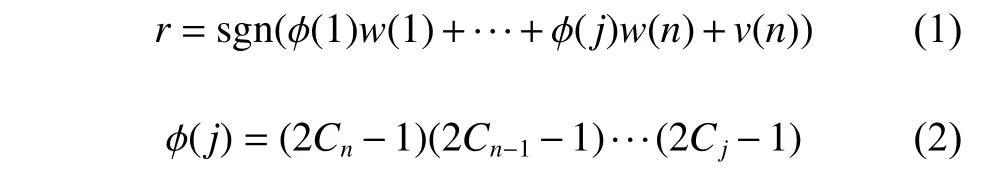

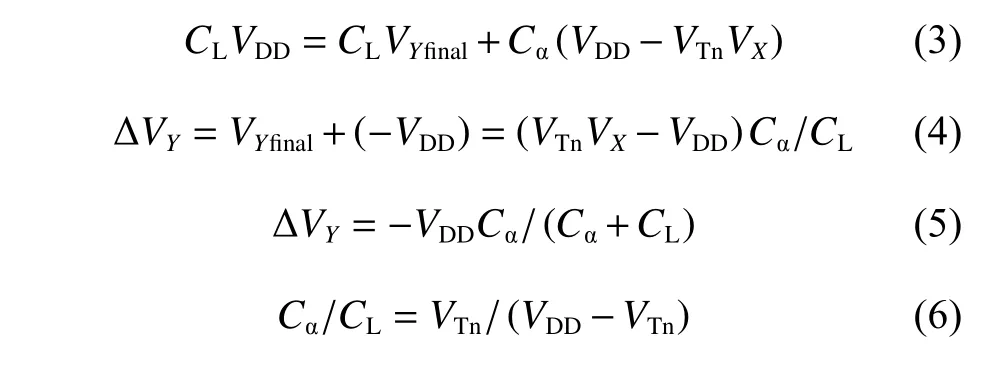

為減少電路功耗,降低電路工作電壓是一種常用方式,但降低電壓也會帶來一系列問題。如圖2(a)所示的靜態CMOS 與非門(NAND gate),相同條件下NMOS 漏源電流比PMOS 大,即使輸入信號A、B全為低電平,NMOS 亞閾值漏電流也不可忽略。隨著電壓下降,動態功耗呈平方關系下降,亞閾值漏電功耗卻以指數形式增長。當電壓下降到一定程度時,靜態漏電流功耗成為主要功耗,因此降低功耗就必須抑制其漏電流。考慮如圖2(b)所示的動態與非門,當時鐘信號CLK為低電平時,電路為預充電狀態,通過負載電容CL,Y被充電至高電平。當CLK為高電平時,電路進入求值狀態。A和B只要任一個為高電平,Y將被放電至低電平,完成與非邏輯運算。該電路在求值過程并不需要PMOS, 與靜態CMOS 相比,相當于可減少兩個串聯大尺寸PMOS。此外,若輸入邏輯數量為N,則靜態CMOS 邏輯晶體管數量為2N,而動態邏輯晶體管數量為N+2。在多輸入邏輯下,動態邏輯能夠節省更多面積,但其缺點是有電荷泄漏以及電荷分享效應。電荷分享效應是指當圖2(b)中A、B邏輯僅有一個為高電平時,下拉堆疊網絡關閉,但是高電平所控制的晶體管仍具有寄生電容,同樣具有儲存電荷能力,Y將發生電平偏移。假設VX、VY分別表示X、Y的電壓值,初始值分別為0、VDD(電源電壓),VTn為晶體管閾值電壓,并以ΔVY表示Y的電壓偏移量。此時分兩種情況:(1) ΔVY<VTn,VX終值等于VDD-VTnVX。由電荷守恒定理可得式(3)和式(4),其中VYfinal代表VY終值,Cα為晶體管N1 的寄生電容值;(2) ΔVY>VTn,VY與VX處于相同值,可得式(5)。兩種情況邊界條件可由式(6)確定,當電容之比小于該值,情況(1)成立,否則情況(2)成立。應當控制ΔVY在合理范圍,否則電路會發生邏輯錯誤。

圖2 靜態與非門和動態與非門Fig. 2 Static and dynamic NAND gate

2 DSD PUF 電路設計

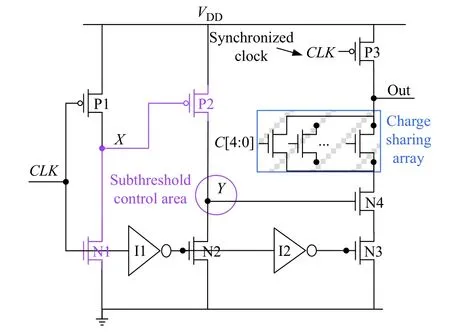

2.1 混合延遲單元電路

混合延遲單元電路采用動態亞閾值邏輯,其結構如圖3 所示。電路由晶體管N1~N4、P1~P3 以及反相器I1、I2 構成。時鐘信號CLK控制電路預充電、求值狀態,當CLK為低電平時,P1、N2、P3 開啟,X與Out 被預充電至高電平,而Y被放電至低電平,預充電階段結束。當CLK跳變至高電平時,電路進入求值狀態,由于下拉網絡開啟,X與Out 將被放電。晶體管P2 漏源電流受X電位影響,隨著X電位下降,P2 晶體管漏源電流逐漸增大。因此Y在電路計算過程中處于動態變化狀態,稱為亞閾值壓控結點,N4 晶體管漏源電流也隨之變化。由于N4 在時鐘剛反轉時漏源電流較低,為避免電路噪聲影響,需要經緩沖器延時開啟,而P3 開啟時間與P1 相同,則下拉網絡具有較好的穩定性。由于反相器I1、I2 的固有延遲,Y電位上升速度比X放電速度慢,在此期間,N4 柵極電位處于變化狀態。電荷分享陣列由5 個并聯NMOS 晶體管組成,受激勵信號C[4:0]控制,每個晶體管開啟都將產生電荷分享效應并引起輸出Out 電壓偏移。因此,盡管整體下拉網絡處于關閉狀態(由于緩沖器的延時,晶體管N3 不會立即開啟),每增加一個開啟的電荷分享晶體管,Out 都將發生電壓偏移。激勵信號控制并聯晶體管開啟數量,并產生不同電壓偏移量從而使輸出節點電壓改變。當CLK經過緩沖器到達N3 晶體管時,Out 開始放電,其初始電壓(即下拉網絡對應的零輸入響應初始值)為改變后的值。因此不同激勵信號對應不同的輸出函數。

圖3 混合延遲單元電路Fig. 3 Hybrid delayed cell circuit

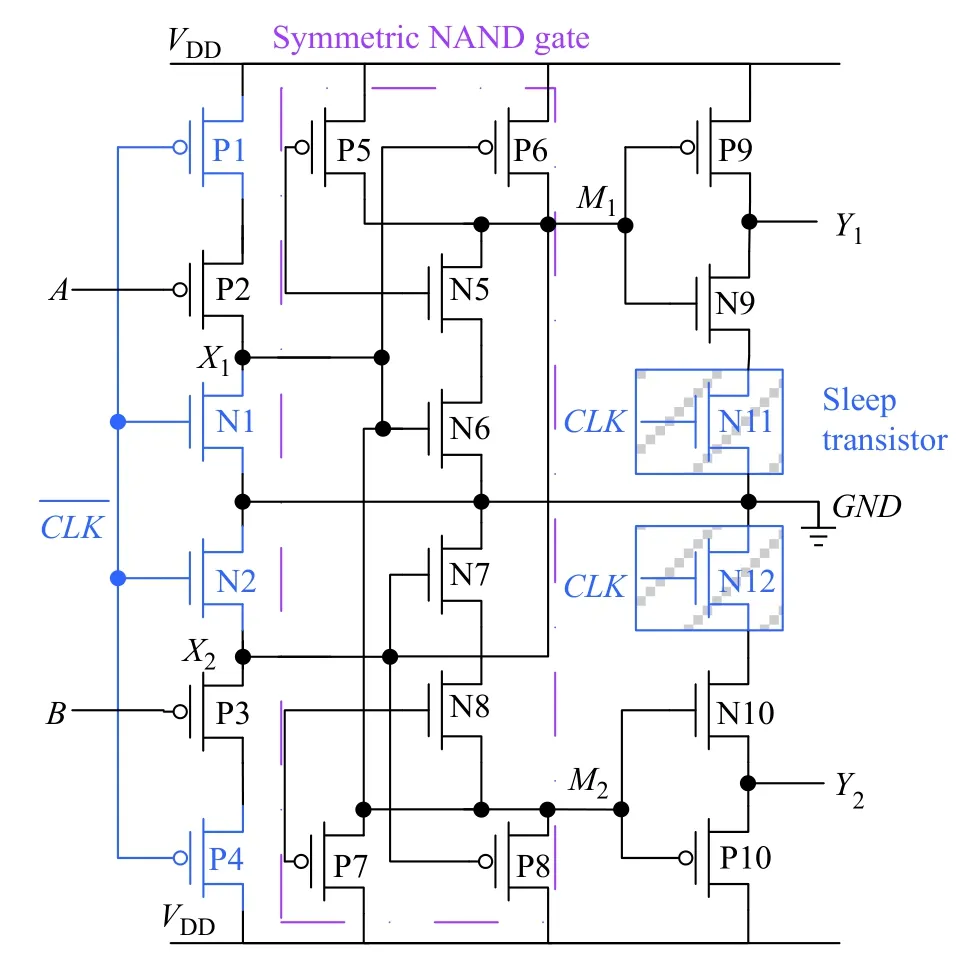

2.2 動態亞閾值判決器

為對混合延遲單元輸出進行判決,設計了動態判決器如圖4 所示。在電路輸入級采用P 型動態反相器設計,晶體管N1、N2、P1、P4 受反相時鐘信號控制,A、B信號作為上拉網絡輸入信號,堆疊NMOS 晶體管有利于平衡PMOS 與NMOS 驅動能力。電路主體為兩個對稱耦合與非門,初始狀態為高電平時,N1、N2 開啟,將X1、X2下拉至低電平,因此與非門輸出停留在高電平。A、B以不一樣的速度降低至低電平時,X1、X2到達對稱與非門輸入端時間點也不一樣,若A下拉速度較快,則M1將被封鎖在低電平,此時晶體管N7 被M1封鎖,M2通過P6 補充電荷維持在高電平,反之則M1輸出高電平,M2輸出低電平。為減少負載效應影響,輸出級采用一級靜態反相器緩沖,并增加N11 與N12 兩個休眠晶體管以減少亞閾值靜態漏電功耗,僅在CLK為高電平時,輸出級下拉網絡開啟,最終Y1與Y2形成互斥輸出,作為判別A、B信號速度快慢的標志。

圖4 動態亞閾值判決器Fig. 4 Dynamic subthreshold arbiter

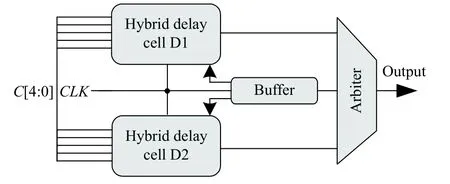

2.3 N 位DSD PUF 電路結構

1 位DSD PUF 單元結構如圖5 所示,兩個混合延遲單元D1、D2 具有相同激勵C[4:0]與時鐘CLK輸入。D1、D2 的輸出信號通過判決器產生1 位PUF 輸出信號。在實際應用中,密鑰通常具有多位,因此構造8×128 位PUF 單元陣列,從128 位PUF 陣列中分別選出1 位形成8 位并行密鑰輸出,并擴展激勵信號至13 位,構成地址與路徑選擇信號,其結構框圖如圖6 所示。最終可在CLK控制下,產生8 位并行數字密鑰。

圖5 1 位DSD PUF 單元框圖Fig. 5 1-bit DSD PUF cell block diagram

圖6 N 位DSD PUF 電路框圖Fig. 6 N-bit DSD PUF circuit block diagram

3 實例結果與分析

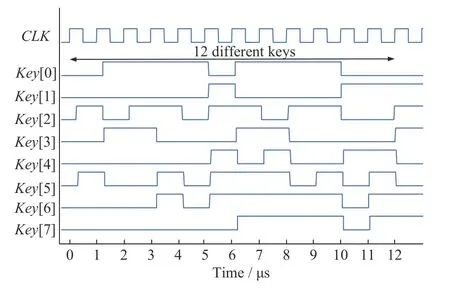

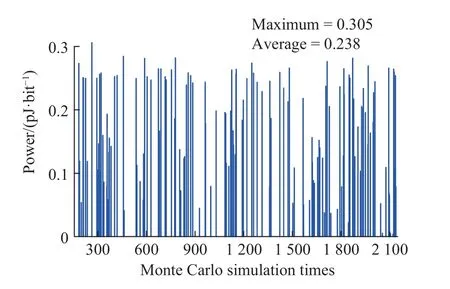

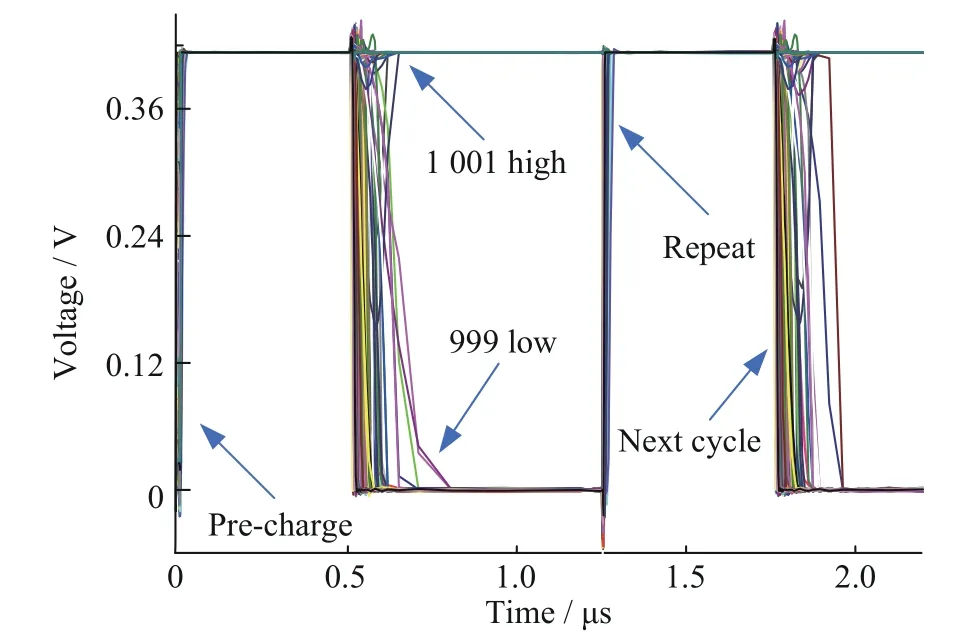

在TSMC 65 nm 工藝下,使用HSPICE 工具進行驗證。電源電壓為0.4 V 時,電路輸出時序圖如圖7所示(13 位激勵信號Cx已省略)。當時鐘跳變至高電平,電路開始產生密鑰Key,在12 次不同Cx下,每個時鐘周期內Key都呈現不同的0、1 分布,具有隨機性。通過蒙特卡洛仿真分析并對其平均能耗進行統計,結果如圖8 所示,DSD PUF 平均能耗為0.238 pJ/bit,最大能耗為0.305 pJ/bit,具有低能耗特點。

圖7 密鑰提取時序圖Fig. 7 Timing diagram of key extraction

圖8 能耗分布Fig. 8 Energy consumption distribution

3.1 DSD PUF 安全性分析

PUF 的隨機性以信息熵Entropy 表示,其表達式如式(7)所示:

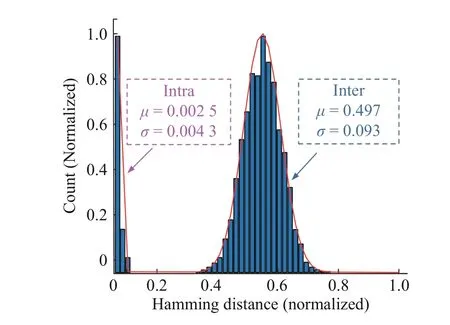

其中,p(r)表示邏輯r的出現概率。對密鑰輸出進行2 048 次蒙特卡羅仿真分析,仿真結果如圖9 所示。高電平輸出個數為1 001,低電平輸出個數為999。由公式可得信息熵為0.999 999 279。其漢明距離分布如圖10 所示,片內、片間漢明距離分別滿足μ=0.002 5、σ=0.004 3 與μ=0.497、σ=0.093 的正態分布,其中μ表示數學期望,σ表示方差。

圖9 2 000 次蒙特卡洛仿真結果Fig. 9 2 000 times Monte Carlo simulation results

圖10 DSD PUF 漢明距離分布Fig. 10 Hamming distance distribution of DSD PUF

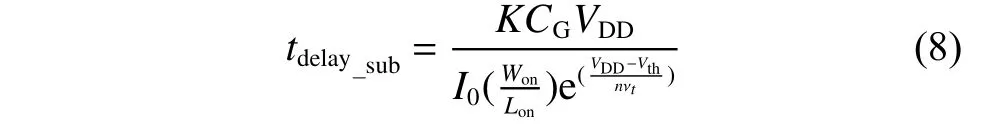

在動態亞閾值邏輯下,DSD PUF 延遲時間tdelay_sub滿足式(8)所示指數特性:

其中:K為線性系數;CG為負載電容;Vth為晶體管閾值電壓;I0為由工藝決定的方塊漏極電流;νt為熱電壓;Won與Lon分別表示充放電過程中等效晶體管的寬與長;n為經驗參數。傳統模型攻擊方式通過搜集一定數量激勵響應對(Challenge Response Pair,CRP)代入輸出模型公式,計算相關系數并建立對應數學模型從而預測剩余密鑰。對于DSD PUF,當激勵不同時,下拉網絡的零輸入響應函數是不一樣的。以f(σ1)、f(σ2)分別表示工藝偏差系數σ1、σ2對延時函數指數部分的影響,即使對于具有相同0、1 數量分布的不同激勵輸入,器件參數偏差也使得指數部分的參數存在差異,該延遲差函數可簡化為:

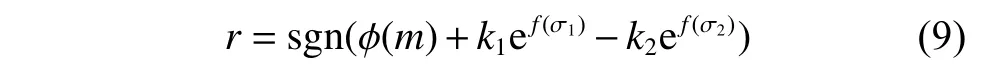

其中:k1、k2為與工藝相關的線性系數; φ (m) 為電路固有延遲。 對DSD PUF 使用人工神經網絡(Artificial Neural Network, ANN)算法進行抗攻擊驗證時,其效果如圖11 所示。可以看出,APUF 在訓練組數量為500 時,預測錯誤率便已明顯減少。DSD PUF 在訓練組數量達5 000 時,預測錯誤率仍接近理想狀態50%。因此DSD PUF 能夠有效抵御這類模型攻擊。

圖11 ANN 算法預測錯誤率Fig. 11 Prediction error rate by ANN algorithm

3.2 DSD PUF 輸出穩定性分析

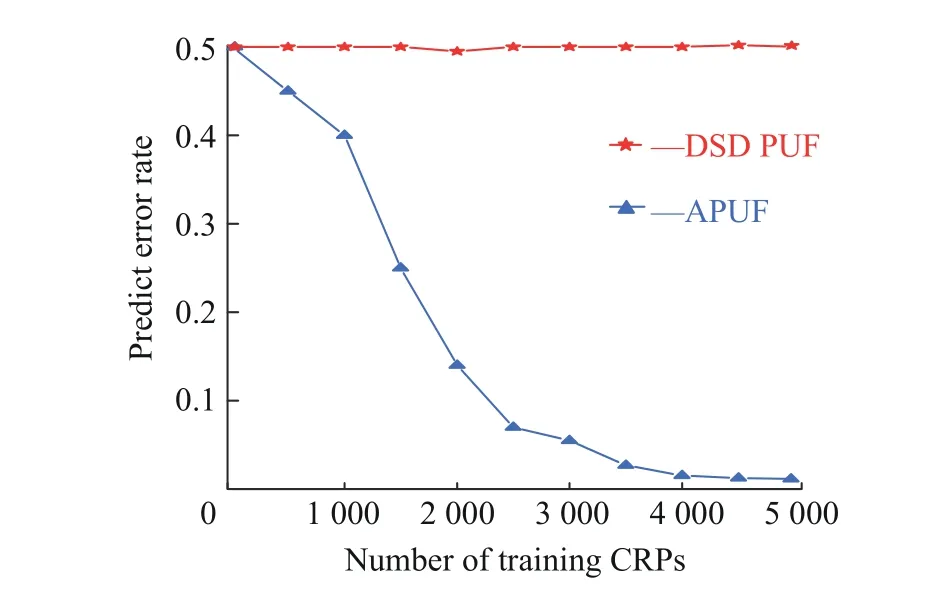

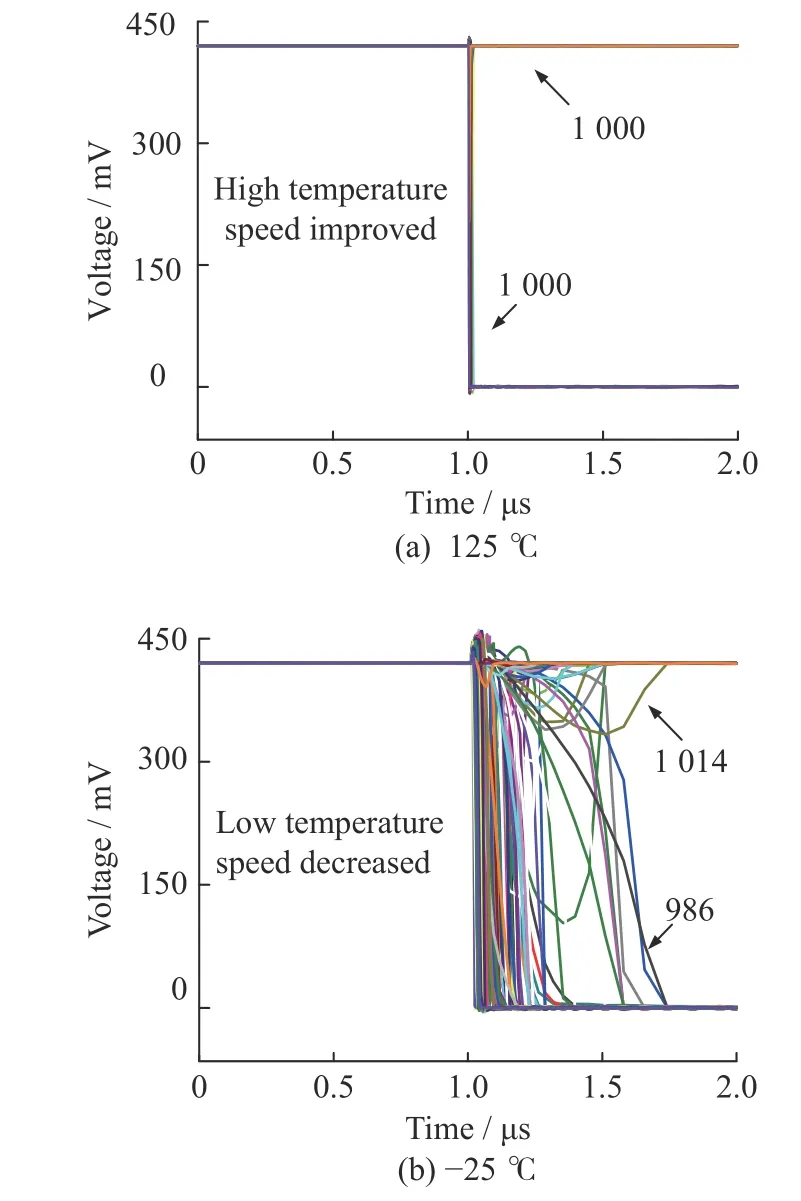

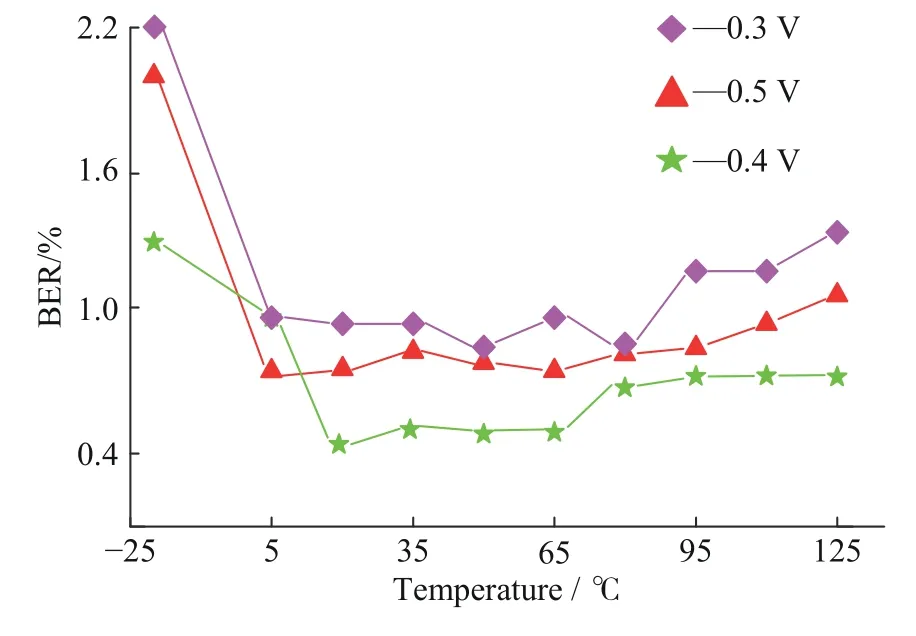

在亞閾值區,溫度對電路性能影響很大,因此對DSD PUF 在不同溫度下進行蒙特卡洛仿真驗證。晶體管閾值電壓與溫度負相關,當溫度升高時,電路中各晶體管漏源電流明顯增加,因此整體速度性能提高。如圖12(a)所示,125 °C 工作溫度下,電路速度性能提高并且高電平個數為1 000,低電平個數為1 000,隨機性接近理想狀態。如圖12(b)所示,當工作溫度降低至-25 °C 時,電路性能明顯下降,高電平個數為1 014,低電平個數為986,電路隨機性變差。這是由于低溫引起亞閾值電流大幅降低,電路延時明顯增加并且易受噪聲干擾而產生錯誤。對不同工作電壓以及溫度下DSD PUF 的誤碼率(Bit Error Rate, BER)進行統計,結果如圖13 所示。盡管高溫使得電路具有更高的隨機性,但對電路穩定性產生影響。對實驗結果分析,DSD PUF 最優工作電壓為0.4 V,此時誤碼率能夠達到0.4%,而在最壞情況下誤碼率為2.19%。與其他相關文獻的對比結果如表1所示。可以看出DSD PUF 輸出信息熵為0.999 999 279,僅次于文獻[13],具有良好隨機性;能耗為0.238 pJ/bit,與同類最優電路相比降低了20.67%。

表1 電路性能比較結果Table 1 Circuit performance comparison results

圖12 極端溫度下的蒙特卡洛仿真情況Fig. 12 Monte Carlo simulation in worst temperature condition

圖13 不同溫度、電壓下的誤碼率Fig. 13 BER against temperature and voltage variations

4 結 論

本文通過對PUF 電路的研究,結合動態亞閾值特性,提出了一種基于動態亞閾值邏輯的延遲型PUF 電路。該電路主要優點為在動態亞閾值邏輯中,利用電荷分享效應改變不同激勵信號下的電路輸出函數。采用TSMC 65nm 工藝設計電路并通過HSPICE 驗證。結果表明,DSD PUF 電路具有良好唯一性和隨機性,其平均能耗為0.238 pJ/bit,與同類最優電路相比降低了20.67%,并能有效抵御模型攻擊。