機載電子跨時鐘域同步電路驗證及可靠性分析

范毓洋, 鄧智, 李子航

(1.中國民航大學 民航航空器適航審定技術重點實驗室, 天津 300300; 2.中國民航大學 適航學院, 天津 300300)

隨著機載電子設備復雜性增加、機載電子芯片設計規模的擴大,集成電路設計中跨時鐘域信號傳輸也逐漸增多。而信號跨時鐘域傳輸不可避免地會在電路中引入亞穩態[1],若亞穩態處理不當,則可能給電路帶來數據丟失、位錯、重匯聚等風險,造成設備關鍵功能的喪失或錯誤。如時鐘檢查電路功能喪失[2]、飛機顯示圖像異常、AFDX交換機數據錯誤等。更嚴重的是,若亞穩態沿信號通道上的寄存器級聯傳播,可能造成芯片燒毀的嚴重后果。如某航天器在為期一年多的地面測試中突然出現故障,經分析發現,航天器出現故障的原因是跨時鐘域電路傳輸引入亞穩態,亞穩態傳播導致片上大量MOS(metal oxide semiconductor)管同時工作致使電路板燒毀[3]。

目前電子設計技術的進步和一些機載電子設計部門的擴張,客觀上也增大了設計中發生亞穩態問題的可能性。如一些硬件綜合工具支持軟件工程師使用高級語言設計硬件電路,與使用RLT代碼進行電路設計相比,跨時鐘域電路的亞穩態問題更容易被設計人員忽略[4]。另外,機載電子設計部門因為人員快速擴張,員工技術水平良莠不齊,不僅使得在設計過程中容易出現同步器功能設計錯誤,也使得同行評審質量下降,不能依靠評審有效發現問題。且隨著特征尺寸的下降、新設計技術的出現[5],芯片電壓下降、時鐘頻率和數據頻率提高、同步路徑增多,導致芯片中已有的功能正確的跨時鐘域信號同步器的可靠性下降。若這些同步設計不經過可靠性評估而直接應用到航空領域,則會產生安全隱患。雖然目前跨時鐘同步電路的問題存在的可能性增大,但是目前的機載電子的驗證活動中,常常會忽視掉針對跨時鐘域傳輸功能和可靠性的驗證活動。

FAA Order 8110.105 A提及了機載電子硬件需進行最好或最壞情況下時序分析[6]。但是Order 8110.105 A及DO-254標準中都未具體提及如何驗證跨時鐘域時序問題[7]。而機載電子行業針對機載復雜電子硬件驗證活動是基于需求開展的。時鐘相關的需求一般只會描述各個時鐘的時鐘頻率、占空比、抖動等內容。針對這些時鐘需求的驗證一般通過時序仿真和靜態時序分析來進行覆蓋。因此基于需求的驗證及對應的驗證方法并不能有效發現跨時鐘域傳輸的問題。若未在設計活動中把概要設計或詳細設計中明確的跨時鐘域路徑反饋到衍生需求,或未在概要設計中明確描述跨時鐘路徑及同步策略方法,則針對跨時鐘域的驗證活動很容易被忽視。若把亞穩態問題帶到終端產品上去,則可能會使機載設備產生安全隱患。

因此,為了減少亞穩態問題發生概率,保證同步正確性,需要對跨時鐘域電路可能帶來的問題(同步器可靠性問題[8-9]、同步器結構問題[5,9-10]、跨時鐘域數據傳輸協議問題[5,11]、重匯聚[5,12-13]問題)進行全面驗證。而跨時鐘域信號驗證通常只能對多個實際電路進行長期測試以發現亞穩態隱患。但由于亞穩態造成的故障具有偶發性和不可重現性,極大增加了電子硬件的研制時間和驗證成本。如果直接使用國外專用CDC分析軟件(如spyglass,questa-CDC),在高安全等級機載電子電路驗證活動(例如DAL A,B)中需承擔工具成本及使用此工具所需的工具鑒定[14]活動所帶來的時間和經濟成本。另外,由于航空單粒子問題,常常要求使用三模冗余對跨時鐘域模塊進行加固設計[15],但目前的專用CDC分析軟件不支持三模跨時鐘同步電路驗證,容易出現錯誤的驗證結果,給驗證活動帶來問題。

針對此情況,本文對跨時鐘域同步可能存在的問題開展全面的驗證方法研究,提出了一套基于傳統FPGA(field programmable gate array)設計工具、功能仿真工具的RTL級驗證、板級加速測試和計算評估相結合的跨時鐘域驗證的解決方法。該方法有較強的實用性和適用性,能夠有效彌補專用工具缺陷,在機載電子設計早期發現并評估潛在的跨時鐘域傳輸風險,達到降低安全隱患的目的。

1 方法概述

完整的跨時鐘域同步電路驗證及可靠性分析方法主要包括RTL級驗證、板級加速測試、計算評估三部分,具體驗證流程如圖1所示。

圖1 驗證流程圖

RTL級驗證(包括結構分析、協議驗證、重匯聚驗證)旨在證明跨時鐘域信號傳輸所使用的同步方法功能正確,保證了單比特的使能信號或多比特的數據信號能傳輸到目的時鐘域,且不出現數據丟失。

板級加速測試通過構建加速亞穩態生成環境獲取亞穩態相關數據,并根據板級測試所得亞穩態相關數據計算出亞穩態參數值。

對于航空機載設備電路的設計,需對這些功能正確的同步電路的可靠性進行分析。為評估電路可靠性,需通過亞穩態參數計算同步電路的MTBF(mean time between failure)。從而最終判斷出設計中使用的同步策略是否可接受。

如果在RTL級驗證或計算評估中發現問題應及時提出問題報告,依據問題報告提出更改請求,增加對應的衍生需求。并依據需求修改對應的概要設計及設計代碼。最后將修改后的代碼重新進行RTL級驗證、板級加速測試、MTBF計算評估,如果發現問題應繼續提出問題報告并修改直至得到可接受的同步策略。

2 RTL級驗證

在電路RTL設計及功能仿真完成后,需要針對跨時鐘域信號進行結構分析、協議驗證和重匯聚驗證,作為靜態時序分析的補充。其中結構分析用以確保同步電路具有正確的同步電路單元,協議驗證對同步電路是否滿足相應的傳輸協議進行檢查,重匯聚驗證判斷數據在目的時鐘域內是否存在重匯聚問題。

2.1 結構分析

能夠將數據正確跨時鐘域傳輸的同步電路(如握手協議、異步FIFO等同步電路)都包含至少連續2級且中間無組合邏輯運算的寄存器級聯的結構單元,本文把其定義為同步單元(或電平同步電路),如圖2所示。

圖2 同步單元

結構分析主要確定跨時鐘域路徑上是否含有該同步單元的結構以降低亞穩態傳輸概率,進而確定設計所采用的同步電路結構或方法,可通過使用常用的EDA工具來快速分析。如在Xilinx的Vivado開發環境下,對RTL級代碼進行綜合后可得到原理圖,在原理圖上同時選定不同時鐘域的時鐘信號,便可快速定位出數據跨時鐘域交互模塊。定位出CDC設計模塊后,便可分析該模塊所采用的同步策略、模塊是否含同步單元、同步路徑是否含組合邏輯。如果沒有正確的同步電路結構,則說明需要增加合適的同步電路使數據正確傳輸。

2.2 協議驗證

電路具有正確的同步電路結構,并不能保證該數據可以正確地傳輸到目的時鐘域,還需滿足相應的傳輸協議。為快速驗證電路是否符合傳輸協議,可使用傳統的仿真軟件,并在基于斷言的仿真測試平臺上進行動態仿真。為模擬出真實環境,保證數據在任何情況下都滿足傳輸協議,動態仿真的輸入激勵須覆蓋需求規定的所有情況。在進行動態仿真時,如果傳輸的數據在某一時刻不滿足相應的傳輸協議,則斷言宣告失敗,說明該數據不能被正確地跨時鐘域傳輸,需重新修改同步策略直至驗證通過;如果斷言成功,則表示該同步電路能正確地將數據傳輸到目的時鐘域。

本文以適用于三模冗余的多周路徑(multi-cycle-path,MCP)傳輸電路為例,說明CDC電路的傳輸協議驗證過程。適用于三模的MCP電路如圖3所示,發送電路在更新數據tx-data的同時發出脈沖信號tx-en。tx-en經過結繩模塊后變為電平信號en-tx-clk。q2-A為同步后的en-tx-clk信號,q2-B、q2-C則為另外2個冗余電路的電平同步后信號。3個信號經過voter表決后通過邊沿檢測生成en-rx-clk信號,并把其作為data-sending的讀時鐘域接收寄存器的使能信號。

圖3 多周路徑傳輸路徑電路

假設發送時鐘域中的脈沖信號間隔為nT1(T1代表發送時鐘周期),考慮到亞穩態的情況下,接收時鐘域中的數據信號必須經過1個發送時鐘周期和至少4個接收時鐘信號的上升沿,才能保證該組數據的正確傳輸,即nT1>4T2+T1(T2代表接收時鐘周期)。因此,使能信號tx-en的間隔應滿足公式(1)。

(1)

式中:Ttx-en-1表示tx-en信號下降沿到下一個tx-en上升沿之間包括的最少發送時鐘周期,在此期間tx-en應保持低電平。

發送數據tx-data在整個數據發送過程中均應保持穩定,協議可以表示為公式(2)。

(2)

Tdata表示發送數據tx-data需要在多少個發送時鐘周期內保持穩定。

根據上述分析,使CDC數據正確傳輸發送數據和脈沖信號間隔斷言表示如下,仿真波形如圖4所示。

property DATA-SEND;

endproperty:DATA-SEND

property TX-EN;

endproperty:TX-EN

圖4 電路斷言波形圖

2.3 重匯聚驗證

當數據經過不同的同步電路后,無法保證同步電路的路徑、環境(如時鐘相位、寄存器電壓、電磁干擾)及器件工藝參數完全相同,因此經過不同同步電路的傳輸數據可能會出現不可預測的提前或延遲。在目的時鐘域內,如果經過不同跨時鐘域路徑傳輸的數據進行組合邏輯運算,可能會造成整個電路的功能錯誤。為避免電路出現無有效保護的重匯聚運算,須對設計進行亞穩態重匯聚驗證。重匯聚驗證可基于傳統仿真工具,通過隨機注入延遲來判定電路對亞穩態的容忍度。如果進行延遲注入后仿真結果與預期一致,則表明該電路符合需求。與協議驗證一樣,重匯聚驗證需要仿真測試平臺的輸入激勵覆蓋需求規定的所有情況。

下面描述的亞穩態注入方案與已有研究的注入方法相比[12]主要區別是固定了注入隨機延遲的變化頻率,注入隨機延遲的時機由狀態機進行控制。該方法保證了進行一次使能信號傳輸時,隨機延遲的注入不會突然變化而導致單比特使能信號縮短。相比于已有研究論文,其能應用在如對接收使能信號有長度要求(一般為2個接收時鐘長度)的三模冗余電路。需注意的是,一般情況下在目的時鐘域的重匯聚是不允許的,但在抗單粒子翻轉使用的三模冗余設計中,不同同步路徑會在三模投票電路處出現計劃內的匯聚點[13],一些專用的跨時鐘域分析工具如Questa CDC可能誤報該錯誤。使用本文的亞穩態注入方法,可以對該投票電路功能在翻轉場景下是否失效進行動態判別。避免一些靜態跨時鐘域分析工具直接對該匯聚現象報錯的情況出現。

圖5 亞穩態注入電路

如圖5所示,亞穩態注入位置選取在跨時鐘模塊信號傳輸完成后三模冗余投票之前的節點,本設計使用狀態機確保3個亞穩態注入點注入亞穩態時,該信號不會被截短導致三模冗余驗證不能通過。且在動態仿真過程中,為保證驗證的全面性,需要收集功能覆蓋率情況。確認在驗證過程中覆蓋了亞穩態的一路注入、兩路同時注入、三路同時注入的情況。使驗證活動更為完整可靠。

協議驗證和重匯聚驗證可以使用相同的輸入激勵,因此可以在一次仿真驗證過程中同時檢查電路的傳輸協議和重匯聚問題。

3 加速測試和可靠性分析評估

本節通過構建加速亞穩態的生成和采集電路獲取亞穩態相關數據,并根據板級測試所得亞穩態相關數據計算出亞穩態參數值,使用該亞穩態參數值,就可以計算出電路全部跨時鐘域路徑的TMTBF(平均無故障時間)值。

3.1 加速測試方法

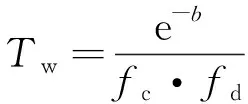

跨時鐘域傳輸時通過單觸發器后發生亞穩態的概率常使用公式(3)進行評估[15]:

(3)

式中:tτ為亞穩態解決時間,即預留給觸發器使其從亞穩態恢復到穩定的時間;τ為觸發器的亞穩態解析時間常數;Tw為亞穩態窗口時間常數;fc為設計的接收時鐘頻率;fd為設計的異步信號變化頻率,即輸入的異步信號翻轉率。

對于具體的電路設計來說,參數fc,fd和tτ已知。因此要對MTBF進行計算的關鍵是確定觸發器的亞穩態參數Tw和τ。

對公式(3)兩邊取自然對數,得到如下公式:

(4)

易知方程(4)是一條直線,其自變量為亞穩態決斷時間tτ,因變量為ln(TMTBF),直線斜率k為1/τ,截距為-ln(Tw·fc·fd)。得到τ的計算公式,如公式(5)所示

(5)

得到Tw的計算公式,如公式(6)所示

(6)

所以可以通過改變tτ,測得到不同tτ下的TMTBF值,擬合出tτ-ln(TMTBF)直線,從而算出Tw和τ。目前半導體器件的亞穩態參數測試方法都是基于該測試理論。

基于該測試理論,FPGA芯片廠商推薦使用的亞穩態參數的測試電路為半周期測試電路[8],通過改變時鐘周期的頻率改變tτ。本文推薦使用器件的時間管理模塊以實現tτ更精確的控制,以便獲得更多更廣泛的數據和更高的測試效率。亞穩態參數測試需采集大量的亞穩態數據,為計算TMTBF值,需測得亞穩態發生次數和其對應的時間。在設計亞穩態采集電路時,測試前規定亞穩態采集停止次數S。開始亞穩態采集時,計時計數器開始計時,當亞穩態采集次數計數器達到亞穩態采集停止次數S時,使計時計數器停止,并把該時間T記錄下來。S/T即可計算得出采集到2次亞穩態的平均時間間隔。通過改變tτ,經過不同次的測試計算獲得對應的TMTBF值。需注意的是,測試時要使亞穩態采集點在FPGA上的位置盡可能分散。

為方便在使用某些器件時進行跨時鐘域的可靠性評估,本文對6種典型FPGA芯片的亞穩態相關參數進行采集計算。在不同采樣點多次規定次數進行亞穩態采樣后,對數據點進行最小二乘法直線擬合,繪制出6種典型芯片亞穩態參數采集Matlab圖(圖中tτ和TMTBF的單位為ps)如圖6所示。

圖6 不同芯片亞穩態參數采集圖

對多組數據擬合成直線,計算得到的亞穩態參數值如表1所示。

表1 被測芯片亞穩態參數值

3.2 計算評估

不同的同步策略解決亞穩態的核心原理都是增加亞穩態的解決時間,核心電路為同步單元結構。其中雙級同步單元的MTBF計算公式如公式(1)所示。

當雙級同步單元不能滿足MTBF的需求時,可以提高同步單元的串聯級數來增大亞穩態的實際解決時間。多級觸發器風險評估公式(7)[16]

(7)

式中,M為一個同步單元中寄存器個數。

FPGA整體的同步電路的MTBF值由設計中所有的跨時鐘域同步單元決定。一個同步單元失效率F(Pn)為1/TMTBF(M),Pn表示第n個同步單元。整個設計由亞穩態導致的失效率是把所有同步鏈的失效率相加,如公式(8)所示。假設FPGA整體設計含N個同步單元,其MTBF計算公式如公式(9)~(10)所示:

在計算跨時鐘域同步電路可靠性時,需關注兩點:第一是同步單元數目的確定;第二是對數據變換速度fd的確定約束。在確定同步單元數目時,要注意每種同步電路含有的同步單元的個數不同,同步電路與其含有的同步單元不是一一對應關系(如握手同步策略,異步FIFO同步策略)。在確定公式使用fd數值時,如果數據變換速度fd未知,一般fd可按照發送時鐘域的時鐘頻率fw估計,這樣計算出的MTBF值可認為是保守的可靠性值。但在某些場景可對fd進行更精確約束時,建議使用更精確的方法約束fd最高變換頻率,以求得更符合實際的MTBF值。下面舉例說明如何確定計算MTBF所需的同步單元的個數N和fd的值。假設一個電路設計中含有一個異步FIFO,其指向數據存儲器的地址采用二進制碼編寫。其中,異步FIFO中的寫滿標志判斷需要把讀地址同步到寫時鐘域,讀空標志需要把寫地址同步到讀時鐘域[17]。當讀寫地址碼進行跨時鐘域傳輸時,需把二進制編碼轉化為格雷碼。若地址總線位寬為W,由于讀寫地址都要同步,因此該異步FIFO中具有2W個同步單元,即N=2W。確定N之后,需確定約束每個同步單元的fd。對于地址總線為W的異步FIFO,存在2W個寫地址,其中最高位為狀態位,2W-1個地址對應實際存儲器的地址。自然二進制碼轉換成二進制格雷碼,其法則是保留自然二進制碼的最高位作為格雷碼的最高位,而次高位格雷碼為二進制碼的高位與次高位相異或,而格雷碼其余各位與次高位的求法相類似。經分析計算,第n位格雷碼最快變換頻率如公式(11)所示。

(11)

以W=4為例,代入公式(11),可得到各同步單元最快變換頻率表。

表2 4位格雷碼同步單元最快變換頻率表

依據表2中的各同步單元最快變換頻率fd,便可以使用公式(7)進行單個同步單元TMTBF計算。之后使用公式(10)進行該異步FIFO的TMTBF計算。

通過計算所得的MTBF值即可判斷同步電路是否符合可靠性要求。如不符合,需修改同步電路設計,增加相應同步單元內寄存器的級數。

4 結 論

本文介紹了一種適用于機載復雜電子硬件的基于傳統工具的RTL級驗證、板級加速測試和計算評估相結合的跨時鐘域驗證及可靠性評估方法,可以在設計早期發現三模場景和普通場景下的跨時鐘域信號的隱患。對于含跨時鐘域同步電路的電子設計,電路驗證應關注跨時鐘域路徑上的同步電路結構,數據傳輸要求,目的時鐘域重匯聚等問題。

對于應用在DAL A/B的機載復雜電子硬件的跨時鐘域同步電路,則需在RTL級驗證通過后,對亞穩態參數未知的芯片進行實際板級加速測試,最后根據測試結果計算評估其TMTBF值,判斷同步器的可靠性是否符合需求。另外,本文提供了Altera和Xilinx公司的共6款不同特征尺寸的亞穩態參數測試參考值,使驗證人員能更方便快捷地進行該器件的跨時鐘域可靠性評估計算。建議該方法可作為靜態時序分析工作的補充,共同完成對電路的時序分析工作。