2GHz~18GHz寬帶有源巴倫芯片設計

楊楠,楊旭達

(中國電子科技集團第十三研究所,河北 石家莊 050051)

0 引 言

伴隨著當今社會信息化的快速發展,無線通信技術已經廣泛應用在各個領域,如通信網絡、定位系統、無線局域網、藍牙等等,這些已經成為生活中不可或缺的部分。射頻前端是無線通信系統中極其重要的組成部分,它往往需要平衡式電路來提升整個系統的性能。而巴倫(balun)結構,即平衡—非平衡轉換器,可以實現信號的單端輸入到差分輸出的轉換或者實現差分輸入到單端輸出的轉換,并完成阻抗匹配。通常在射頻前端系統的接收通道內需要射頻信號的單端輸入轉化為平衡輸出,而發射路通道需要射頻信號實現差分輸入到單端輸出的信號轉換。本文主要研究信號單端到差分的信號轉換有源巴倫電路,它在單平衡、雙平衡倍頻器、混頻器和移相器中都有一定的應用,其性能的好壞對系統整體指標有較大影響。

巴倫可以分為無源巴倫和有源巴倫兩種。通常無源巴倫電路是利用微帶線、同軸線等結構的耦合、移相實現信號不平衡—平衡之間的轉換。無源巴倫按其實現形式可粗略分為三類:(1)使用集總元器件形式實現轉換,該形式通常適用于窄帶、低頻電路;(2)使用螺旋變壓器形式實現轉換,該種形式應用于低頻和超高頻電路中,有一定的損耗;(3)分布參數形式實現轉換,該形式是微波毫米波電路中常用的形式之一,具有較好的幅值平衡性和相位平衡性,但工作帶寬有一定的限制性。總之,無源巴倫電路結構簡單,無直流功耗,但缺點也很顯著,如有較大插入損耗、端口隔離度低、工作頻帶窄,尤其是低頻段由于面積大不易集成等。

有源巴倫電路,通常是利用晶體管特定的工作狀態完成射頻信號的轉換,不僅具有良好的幅度和相位平衡性,還有一定的增益、較高的端口隔離度,便于單片集成設計,提高系統的集成度。與無源巴倫電路相比,有源巴倫更容易實現更寬頻段范圍內的信號轉換。有源巴倫電路可廣泛應用于有源倍頻器、有源數控移相器、低噪聲放大器、有源混頻器等微波電路的集成化設計中。比如在混頻器中,可以采用有源巴倫實現單端到雙端的轉換,中頻輸出端采用有源巴倫等實現雙端到單端的轉換,極大地提高混頻器的帶負載能力和芯片的集成度。常見有源巴倫電路有偽差分型有源巴倫、源級/漏極型有源巴倫和共源/共柵型有源巴倫等,不同的電路結構具有各自的優缺點,但目前可查的有源巴倫電路大多都采用了CMOS工藝或混合集成工藝設計加工制作,無法實現系統中GaAs芯片級的集成一體化設計。

本文設計的2 GHz~18 GHz寬帶有源巴倫芯片,采用0.13 μm GaAs pHEMT成熟工藝設計加工并流片,其幅度平衡性和相位平衡性優良,且有一定的小信號增益和功率輸出能力;后續可以考慮將該結構的有源巴倫電路應用到至混頻器、移相器等電路一體化設計中,改善系統性能,提升系統集成度。

1 有源巴倫設計

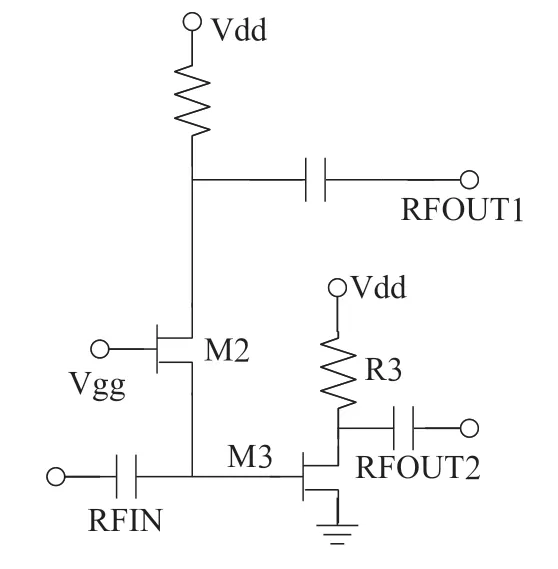

文中提到的共源/共柵巴倫電路,電路結構如圖1所示。該有源巴倫電路包含兩個部分,分別是晶體管M3構成的共源放大級和晶體管M2構成的共柵放大級。射頻信號分別輸入到晶體管M2的源級和晶體管M3的柵極,經過信號轉化,分別從晶體管M2漏極、晶體管M3漏極輸出。其中射頻信號經過共源放大級時相位改變180°,經過共柵放大級射頻信號相位保持不變。假設晶體管M2、M3跨導分別為gm、gm。在不考慮二級效應的條件下,那么共源放大級增益可簡化為:Av=-gmR3,共柵放大級增益可簡化為:Av=gmR2。共柵放大級的輸入阻抗較小,而共源放大級的輸入阻抗大,可通過合理的設計優化電路元器件尺寸使得兩平衡輸出端口小信號增益趨于一致,相位差值為180°。共源/共柵有源巴倫具有幅度平衡度好、直流功耗小、電路結構簡單、容易集成設計等優點,但是隨著頻段的升高,電路的寄生參數影響越來越大,共源/共柵巴倫電路相位差會越來越大,很難實現較高頻率范圍內寬帶的良好匹配,這大大限制了該結構有源巴倫電路的使用。

圖1 共源/共柵有源巴倫

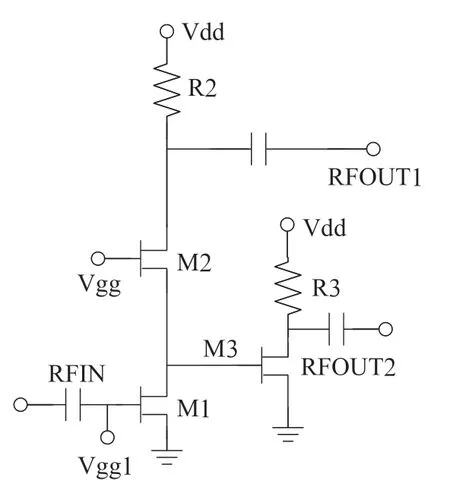

C3(combined cascode-cascade)有源巴倫,是在共源/共柵巴倫的基礎上進行改進設計的電路結構,原理圖如圖2所示。該結構的有源巴倫電路包含兩個射頻通路。晶體管M1為兩通路共用的輸入放大級,通路一,是由晶體管M1和M2構成共源共柵(cascode)放大路,射頻信號路徑為RFIN→RFOUT1;通路二,是由晶體管M1和M3構成兩級共源級聯放大級,射頻信號路徑為RFIN→RFOUT2。晶體管M1、M2組成的共源共柵放大級,和兩晶體管之間的匹配電路用于擴展工作頻率帶寬,同時改善兩平衡輸出端口之間的相位平衡性;晶體管M1、M3尺寸及該通路中匹配電路元器件值的大小,主要用于改善有源巴倫電路的幅度平衡性。相比共源/共柵有源巴倫電路,C3有源巴倫提供更寬的工作頻段,具有更好的幅度平衡性和相位平衡性,兩輸出端口間的隔離度更高。

圖2 C3有源巴倫

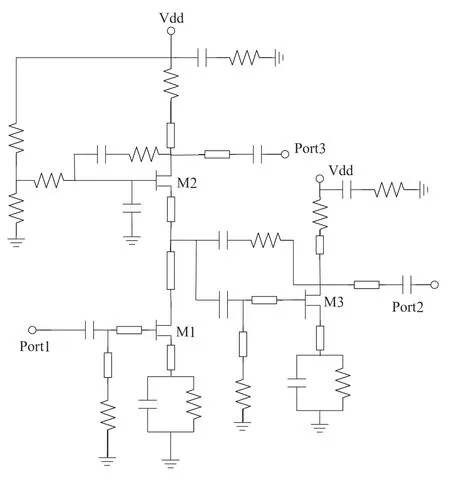

本文設計的有源巴倫芯片基于C3有源巴倫電路,在電路結構上進行進一步的改進優化,原理圖如圖3所示。該有源巴倫電路以單電源方式來實現,無須外部提供柵壓,只需要提供漏極工作電壓5 V,實現信號單端到差分的轉換;單電源供電的有源巴倫電路在系統使用中減小裝配工序和調試工作,大大提高系統的可靠性。晶體管M1、M3的柵偏置電壓均通過電容電阻并聯到地自偏結構來實現,無須外加;晶體管M2工作柵壓由電源電壓Vdd通過電阻分壓實現,此處考慮引入的額外功耗,分壓電阻總值在5 KΩ以上。晶體管M2、M3的柵級與漏級之間分別引入電容電阻負反饋電路,不僅可以優化端口駐波,還大大提高電路了穩定性;射頻輸入端口的匹配電路,對晶體管M1的輸入阻抗進行匹配設計,優化電路的輸入駐波;晶體管M1、M2間電感的感量及Q值大小,對擴展電路工作帶寬及兩輸出端口的幅度平衡度有較大影響;晶體管M1、M3間的匹配電路和兩輸出端口的匹配電路、漏極的扼流電感和電阻等元器件均可以改善兩輸出端口的相位平衡度及輸出駐波。通過各晶體管尺寸及工作偏置狀態、電路中各個元器件尺寸的優化設計,可在寬帶工作頻率范圍內實現一定的小信號增益,并實現較好的幅度平衡性和相位平衡性。

圖3 2 GHz~18 GHz有源巴倫原理圖

本文設計的寬帶有源巴倫電路以工作頻段范圍內兩平衡端口小信號增益、兩輸出端口幅度差、相位差、輸出P1 dB、直流功耗及電路的穩定性等特性為優化目標,選擇合適尺寸的M1、M2、M3晶體管,實現射頻信號在工作頻段范圍內良好的幅度平衡性和相位平衡性,實現信號單端到差分的轉換,并具有一定的小信號增益和功率輸出能力。

2 仿真與測試結果

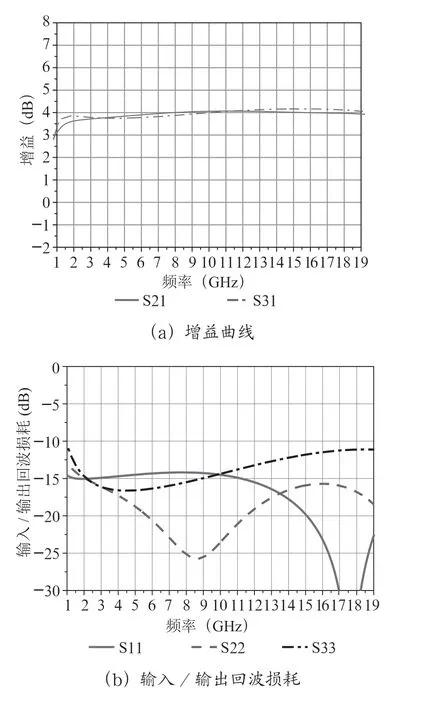

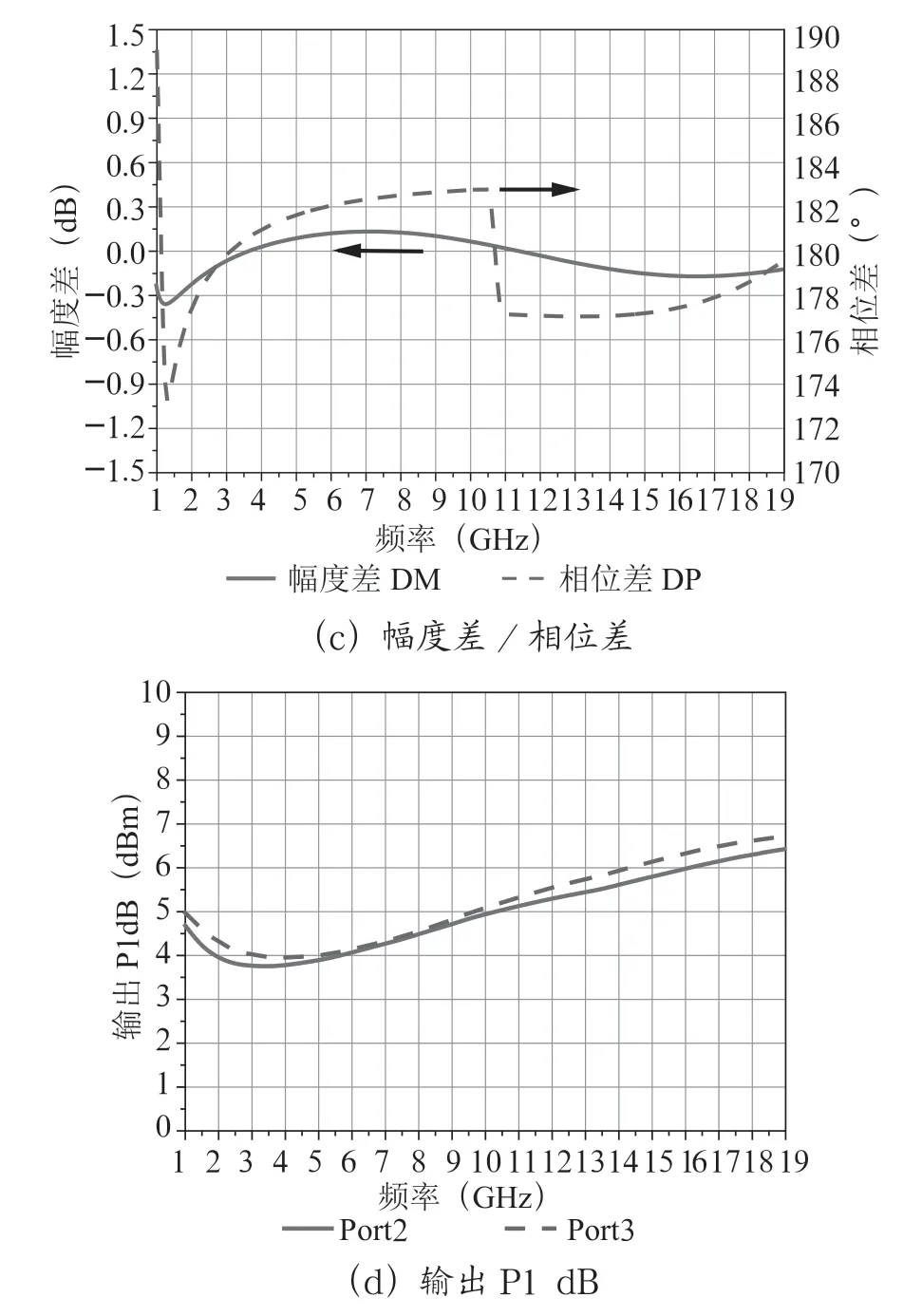

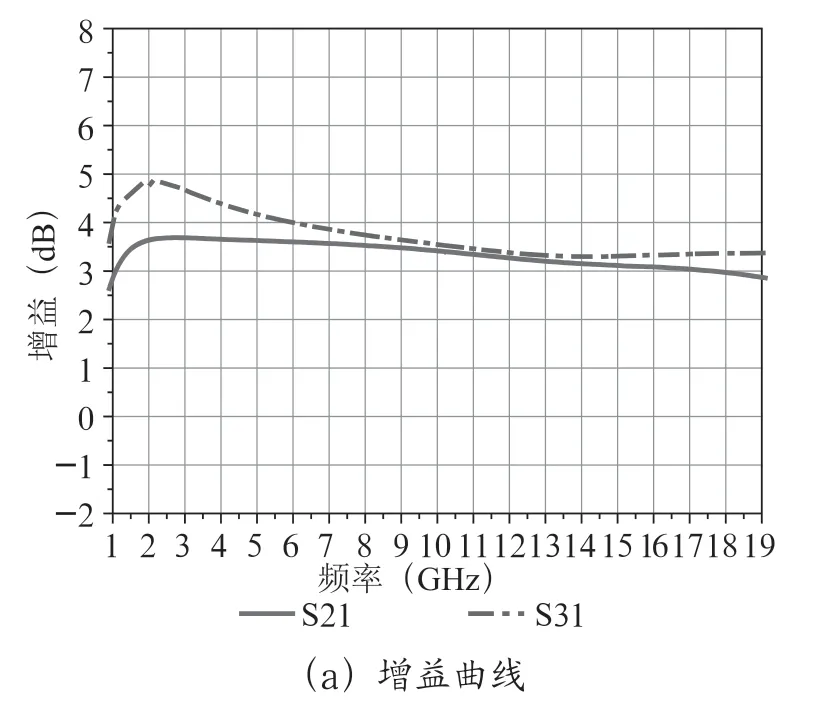

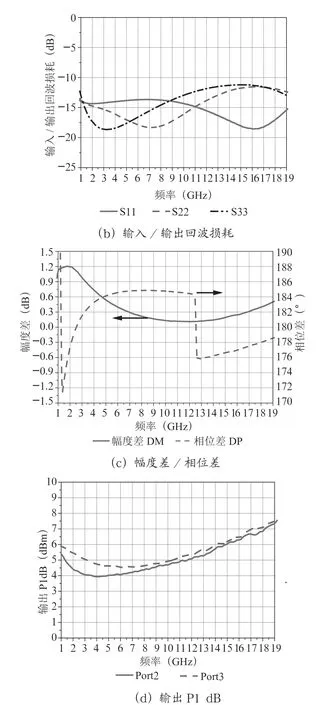

基于上述設計思路及方法,本文采用0.13 μm GaAs pHEMT成熟工藝,設計并流片一款工作于2 GHz~18 GHz寬帶有源巴倫芯片。綜合考慮工藝推薦的晶體管工作偏置、工作帶寬、輸出P1dB及電路功耗等技術指標及芯片的可靠性等,最終確定晶體管M1、M2、M3尺寸分別為4 μm×30 μm、4 μm×40 μm和4 μm×40 μm;使用電磁仿真軟件中小信號仿真控件、大信號仿真控件及優化控件等,對有源巴倫電路進行原理圖和版圖優化仿真設計。最終版圖仿真曲線如圖4所示,在2 GHz~18 GHz頻率范圍內,有源巴倫電路輸入端口到輸出兩端口小信號增益S21、S31均為4 dB左右,幅度差±0.3 dB以內,增益平坦度較好;輸入、輸出回波損耗均大于11 dB,兩輸出端口相位差為180°±3°以內,輸出P1 dB功率值均為4 dBm,電路直流功耗5 V/50 mA,設計指標滿足要求。

圖4 2 GHz~18 GHz寬帶有源巴倫芯片仿真曲線

電路經過工藝加工流片、劃片、載體裝配及矢網測試,2 GHz~18 GHz寬帶有源巴倫芯片實測曲線如圖5所示。其中在工作帶寬范圍內,輸入端口到輸出兩端口小信號增益S21為3.0 dB~3.5 dB、負斜率0.5 dB;小信號增益S31為3.5 dB~4.7 dB、增益平坦度略差;兩射頻端口的幅度差最大值1.2 dB@2 GHz,6 GHz~18 GHz范圍幅度差小于0.4 dB;實測幅度差值與仿真值在2 GHz~6 GHz頻段內差別較大,主要是小信號增益S31在該頻段內實測值偏大,且增益曲線趨勢與仿真曲線不一致造成的,后續考慮對該指標進行擬合及電路優化改版設計;輸入、輸出回波損耗全頻帶內均優于12 dB,兩輸出端口相位差180°±5°以內,相位差實測值略大于仿真值,但曲線變化趨勢一致;輸出P1 dB大于4 dBm,直流功耗約5 V/50 mA。有源巴倫芯片版圖如圖6所示。

圖5 2 GHz~18 GHz寬帶有源巴倫芯片測試曲線

圖6 2 GHz~18 GHz寬帶有源巴倫芯片版圖

3 結 論

本文講述一種寬帶有源巴倫芯片設計方法,設計并流片一款工作頻率覆蓋2 GHz~18 GHz的寬帶有源巴倫芯片,芯片尺寸1.4 mm×1.9 mm×0.07 mm,集成度高。經裝配測試,有源巴倫芯片在工作頻段范圍內,兩平衡輸出端口小信號增益分別為3.0 dB~3.5 dB、3.5 dB~4.7 dB,幅度差小于1.2 dB,相位差180±5°以內,輸出P1 dB大于4 dBm,直流功耗約為5 V/50 mA。此結構的寬帶有源巴倫結構可應用于超寬帶有源倍頻器、有源混頻器等電路集成設計中。