基于動態加載的FPGA 在線更新方法

邵龍

(中國電子科技集團公司第十研究所,四川成都 610036)

綜合化電子系統定義了通用信號處理模塊(SPM)、通用數據處理模塊(DPM)等6 類通用功能模塊,每一類模塊都包括模塊支持單元(MSU)、處理單元(PU)、模塊物理接口(MPI)等組成單元[1-6]。通用信號處理模塊的處理單元由典型信號處理器DSP/FPGA 組成,單獨由FPGA 組成處理單元的信號處理模塊就形成了FPGA 型信號處理模塊。相較于DSP,FPGA 具備硬件并行優勢,擁有更高的運算能力[7-9],提供更豐富的I/O 資源,因此,FPGA 型信號處理模塊綜合化電子系統的應用廣泛。

FPGA 程序更新通常采用FPGA 廠家提供的基于邊界掃描方式對外掛FLASH 芯片進行編程[10],但該方法操作繁瑣、效率低[11-12]。采用在線更新的方式,可以解決FPGA 程序維護更新效率低的問題。目前,FPGA 在線更新有如下兩種常規方案。常規方案一:FPGA 功能程序內含FPGA 在線更新模塊,通過該模塊實現將FPGA 程序更新到FPGA 外掛存儲器中[13-15]。常規方案二:FPGA 程序存儲在其他處理器(通用信號處理模塊中一般為DSP)外掛存儲器中,通過DSP 實現FPGA 在線更新[16-18]。

1 現有解決方案的局限性

現有的一些方案中有如下缺點:常規方案一中,由于FPGA 在線更新模塊內置在FPGA 功能程序中,不僅增加功能應用與在線更新的耦合、占用寶貴的FPGA 內部資源,而且如果更新失敗,還將導致FPGA在線更新功能完全失效,只能通過JTAG 燒寫才能恢復。常規方案二中,由于FPGA 程序存儲在DSP 外掛存儲器中,FPGA 的加載就只能采用被動加載模式,加載速度比主動加載慢;另外,在沒有DSP 的FPGA型信號處理模塊中,常規方案二根本無法實現。

針對現有FPGA 在線更新技術中存在的不足,基于綜合化電子系統中每個模塊都包括模塊支持單元(MSU),文中提供一種綜合化電子系統中加載速度快、松耦合、不依賴DSP 的基于動態加載的FPGA在線方法。

2 FPGA在線更新電路

如圖1 所示,在綜合化電子系統中,基于動態加載的FPGA 在線更新電路包括電連接在綜合化系統與FLASH 芯片之間的MSU 和FPGA,其中,MSU 包含處理器系統PS 和可編程邏輯PL,PL 內置PSPLIF 總線讀寫器、FPGA 程序加載控制器和FLASH 塊選擇器。PS 一端通過控制總線接入綜合化系統,另一端通過PSPLIF 連接PL 的PSPLIF 總線讀寫器。PL 的FPGA 程序加載控制器通過一根輸出和兩根輸入離散線連接FPGA 的PROG、INIT 和DONE 管腳,PL 的FLASH 塊選擇器通過n根地址控制線連接FLASH 高n位地址管腳。FPGA 一端通過數據總線接入綜合化系統,另一端通過FPGA 并行加載接口BPI 連接FLASH 的控制接口、數據接口和除高n位地址管腳以外的地址接口。

圖1 FPGA在線更新電路框圖

在線更新時,PL 的FLASH 塊選擇器選中FPGA在線更新程序所在的FLASH 塊,通過PL 的FPGA 程序加載控制器動態加載FPGA 在線更新程序。

FPGA 在線更新程序內部電路包括包收發器、包解析器和包燒寫器,包收發器通過數據總線接入綜合化系統數據總線,包燒寫器通過BPI 與FLASH 連接。包收發器用于如下情況:1)當數據總線有FPGA程序數據包到達時,包收發器用于接收數據包并將數據包輸出到包解析器;2)當接收到包解析器輸出的包傳輸結果時,包收發器用于將包傳輸結果輸出到綜合化系統數據總線;3)接收到包燒寫器輸出的包燒寫結果時,包收發器用于將包燒寫結果輸出到綜合化系統數據總線。包解析器用于當包收發器輸入FPGA 程序更新數據包時,檢查包的完整性和確定傳輸結果的有效性,并輸出傳輸結果到包收發器,如果完整有效,提取出待燒寫地址、待燒寫長度和待燒寫數據,并輸出到包燒寫器。包燒寫器用于當包解析器輸入待燒寫地址、待燒寫長度和待燒寫數據時,將長度為待燒寫長度的待燒寫數據通過BPI 寫入FLASH 的待燒寫地址中,校驗燒寫結果,并輸出燒寫結果到包收發器。

3 FPGA在線更新方法

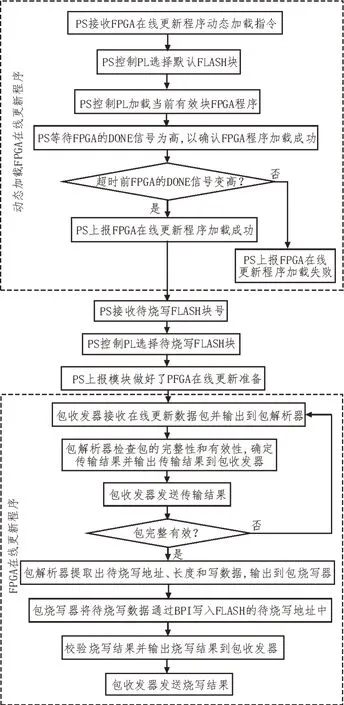

如圖2 所示,綜合化電子系統中基于動態加載的FPGA 在線更新方法主要包括動態加載FPGA 在線更新程序和執行FPGA 在線更新程序實現FPGA在線更新,細分為5 個步驟:

圖2 FPGA在線更新方法流程圖

1)FPGA 在線更新電路通過PS 接收控制總線上動態加載指令,將默認塊號(FPGA 在線更新程序所在的塊)寫入PL 的FLASH 塊選擇器中,選擇FPGA在線更新程序所在的FLASH 塊為當前有效塊;

2)PS 通過PSPLIF 總線讀寫器控制PL 的FPGA程序加載控制器輸出低電平脈沖到FPGA 的PROG管腳,啟動FPGA 加載流程,加載FPGA 在線更新程序,并通過判斷FPGA 的DONE 信號,確認FPGA 在線更新程序加載成功;

3)PS 通過控制總線上報FPGA 在線更新程序加載成功,接收待燒寫FLASH 塊號,通過PSPLIF 總線讀寫器將待燒寫FLASH 塊號寫入PL 的FLASH 塊選擇器,選擇待燒寫FLASH 塊為當前有效塊,并通過控制總線上報模塊做好了FPGA 在線更新準備;

4)FPGA 的包收發器接收在線更新數據包,將包輸出到包解析器,包解析器檢查包的完整性和確定傳輸結果的有效性,并輸出傳輸結果到包收發器,如果完整有效,提取出待燒寫地址、待燒寫長度和待燒寫數據,并輸出到包燒寫器;

5)包收發器發送傳輸結果,包燒寫器將長度為待燒寫長度的待燒寫數據通過BPI 寫入FLASH 的待燒寫地址中,校驗燒寫結果,輸出燒寫結果到包收發器,并發送燒寫結果。

其中,步驟1)~3)在MSU 中執行,實現FPGA 在線更新程序的動態加載和待燒寫扇區的選取;步驟4)、步驟5)屬于FPGA 在線更新程序,在FPGA 中執行,實現待更新FPGA 程序的接收和燒寫。

4 工程應用及性能對比

基于動態加載的FPGA 在線更新電路及方法已應用在某綜合化系統FPGA 密集型信號處理模塊(SPM-F)的FPGA 在線更新中。

FPGA 密集型信號處理模塊硬件框圖如圖3 所示。MSU 采用TI 公司的C2000 系列處理器C28235作為PS,選用XILINX 公司的Spartan 系列可編程邏輯器件XC3S1400 作為PL。C28235 的一端通過CAN總線接入綜合化系統控制總線,另一端通過外部接口XINTF 連接XC3S1400。FPGA 的一端通過SRIO總線接入綜合化系統數據總線,另一端通過BPI 與FLASH 連接。XC3S1400 通過一根輸出離散線與FPGA 的PROG 管腳連接,XC3S1400 通過兩根輸入離散線與FPGA 的INIT 和DONE 管腳連接,XC3S1400通過3 根地址控制線連接FLASH 高3 位地址管腳,3根地址控制線將FLASH 分成塊號為0~7 的8 塊,FPGA 在線更新程序放在塊號為7 的FLASH 塊中。

圖3 FPGA密集型信號處理模塊硬件框圖

系統硬件架構框圖如圖4 所示。FPGA 密集型信號處理模塊通過SRIO 分別接入主備SRIO 網絡,通過CAN 分別接入主備CAN 網絡。I/O 模塊通過CAN 總線發送動態加載指令至FPGA 密集型信號處理模塊C2000,C2000 將塊號7 寫入XC3S1400 的FLASH 塊選擇器中,選擇FPGA 在線更新程序所在的FLASH 塊為當前有效塊;C2000 通過XINTF 控制XC3S1400 的FPGA 程序加載控制器,加載FPGA 在線更新程序,并通過判斷FPGA 的DONE 信號,確認FPGA在線更新程序加載成功。C2000通過CAN總線向I/O 模塊上報FPGA 在線更新程序加載成功,并接收I/O 模塊通過CAN 總線下發的待燒寫FLASH 塊號,通過XINTF 將待燒寫FLASH 塊號寫入XC3S1400的FLASH 塊選擇器中,選擇待燒寫FLASH 塊為當前有效塊,并通過CAN 總線向I/O 模塊上報:模塊做好了FPGA 在線更新準備。

圖4 系統硬件架構框圖

FPGA 在線更新程序的FPGA 的包收發器通過SRIO 接收I/O 模塊發送的在線更新數據包,并將包輸出到包解析器,包解析器檢查包的完整性和確定傳輸結果的有效性,并輸出傳輸結果到包收發器,如果完整有效,提取出待燒寫地址、待燒寫長度和待燒寫數據,并輸出到包燒寫器;包收發器通過SRIO 向I/O模塊發送傳輸結果,包燒寫器將長度為待燒寫長度的待燒寫數據通過BPI 寫入FLASH 的待燒寫地址中,校驗燒寫結果,輸出燒寫結果到包收發器,包收發器通過SRIO 向I/O 模塊發送燒寫結果。

基于動態加載的FPGA 在線更新方法與常規方案一和常規方案二的性能對比如表1 所示。相對于常規方案一,基于動態加載的FPGA 在線更新方法具有功能應用與在線更新解耦、不占用功能應用的FPGA 處理資源、更新失敗時不需要采用JTAG 下載等優勢。相對于常規方案二,基于動態加載的FPGA在線更新方法具有加載速度快,不需要額外處理器的優勢。

表1 性能對比

5 結論

文中提出了一種基于動態加載的FPGA 在線更新方法,不僅通過避免需要增加DSP 才能實現FPGA在線更新,降低了成本和系統復雜度,而且通過避免在線更新模塊內置于FPGA 功能應用程序中,減少了系統耦合和處理資源的占用。多個大型綜合化系統的應用實踐表明,該方法是一種在綜合化電子系統中實現FPGA 在線更新的有效方法。