SiC MOSFET 器件單粒子燒毀仿真分析

李林歡,曹榮幸,黃 鑫,孟 洋,劉 洋,韓 丹,李紅霞,鄭 澍,曾祥華,薛玉雄

(揚州大學 電氣與能源動力工程學院,揚州 225127)

0 引言

更高效率以及更高功率密度的功率器件是半導體技術發展的重要方向之一。近年來,新興的寬禁帶半導體材料以其優越的特性為半導體功率器件技術領域帶來了新的發展動力,其中SiC 的禁帶寬度是Si 的2 倍以上,擊穿場強是Si 的10 倍多,導熱系數約是Si 的2.5 倍,飽和電子漂移速度是Si 的2 倍。這些特性使得SiC MOSFET 器件具有耐高壓、高頻率、高功率密度等優勢,在一些應用領域開始逐步取代Si 基功率器件。

在航天、核工業領域的應用中,SiC MOSFET器件(文中簡稱“器件”)會受到輻射環境的影響。相比Si 基器件,SiC MOSFET 器件具有較強的抗總劑量能力。但是,SiC MOSFET 器件對單粒子效應比較敏感,尤其是在截止態時由于粒子入射導致的大電流,器件可能發生導致永久性破壞的單粒子燒毀(SEB)。地面單粒子試驗是研究器件單粒子效應的常用技術手段,可以較為精準地評估器件的單粒子效應閾值電壓,但是試驗資源及成本限制常導致輻照條件及器件偏置等數據點數量有限。而采用TCAD 并結合試驗結果驗證優化的單粒子效應建模仿真可以靈活調節輻照條件和器件偏置條件等參數,獲得更為全面的器件安全工作區域,且能從載流子濃度、電流密度、電勢、電場等綜合電參數分布方面系統研究單粒子燒毀機理,從而便捷地開展單粒子效應防護設計及驗證。

自2000 年以來,國內外基于重離子試驗和仿真手段開展了SiC 基MOSFET 器件單粒子效應的研究,建立了器件SEB 的試驗方法與仿真模型,并于近十年根據試驗結果和半導體工藝器件仿真(TCAD)測試了其安全工作電壓以及SEB 截面,初步揭示了SiC MOSFET 的SEB 規律。但是在器件SEB 機理解釋方面缺少對器件內部電參數微觀變化的分析,不利于揭示器件SEB 的損傷物理機制。

本文基于有利于揭示器件內部電參數微觀變化的TCAD 平臺,開展SiC MOSFET 器件單粒子燒毀仿真分析,研究器件內部SEB 的敏感區域、安全電壓范圍及器件發生SEB 時電參數的分布,基于模擬仿真結果進一步研究器件SEB 的防護方法。

1 器件模型構建及仿真參數設置

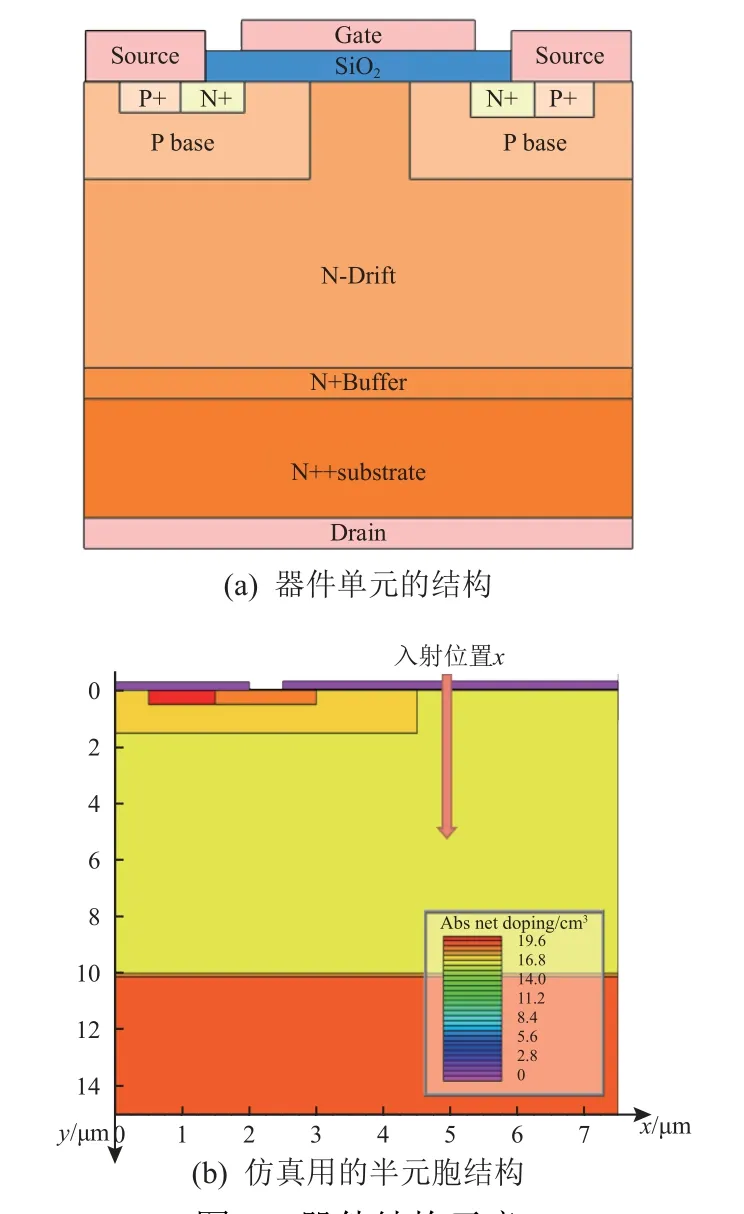

參考國內某廠商典型的1200 V SiC MOSFET建立器件的工藝結構模型,其中:功率器件工藝結構為垂直結構,其柵極和源極位于器件的頂部,而其漏極位于器件的底部,如圖1(a)所示;電學仿真時所使用的半元胞結構的橫向寬度為7.5 μm,縱向高度為15 μm,柵氧化層的厚度為0.06 μm,在襯底與漂移區之間有一個緩沖層,厚度為0.1 μm,其余各區域的尺寸及摻雜濃度范圍等信息如圖1(b)所示。

圖1 器件結構示意Fig. 1 Schematic diagram of the device structure

本文仿真所選用的物理模型有SRH 復合模型、Auger 復合模型、CVT 集成模型、Fermi-Dirac 載流子統計模型、BGN 模型和碰撞離化模型。

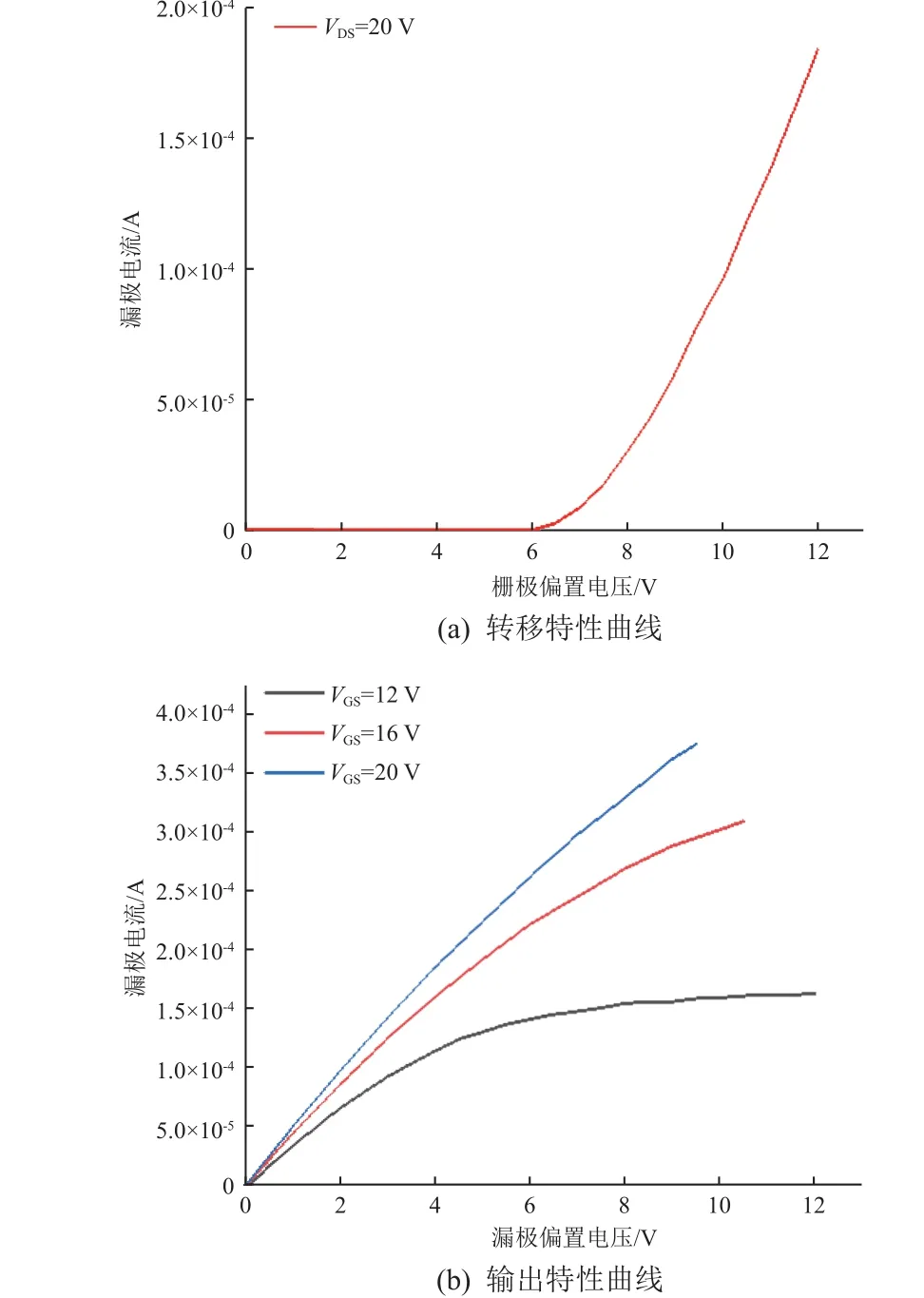

根據上述典型物理方程和器件電學模型,對器件進行電學特性仿真,得到漏極偏置電壓=20 V時的轉移特性曲線(見圖2(a))和柵極偏置電壓分別為12 V、16 V 和20 V 時的輸出特性曲線(見圖2(b)),其中閾值電壓約為6 V。

圖2 器件電學仿真特性Fig. 2 Electrical characteristics obtained by TCAD simulation of the device

在單粒子燒毀仿真中,入射粒子為垂直入射,入射位置為圖1(b)橫坐標。入射粒子和產生電荷脈沖基本參數的選取參考SiC MOSFET 典型數值,具體為:粒子入射產生的電荷徑跡半徑為0.05 μm,入射深度為15 μm;LET 值75 MeV·cm/mg;電荷生成脈沖的峰值時刻為4 ps;電荷生成的脈沖寬度為4 ps。這些參數是依據SiC 器件中常用數值設置的初始值,后續可根據單粒子試驗結果進行驗證和優化。

2 器件單粒子燒毀仿真結果與分析

2.1 閾值電壓及敏感區域分析

器件SEB 的漏極電流隨時間變化的仿真結果如圖3 所示,此圖對應的仿真器件結構中柵極偏置電壓=0 V(器件處于截止態)、漏極偏置電壓分別為490 V、500 V 和550 V,以及入射位置=5 μm、入射粒子LET=75 MeV·cm/mg 的條件下。粒子入射后,在一定的漏極電壓下,若漏極電流能夠恢復至粒子入射之前的水平,則意味著器件未發生SEB;若漏極電流增大并維持在一個較高數值,則意味著發生SEB 失效。從圖3 可以看出:當漏極電壓為490 V 時,漏極電流最終降到0;當漏極電壓為500 V 時,電流值最終保持在一常數值,表明器件發生了SEB;隨著漏極電壓的增大,漏極電流的最終數值也在增大。因此該器件發生SEB的閾值電壓約為500 V。

圖3 器件發生SEB 前后漏極電流隨時間的變化Fig. 3 The drain current in the device before and after SEB

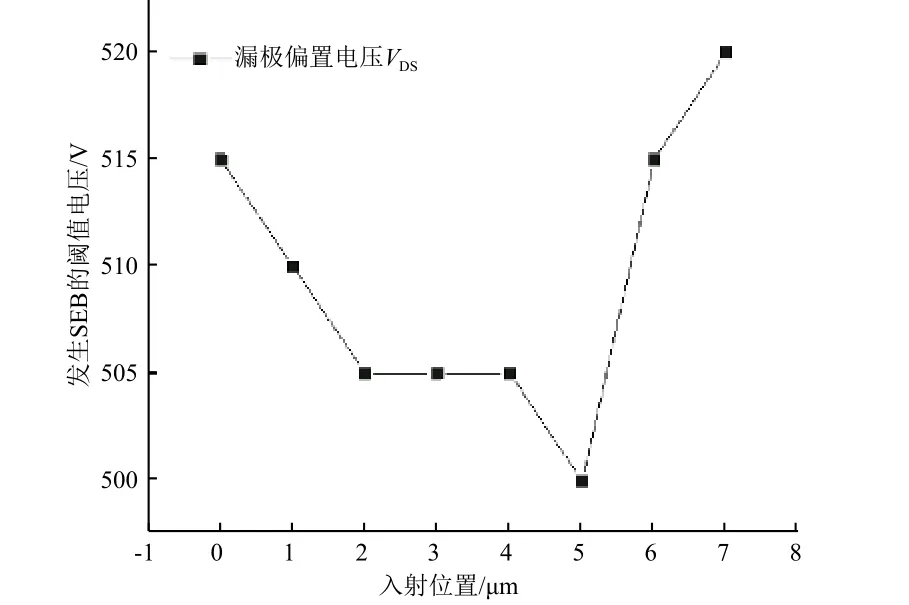

為了進一步研究器件發生SEB 的敏感位置,在=0 V(器件處于截止態)、入射粒子LET=75 MeV·cm/mg 的條件下,對不同入射位置下器件的燒毀特性進行了仿真,結果如圖4 所示。

圖4 不同入射位置的SEB 閾值電壓Fig. 4 SEB threshold voltage in different incident positions

可以看出,器件內部SEB 的敏感性不一樣,并且當入射位置=5 μm 時,器件發生SEB 的閾值電壓最低,說明在該位置(Pbase 基區附近),器件更容易發生SEB。這是因為當粒子入射器件后產生的空穴會向源極漂移,使得Pbase 基區的電壓增加,距離Pbase 基區越遠,產生的空穴漂移到源極就要經過更遠的距離,相比其他入射位置會產生更大的壓降,使得寄生雙極結型晶體管(BJT)更加容易導通;另一方面,當粒子入射器件后,如果入射徑跡靠近器件內部寄生BJT 所在的位置,則會使粒子入射所產生的空穴在外部電場的作用下更快地向源極漂移,由空穴的漂移運動所產生的瞬態電流會在Pbase 基區產生更大的壓降,也會使得寄生BJT 更加容易導通。

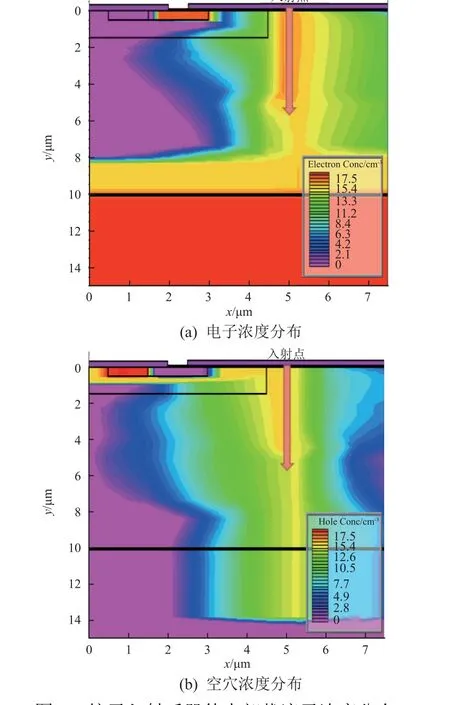

2.2 器件單粒子燒毀特性及機理分析

在器件單粒子燒毀敏感性研究的基礎上,進一步研究了器件單粒子燒毀的機理。圖5 所示為粒子入射后器件內部電子濃度分布和空穴濃度分布。經分析:當器件處于關閉態時(=0 V),高能帶電粒子入射器件后,會在粒子入射徑跡上沉積能量,從而產生電子-空穴對;當漏極加正向偏置電壓后,器件內部產生的電場方向由漏極指向源極,電離產生的載流子在電場作用下發生漂移運動,產生瞬態脈沖電流;電子沿著電場相反方向向漏極漂移,因此電子在襯底和緩沖層附近有較高的濃度(圖5(a));空穴沿著電場方向穿過Pbase 基區向源極和P+源區漂移,因此空穴在源極和P+源區附近有較高的濃度(圖5(b))。

圖5 粒子入射后器件內部載流子濃度分布Fig. 5 Distributions of carrier concentration inside the device after incidence of particles

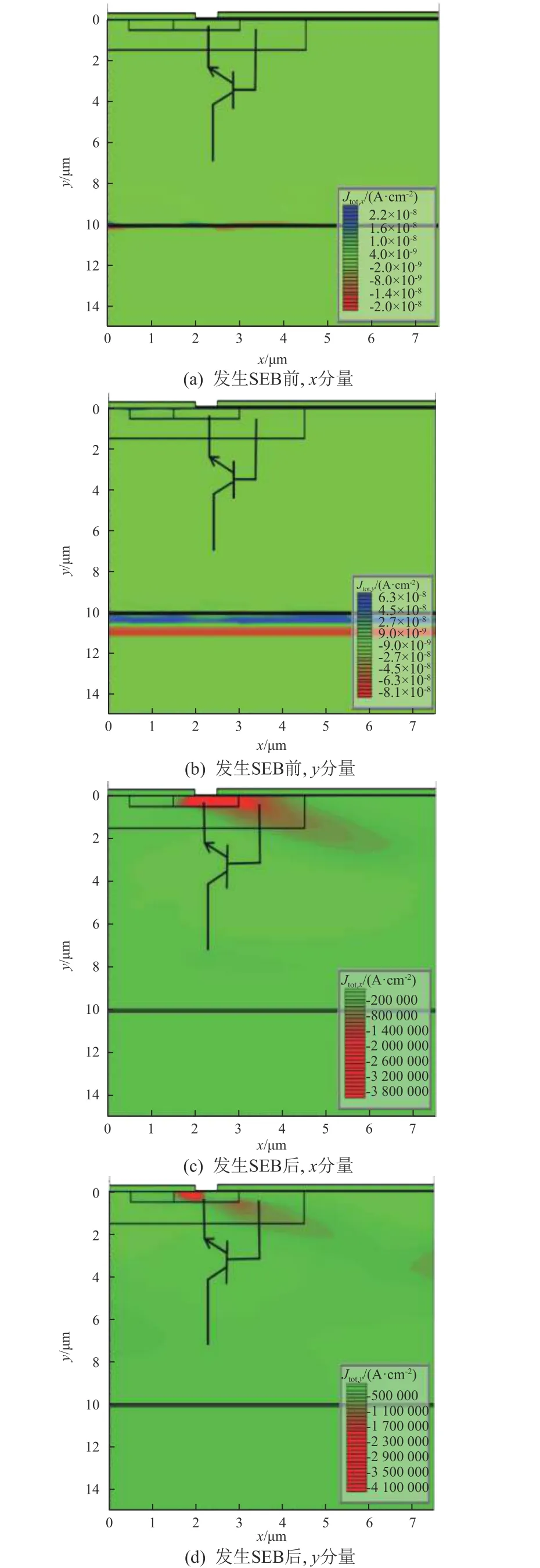

分析在=0 V(器件處于截止態)、=500 V條件下器件發生SEB 前后的電流變化特性,結果如圖6 所示。

圖6 器件發生SEB 前后的電流密度分布(VDS=500 V)Fig. 6 Distributions of current density in the device before and after SEB (VDS=500 V)

SiC MOSFET 器件結構中本身就存在一個寄生BJT,器件的N+源區、Pbase 基區和N-漂移區分別對應寄生BJT 的發射極、基極和集電極。在器件正常工作時N+源區和Pbase 基區是短接的,所以寄生BJT 處于關閉狀態,襯底緩沖層附近會有10A/cm數量級的漏電流,電流密度、分量分別如圖6(a)和圖6(b)所示。當器件關斷且漏極電壓較高時,如果有高能帶電粒子入射器件,由于寄生BJT 的放大效應,產生的正反饋作用使寄生BJT的發射極(N+源區)電流密度倍增,達到10A/cm數量級,電流密度、分量分別如圖6(c)和圖6(d)所示,導致漏極電流急劇增大,直至燒毀器件。

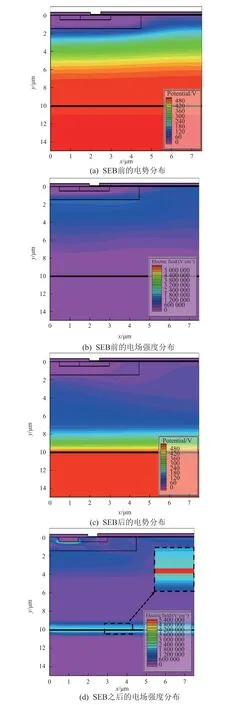

分析了器件截止狀態下(=0 V)發生SEB 過程中的內部電勢和電場強度的變化特性,結果如圖7 所示。在=500 V 時,縱向電勢是緩變分布的(圖7(a)),寄生BJT 集電極的空間電荷區邊界在Pbase 基區處,可以看出電場強度分布集中在此區域附近(圖7(b))。當高能粒子入射器件之后,器件內部沿粒子徑跡產生大量的電子-空穴對,在這些載流子的漂移電流的作用下器件縱向的電勢不再是緩變分布,而是在N+緩沖層和N-漂移區界面處發生了突變(圖7(c))。這一突變是由于N-漂移區淺摻雜,寄生BJT 集電極的空間電荷區邊界會擴展到N+緩沖層的邊緣,因而在N+緩沖層的邊緣處形成了一個很大的電場,所以這個界面處的電場強度極高;隨著寄生BJT 雙極放大作用與緩沖層電場強度增大形成的正反饋使電流加大,這一界面處的電場強度也隨之上升(圖7(d)),最終發生了雪崩倍增效應,導致器件燒毀。從圖7(d)可以看出,在N+緩沖層附近電場強度較大,約為5.4 MV/cm,在P+源區/Pbase 基區的電場強度也很大,約為4.2 MV/cm,這是由于當漏極加較高的偏置電壓(=500 V)時,在粒子入射后,空穴沿著電場方向穿過Pbase 基區快速向源極和P+源區漂移,使得P+源區/Pbase 基區附近載流子遷移率較大,所以此處的電場強度也很高。上述兩個位置的電場強度均超過了SiC 材料的擊穿場強(3 MV/cm),因此這兩個區域也就是發生SEB 的敏感區域,其中N+緩沖層具有最高的場強,是決定器件SEB 敏感性的關鍵區域。

圖7 器件發生SEB 前后的電勢電場分布圖(VDS=500 V)Fig. 7 The electric potential and electric field distribution in the device before and after SEB (VDS=500 V)

3 器件防護設計分析

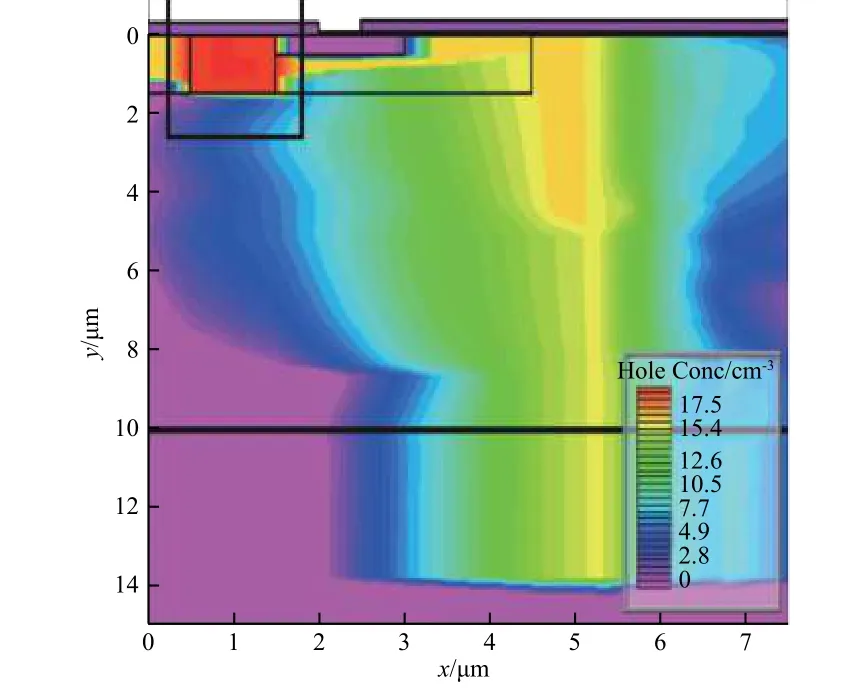

通過2.2 節器件中SEB 的機理分析,為提高器件發生SEB 的閾值電壓,借鑒Si 基器件中的防護設計方法,本文提出一種防護設計思路:將P+源區向下延伸至Pbase 基區。對此防護結構的器件進行了SEB 的仿真分析,結果如圖8 所示。

圖8 P+源區擴展后,空穴濃度的分布特性Fig. 8 Distributions of hole concentration when the P+ source region is extended

由圖8 可見,將P+源區向Pbase 基區延伸后,帶電粒子入射后產生的空穴可以快速從P+源區漂移到源極,空穴在P+源區附近有較高濃度分布。因此這一結構可以有效減少空穴向寄生BJT 敏感區域漂移的數目。由于當重摻雜的P+源區向下延伸到Pbase 基區時降低了寄生BJT 基區的電阻,使瞬態電流通過寄生BJT 基區時在Pbase 基區產生的壓降變小,所以抑制了寄生BJT 的導通。在=0 V(器件處于截止態)、入射粒子LET 值為75 MeV·cm/mg的條件下,對加入防護設計后的結構進行了仿真,結果如圖9 所示。

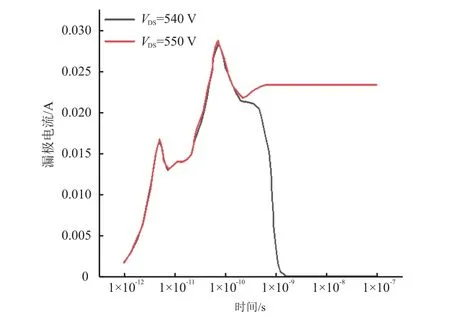

圖9 P+源區擴展后,器件發生SEB 前后的漏極電流隨時間變化Fig. 9 The variation of the drain current against time before and after SEB when the P+ source region is extended

由圖9 可見,器件的漏極電壓在540 V 時未發生SEB,在550 V 時才發生SEB,而防護設計前的器件在=500 V 時就發生了SEB。由此可見,經過這樣的防護設計后,SEB 的閾值電壓提高了近50 V。對這種防護設計后的結構進行了電學特性仿真,發現其轉移特性和輸出特性均保持不變,表明防護設計前后的電學特性是一致的,且可以通過提高離子注入能量實現P+源區擴展,具備器件工藝設計可行性。

4 結束語

本文利用TCAD 對SiC MOSFET 器件進行了單粒子燒毀仿真分析,發現粒子入射最敏感位置時器件發生SEB 的閾值電壓在500 V,與文獻報道的SEB 閾值電壓典型試驗值400~600 V 相符合,表明本文的仿真模型具有較高的精度。同時,仿真獲得了器件的電子-空穴濃度分布、電流密度分布、電勢及電場分布特性,模擬結果表明器件發生SEB 的原因是寄生晶體管的正反饋作用導致緩沖層和基區的電場強度(5.4 MV/cm 和4.2 MV/cm)超過SiC 材料擊穿場強(3 MV/cm)。此外,模擬發現將P+源區的深度向下延伸至Pbase 基區底部時,器件發生SEB 的閾值電壓從500 V 提高到近550 V。后續將從工藝試驗層面對此防護設計進行驗證。