基于電壓閾值憶阻器SPICE模型的加法器電路設計

黃麗蓮,朱耿雷,項建弘,張春杰,李文亞

(哈爾濱工程大學信息與通信工程學院,哈爾濱 150001)

0 引言

憶阻器被認為是打破集成電路限制的潛在器件之一[1],而憶阻器的生產成本很高,目前尚未商用,實驗室制備更是難上加難,所以設計SPICE 憶阻器模型以供實驗室實驗研究顯得尤為重要。加法器是組成計算機的基本元件[2],基于憶阻器的加法器的設計具有實際的應用意義。1971 年,Chua[3]根據電路對稱理論預測并證明了憶阻器的存在。2008 年,HP 實驗室設計了一種由Pt/Ti/TiO2/Pt 組成的憶阻器物理模型并制備出了第1 種物理憶阻器器件[4]。憶阻器可應用于邏輯電路[5-7]、存儲器[8]、神經網絡[9-10]、混沌電路[11-12]等多個領域。現有的SPICE 憶阻器模型中往往只能匹配一種物理憶阻器器件,而且數學模型較復雜[13]。設計一個簡單通用的SPICE 憶阻器模型對憶阻器基礎實驗和憶阻邏輯電路實驗研究具有重大意義。

本文首先設計了一種參數可調且能夠匹配兩種憶阻器物理器件的憶阻器SPICE 模型,并對此憶阻器模型進行實驗驗證與比較討論,同時給出了SPICE 等效模型與SPICE代碼,方便在后續的實驗中使用。然后介紹了基于電壓閾值憶阻器SPICE 模型的多功能憶阻邏輯模塊和MRL(憶阻器比例邏輯門)并將其應用在加法器中,設計了一種基于電壓閾值憶阻器SPICE模型的加法器電路設計方法。最后對此加法器進行實驗驗證與性能分析。

1 電壓閾值憶阻器SPICE模型設計

1.1 數學模型

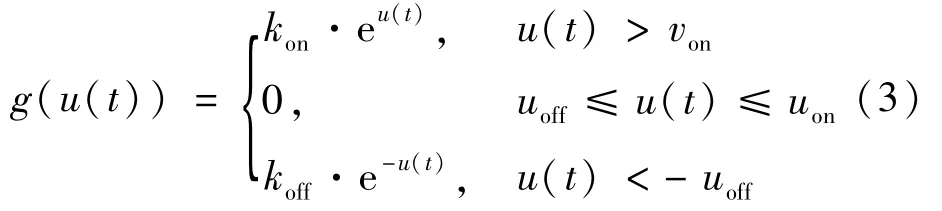

本文設計模型的I-U關系由下式決定,狀態變量x表示歸一化的導電區寬帶,其范圍為[0,1],即

式中:ΔR=Roff-Ron,Roff和Ron分別是憶阻器的最大和最小憶阻值,對應的狀態變量分別為x=0,x=1。

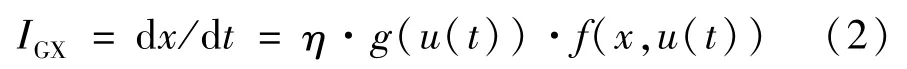

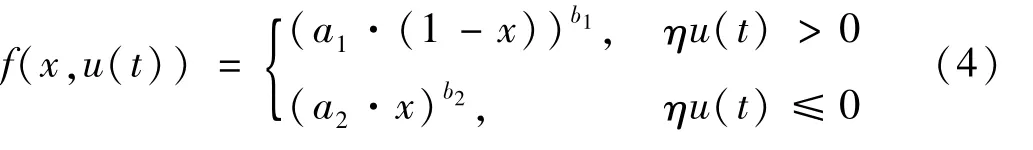

狀態變量x的導數可以表示為兩個獨立函數的乘積,即

式中,η用來確定狀態變量運動的方向。為了實現電壓閾值行為,給出方程:

式中:uon和uoff分別表示憶阻器的正負閾值電壓;kon、koff分別是對應的線性可調參數。考慮到實際的憶阻器器件存在不同的正負閾值以及不同的遷移速率,因此引入兩種不同的閾值與線性參數。從式(3)可以看出,只有當輸入電壓滿足閾值條件時,憶阻器的狀態才會發生改變,即可描述為帶有可編程電壓閾值的憶阻器。

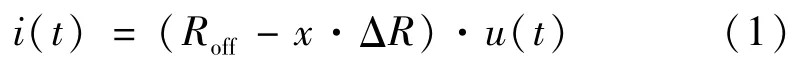

為了描述憶阻器的非線性漂移行為,設計了一個漂移速度自適應方程

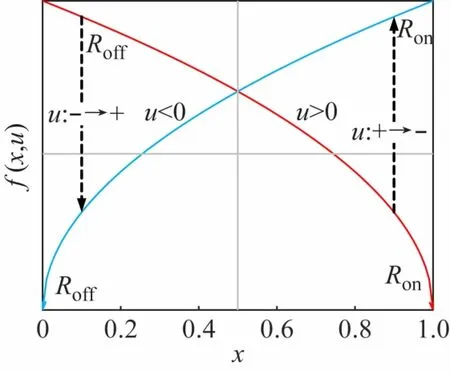

式中:a1,a2,b1,b2為可調參數,根據現有的憶阻器表征數據,狀態變量在兩個方向上的運動速率是不同的,因此引入η來定義狀態變量運動的方向,這里η =1。假設a1=a2=a,b1=b2=b,那么f(x,u(t))的基本示意圖如圖1 所示。圖中兩組漂移速度曲線分別用來描述Ron→Roff和Roff→Ron的變化過程,它們的函數取值范圍均為ab~0。此外,通過調整參數得到不同的參數組合(a,b),可以得到不同的非線性漂移速度曲線。

圖1 漂移速率f(x,u(t))的控制原理圖

參數a和b對漂移速度曲線的調控起到了不同的作用。其中參數a是線性參數,可以對曲線進行向上或向下尺度縮放,進行小范圍的校正;參數b是指數型參數,可以通過調整取值大小來決定曲線的形狀。

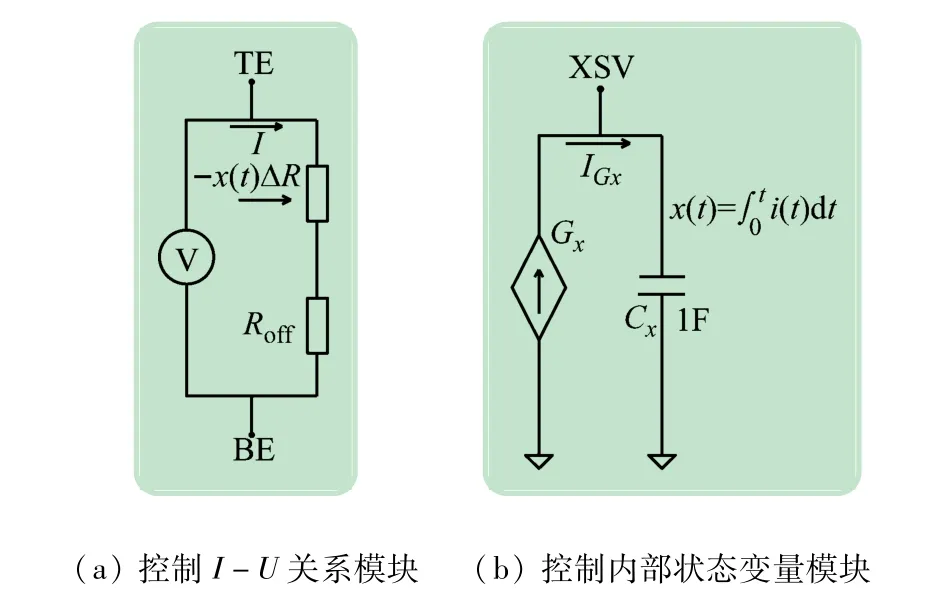

1.2 SPICE等效模型及SPICE代碼

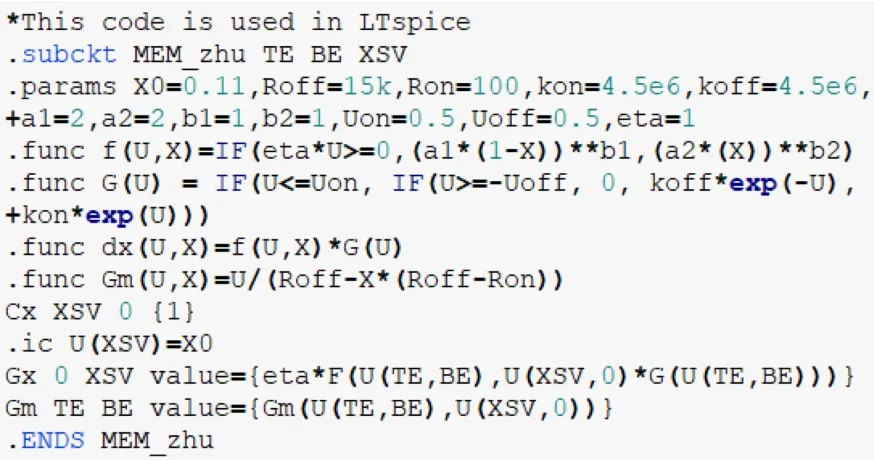

上述數學模型對應的SPICE 等效模型如圖2 所示。其中圖2(a)描述了器件的I-U關系;圖2(b)用于計算器件的狀態變量的值。圖3 給出了LTspice 中使用本文設計的SPICE 憶阻模型進行仿真實驗的代碼。

圖2 SPICE等效電路模型

圖3 LTspice中使用的代碼

1.3 實驗分析與驗證

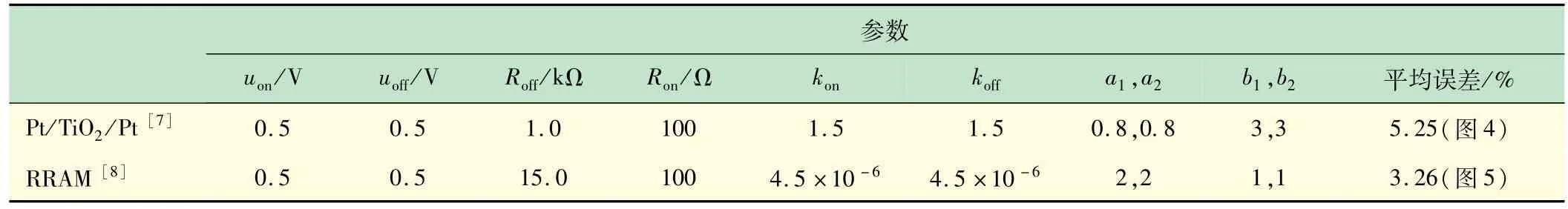

憶阻器建模是為了描述物理憶阻器設備與擬合匹配多種物理憶阻器件,因此實驗驗證與分析是檢驗一個電壓閾值憶阻器模型的關鍵步驟。本節給出了通過調整模型參數擬合匹配不同的物理憶阻器件I-U行為的仿真結果,相應的擬合參數如表1 所示。

表1 憶阻器實驗擬合參數設置

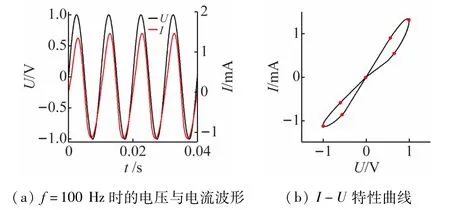

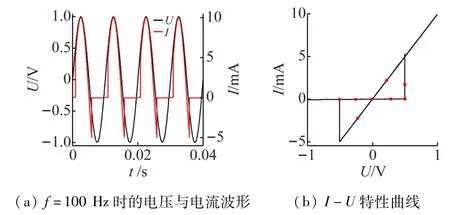

基于TiO2[2]和RRAM[14]的憶阻器器件數據,對實驗結果進行分析。I-U特性曲線中的輸入是連續變化的曲線,同時測試不同電壓下的電流值得到對應的I-U特性曲線。第1組憶阻數據擬合實驗結果如圖4所示,圖4(b)中的紅點為目標數據點。輸入是正弦電壓,得到對應的I-U特性曲線,與TiO2的憶阻器器件數據相比平均誤差為3.58%。從圖4 中可以看出,本文設計模型可以模擬HP憶阻器模型的I-U行為,并且平均誤差率較低。圖5 為對阻變存儲器(Resistance Random Access Memory,RRAM)的數據擬合實驗結果,圖5(b)中的紅點為目標數據點。輸入為正弦電壓,實驗結果以3.26%的平均誤差再現了RRAM的I-U曲線特性,并體現出了RRAM 的開關特效。本文設計的電壓閾值憶阻器模型不僅能夠匹配兩種物理憶阻器設備,還能應用在邏輯電路中。

圖4 輸入電壓為sin 2πft時擬合TiO2 憶阻器數據的實驗結果

圖5 輸入電壓為sin 2πft時擬合RRAM憶阻器數據的實驗結果

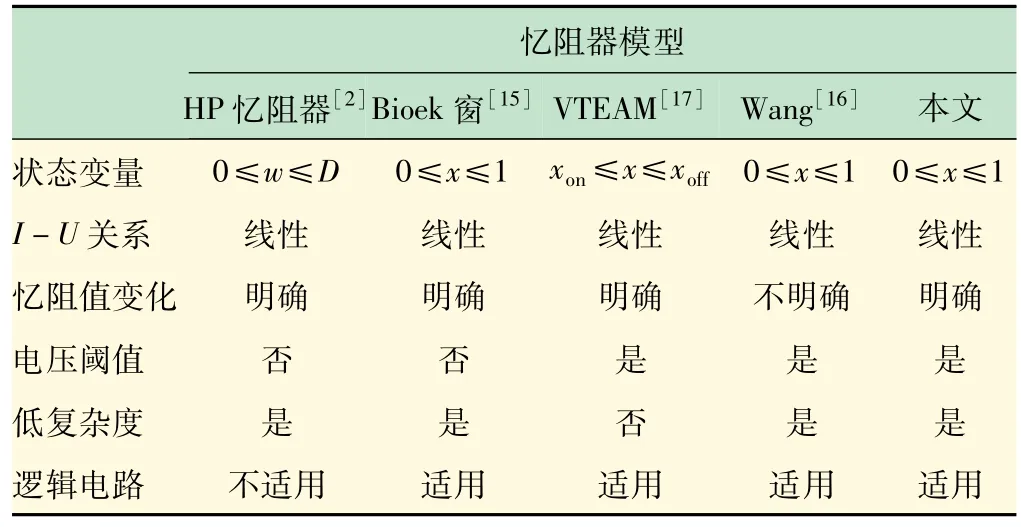

1.4 比較討論

將本文設計的憶阻器模型與現有的部分憶阻器模型進行比較,結果如表2 所示。由表2 分析可知,本文設計的電壓閾值憶阻器模型具有電壓閾值特性和明確的I-U關系,可應用于邏輯電路與神經網絡突觸實驗。復雜度較低容易理解,有助于對憶阻器的理解與研究。總體來說是一個功能完整的憶阻器。

表2 本文設計的模型與現有部分憶阻模型的比較

2 電壓閾值電憶阻器的加法器電路設計

2.1 基本原理

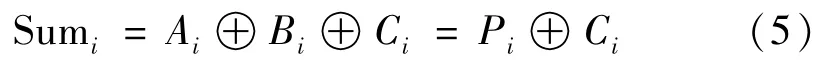

Kowsalya等[17]設計了一種低功率的并行前綴加法器,該技術提高了二進制加法器的運算速度,降低了功率和晶體管的數量。在兩個操作模塊的每一個點位i上,兩個輸入信號Ai和Bi被加在相應的進位信號上產生和輸出Sumi:

進位產生函數和進位傳播函數表達式:

加法器模塊進位信號的計算方法:

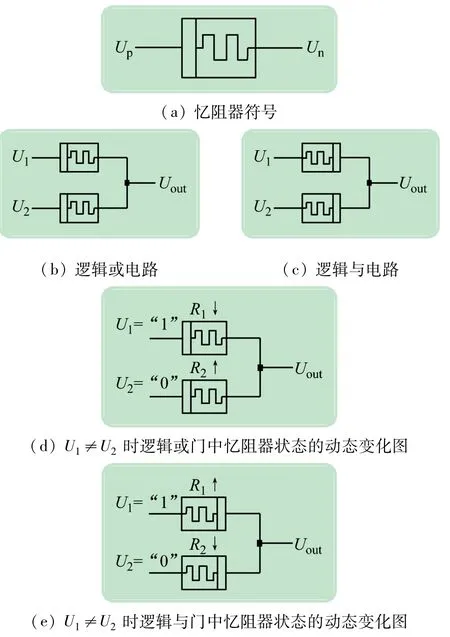

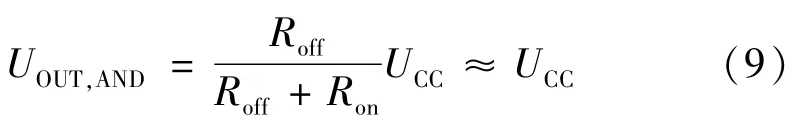

Kvatinsky等[18]設計的MRL邏輯門能夠形成完備的布爾邏輯族,在LTspice 平臺中搭建的MRL 邏輯門如圖6 所示。圖中:憶阻器符號中Up和Un分別代表正負端口;U1和U2為輸入;UCC代表邏輯“1”;GND代表邏輯“0”。“或”和“與”邏輯門對相同的輸入做出類似的反應(2 個輸入都是邏輯“1”或邏輯“0”)。在邏輯與門中,負極連接VCC,電流從正極流出,憶阻器狀態的動態變化如圖6(d)所示。假設Roff≥Ron,則邏輯與門的輸出由下式分壓決定:

在邏輯或門中,正極連接UCC,電流從正極流入,憶阻器狀態的動態變化如圖6(e)所示。同樣,邏輯或門的輸出也由分壓決定,

圖6 憶阻器符號及MRL 門原理圖

構建MRL邏輯門的關鍵是憶阻器具有閾值特性與憶阻值的開關特性,前文設計的電壓閾值憶阻器模型具備這些特性可用于構建MRL邏輯門。

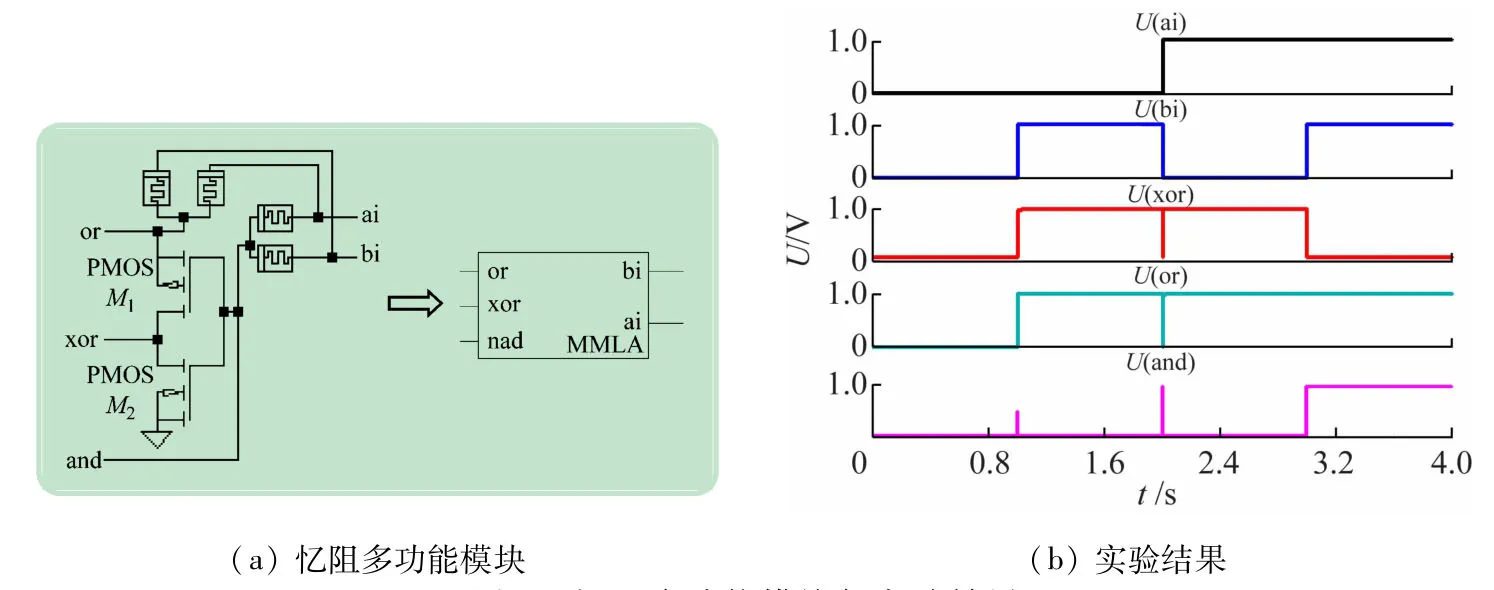

Yang[19]設計了一種高性能憶阻憶阻多功能邏輯模塊(MMLA)。該模塊可以在一個周期內實現與、或、異或的邏輯功能。利用電壓閾值憶阻器SPICE 模型在LTspice平臺中構建多功能邏輯模塊,如圖7 所示,其中圖7(b)為實驗結果。

圖7 憶阻多功能模塊與實驗結果

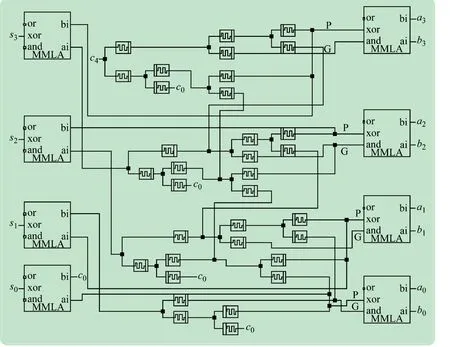

2.2 基于電壓閾值SPICE憶阻器模型的4 bits 加法器電路

根據并行前綴加法器算法,在LTspice 平臺利用上述構建的MRL邏輯門和多功能邏輯模塊多功能邏輯模塊搭建了一個4 bits加法器如圖8 所示。多功能邏輯模塊可以在單個時鐘周期內產生Gi和Pi信號,進而少延遲時間,提高邏輯運算效率。

圖8 基于電壓閾值SPICE憶阻器模型的4 bits加法器電路圖

3 實驗驗證與性能分析

3.1 實驗驗證

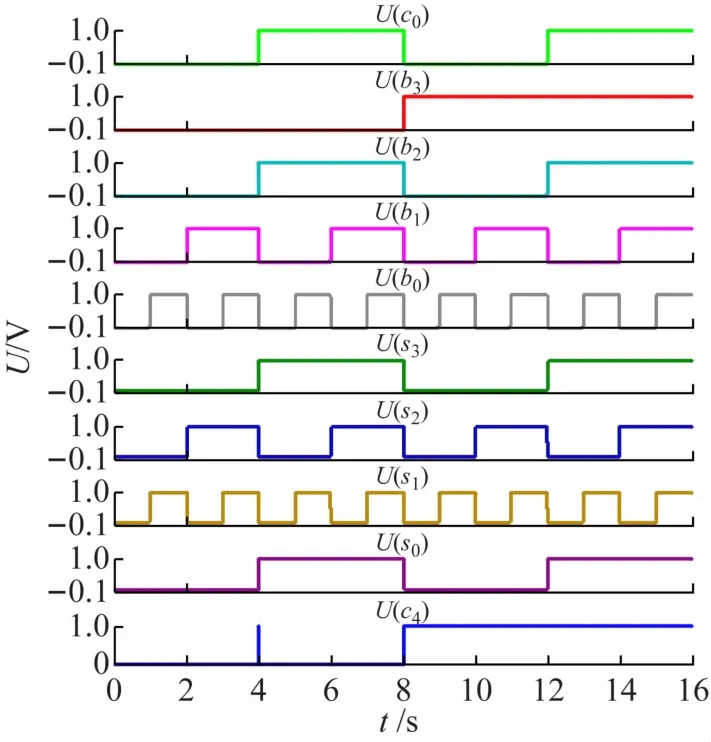

在LTspice平臺上對基于憶阻器的加法器進行實驗驗證,電路中的參數設為表1 中擬合RRAM采用的參數。實驗結果如圖9 所示,其中c0是最低位的進位;c4是輸出的最高位的進位;U(s0,s1,s2,s3)是輸出的電壓波形。為了簡化仿真過程,將b3~b0和a3~a0設置為相同的電壓波形。仿真結果表明,該并行前綴加法器的進位輸出與和輸出的波形均與預期一致。

圖9 基于電壓閾值SPICE憶阻器模型的4 bits加法器電路實驗結果

3.2 性能分析

基于IMPLY(實質蘊含邏輯)的邏輯電路[7]以憶阻值作為狀態變量來表示輸入和輸出,其中高憶阻值和低憶阻值分別表示狀態“0”和“1”,操作的最終結果被存儲在憶阻器中,該電路需要一個額外的讀寫電路和初始化電路,以確保邏輯操作的正確性。額外的初始化和讀寫電路通常由憶阻器和CMOS等電路元件組成,這將使得邏輯電路占用更大的芯片面積并且消耗更多的功率。

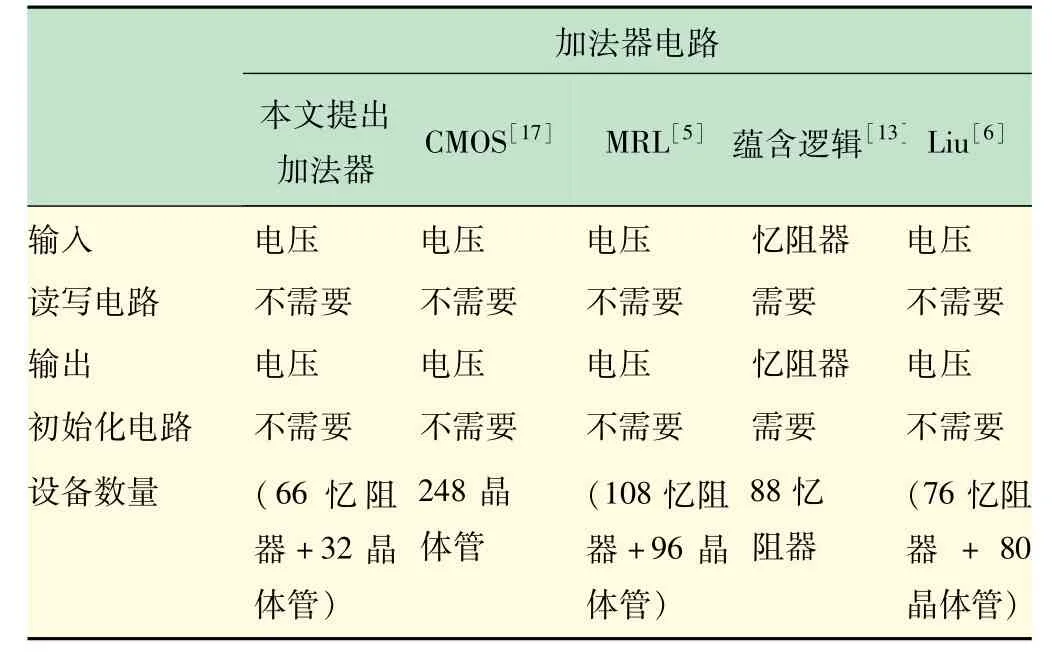

本文設計的加法器電路以電壓電平作為邏輯變量,它與傳統CMOS技術兼容,不需要額外的讀寫初始化電路。此外,采用了憶阻多功能邏輯模塊,大大減少了使用的器件數量,提高了器件的利用率,簡化了電路設計的復雜性,降低了電路的功耗。設計的電壓加法器電路與幾種加法器電路的對比如表3 所示。

表3 本文設計的加法器與其他方法構成加法器電路的比較

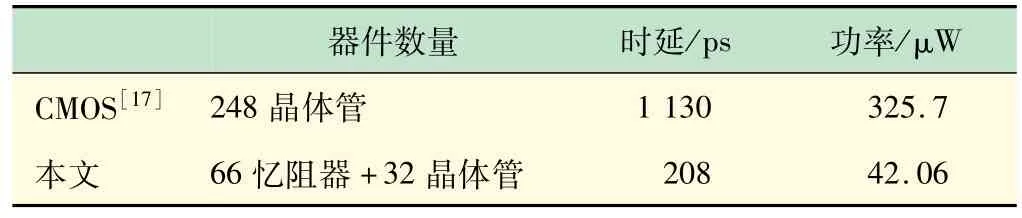

本文設計的加法器與傳統CMOS加法器性能的對較如表4 所示。表中功率指的是靜態和動態功率的平均值(μW)。從表4 可以看出,本文設計的加法器在功耗和延遲性能方面都優于傳統CMOS工藝,功耗降低了87.1%。

表4 本文設計的加法器電路與傳統CMOS加法器性能比較

4 結語

設計了一種電壓的閾值憶阻器SPICE 模型并應用在邏輯電路中,該憶阻器模型功能完整,能夠運用在神經網絡與存儲器中。介紹了MRL 邏輯門和多功能邏輯模塊,然后設計一種基于電壓閾值憶阻器模型的加法器,并對其進行實驗驗證與性能分析。實驗結果與性能分析表明,設計的電壓加法器電路能夠實現正確的邏輯功能,且較傳統的基于CMOS 的加法器能夠減少87.1%的功率。