基于FPGA 的數據輸出顯示電路設計

廖超平

(廣西機電職業技術學院,廣西 南寧 530007)

在非常多的數字系統的設計中存在數據輸出顯示模塊,數據輸出顯示模塊首先要將用二進制(BIT)碼表示的計算結果轉換成用戶習慣使用的十進制(BCD)碼,然后轉換成整數部分第一位不為零的數字前的零不顯示的大家習慣的輸出形式,在通過顯示器(通常是LCD 顯示器)顯示出來。在基于FPGA 設計數字系統時數據輸出顯示電路模塊是經常使用的。基于FPGA 設計數字系統時數據輸出顯示電路在各種智能儀表、電子秤和數控機床等數字系統的設計中廣泛使用。

1 數據輸出顯示電路設計方法原理分析

1.1 二進制-BCD 轉換

數字系統使用的數據通常是二進制碼,在輸出前要轉為BCD 碼。二進制-BCD 轉換電路利用加3 或0再移位方法進行,詳細原理請參考文獻[1]。

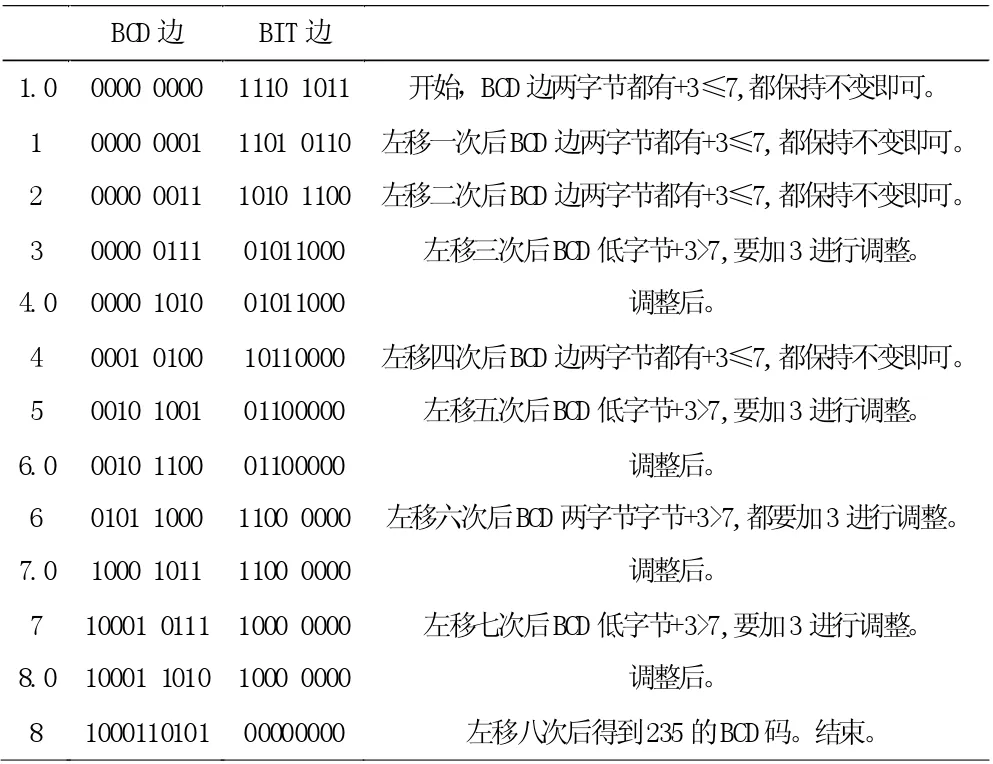

下面舉例說明。假如有一個八位二進制數1110 1011(十進制數235),要把它轉成十進制數的BCD 碼[2]:

在上面處理過程中,每次移位前,先判斷BCD 邊的每個字節特點,若是(0,0,0,0)-(0,1,0,0)這幾個值時,即+3≤7,向左邊移動一位后,沒有對高一位的進位,而且本位最大也符合十進制的表達形式,故這字節加0,即保持不變即可。

如這個BCD 邊字節是(0,1,0,1)-(1,0,0,1)這幾個值時,即+3>7,向左邊移動一位后,最少也存在對高一位的進位,進位是逢十進一,所以要進行修正。修正的方法就是加3 后再移位。

上面分加3 或0 移位兩種情況,原因是為了保證下一次移位后,符合十進制數進位和十進制數的表達形式,即每位十進制數碼應該只能是:0-9 這十個數碼。

BCD 邊 BIT 邊1.0 0000 0000 1110 1011 開始,BCD 邊兩字節都有+3≤7,都保持不變即可。1 0000 0001 1101 0110 左移一次后BCD 邊兩字節都有+3≤7,都保持不變即可。2 0000 0011 1010 1100 左移二次后BCD 邊兩字節都有+3≤7,都保持不變即可。3 0000 0111 01011000 左移三次后BCD 低字節+3>7,要加3 進行調整。4.0 0000 1010 01011000 調整后。4 0001 0100 10110000 左移四次后BCD 邊兩字節都有+3≤7,都保持不變即可。5 0010 1001 01100000 左移五次后BCD 低字節+3>7,要加3 進行調整。6.0 0010 1100 01100000 調整后。6 0101 1000 1100 0000 左移六次后BCD 兩字節字節+3>7,都要加3 進行調整。7.0 1000 1011 1100 0000 調整后。7 10001 0111 1000 0000 左移七次后BCD 低字節+3>7,要加3 進行調整。8.0 10001 1010 1000 0000 調整后。8 1000110101 00000000 左移八次后得到235 的BCD碼。結束。

1.2 數據的譯碼

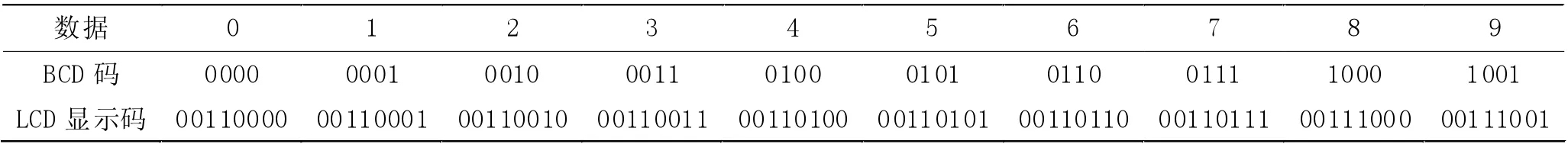

數字和字母要用LCD 顯示器顯示出來,要譯碼成LCD 顯示器顯示的數據格式,數字0-9 的1602LCD數據譯碼表如下:

所以,要輸出的數字要先轉換為BCD 碼,再在其前面加上"0011"。如D0 (7 downto 0)<= "0011" &DIN(3 downto 0)。

對于字母則要詳細查找1602LCD 數據譯碼表,這里省略。

數據 0 1 2 3 4 5 6 7 8 9 BCD 碼 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 LCD 顯示碼 00110000 00110001 00110010 00110011 00110100 00110101 00110110 00110111 00111000 00111001

1.3 LCD 控制電路設計方法原理

要用LCD 顯示的數據主要有數字和字母;有一經顯示就不變的靜態顯示,有需要不斷刷新的動態顯示。另外,LCD 控制電路通常有兩種設計方法,一是狀態機方法,二是計數器方法。

綜合考慮以上LCD 顯示的數據的特點,我們采用對有可能顯示數字和字母的LCD 顯示范圍采用重復掃描的方式顯示數據,對不變的靜態顯示采用每次刷新都重復顯示同樣的數據,而變化的動態顯示則每次刷新時及時更新顯示數據。對于掃描的控制,這里采用計數器方法,因此方法具有直觀、容易遷移到別的設計的特點。

LCD 控制過程分為初始化階段和循環掃描兩行輸出階段。

(1)1602LCD 的一般初始化過程

啟動電源

等待30mS;

寫指令3CH(不檢測忙信號);

以后每次寫指令、讀/寫數據操作均需要檢測忙信號或有足夠延時;

寫指令3CH:顯示模式設置;

寫指令01H:顯示清屏;

寫指令06H:顯示光標移動設置;

寫指令0CH:顯示開及光標設置。

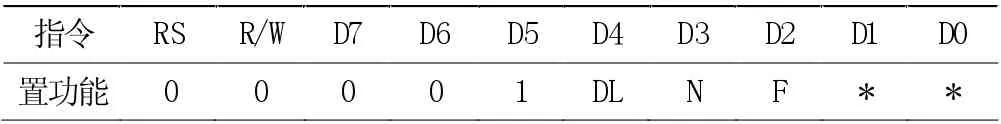

1602LCD 的一般初始化過程用到的指令如下:

顯示模式設置:

指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0置功能 0 0 0 0 1 DL N F * *

DL:1-8 位數據接口、0-4 位數據接口;N:1-2 行顯示、0-1 行顯示;

F:1-5X10 字 體、0-5X7 字 體。當 數 據 位 為00111100 [0x3C]時,設置8 位數據接口,16×2 顯示,5×10 點陣。

清顯示:數據位為00000001 [0x01]

指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0清顯示 0 0 0 0 0 0 0 0 0 1光標和顯示模式設置:指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0置輸入模式 0 0 0 0 0 0 0 1 I/D S I/D:光標移動方向,1-右移,0-左移;S:屏幕上所有文字是否左移或者右移。1-有效,0-無效。當數據位為00000110 [0x06]時,光標右移,整屏顯示不移動。顯示開關及光標設置:指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0顯示開/關控制 0 0 0 0 0 0 1 D C B D:顯示(1 有效);C:光標顯示(1 有效),B:光標閃爍(1 有效)。當數據位為00001100 [0x0C]時,開顯示和光標不顯示,光標不閃爍。(2)循環掃描兩行輸出階段兩行循環掃描中則有三種情況:一是空白,此時輸出空白符,指令如下。指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0寫數據 1 0 0 0 1 0 0 0 0 0二是不變字符,此時直接輸出所要求的字符如“i”。指令如下。指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0寫數據 1 0 0 1 1 0 1 0 0 1三是輸出變化的數字,例如輸出頻率的各位數字。這時輸出由一個總線信號(例如D0(7 downto 0))賦予。指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0寫數據 1 0 D0(7 downto 0)

2 數據輸出顯示電路原理框圖

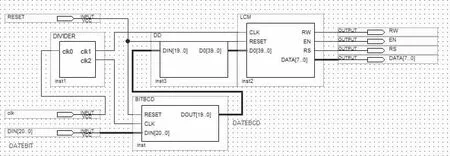

原理框圖,見圖1。

圖1 原理框圖

基于FPGA 設計數字系統時數據輸出顯示電路主要包括三部分:首先是二進制-BCD 轉換電路模塊(BITBCD),此模塊實現將用二進制(BIT)碼表示的計算結果轉換成十進制(BCD)碼;其次是數據譯碼模塊(DD),此模塊實現將原始的十進制(BCD)碼轉換成用于LCD 顯示的代碼;最后是LCD 顯示輸出模塊(LCM)模塊。

3 各組成模塊設計

3.1 二進制-BCD 轉換電路模塊(BITBCD)

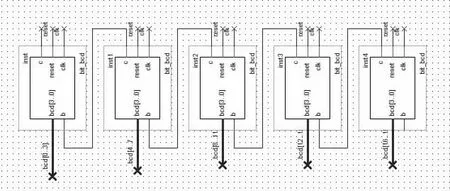

DIN[19..0]是20 位二進制的BIT 輸入,clk 是移位時鐘信號,RESET 為復位信號。它的內部包含有五個BIT-BCD 單元,見圖2。

圖2 五個BIT- BCD 單元

每個單元負責一位BIT、BCD 數碼的移位和實施BIT- BCD 轉換的加3 或加0 運算[1]。轉換過程開始后,先復位,并行輸入20 位二進制數的BIT 碼。然后,在每次奇次時鐘到來時五個單元各自進行加3 或加0,每次偶次時鐘到來時實施移位。經過了40 個時鐘,20 次移位和運算完成整個轉換過程。

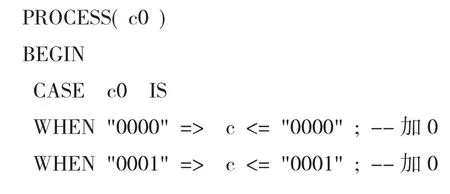

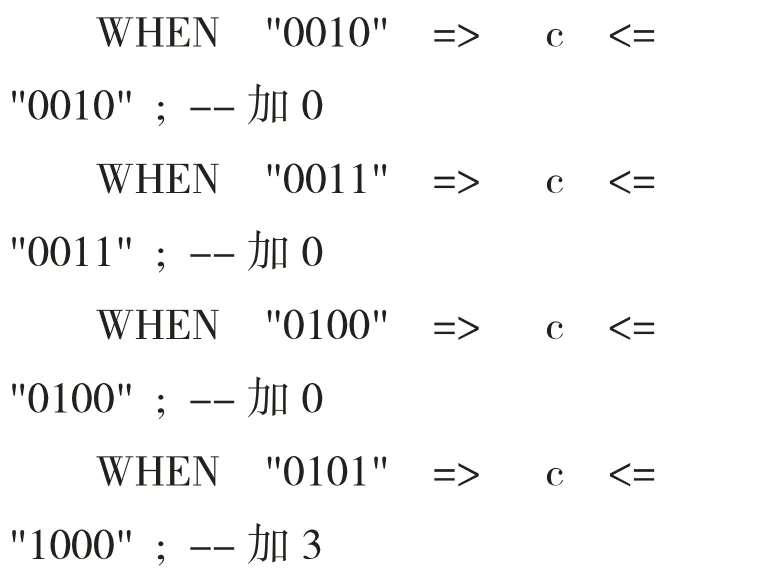

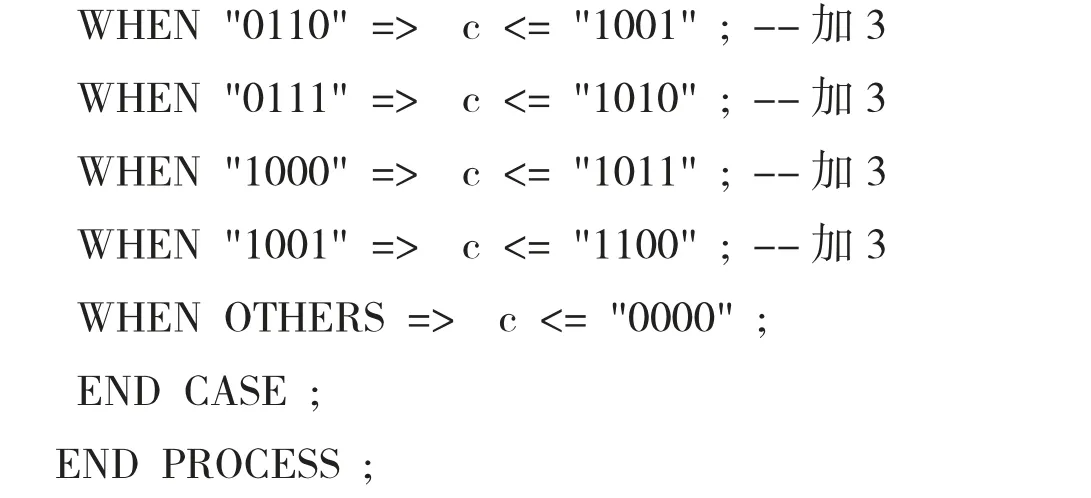

其中,BIT- BCD 單元的加3 或加0 進程VHDL代碼如下[3]:

在上面例子的BCD 邊的每個字節是(0,0,0,0)-(0,1,0,0)這幾個值時,向左邊移動一位后,沒有對高一位的進位,而且本位最大也符合十進制的表達形式,故加0,即保持不變即可。

在 BCD 邊的每個字節是(0,1,0,1)-(1,0,0,1)這幾個值時,向左邊移動一位后,最少也存在對高一位的進位,進位是逢十進一,所以要進行修正。修正的方法就是加3 后再移位。

以后每次移位都遵守同樣的規律,移動20 次后,即完成轉換過程。

3.2 數據譯碼模塊(DD)

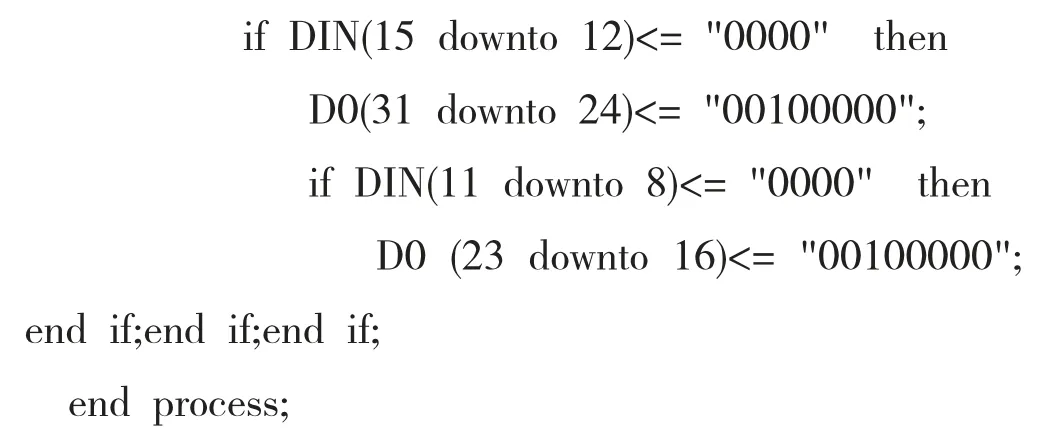

此模塊將信號DIN (19 downto 0) 中的十進制(BCD) 碼轉換成用于LCD 顯示的代碼信號D0(39 downto 0),轉換時要考慮整數部分第一位不為零的數字前的零不要顯示。其主要VHDL 代碼如下:

--整數部分第一位不為零的數字前的零不要顯示。

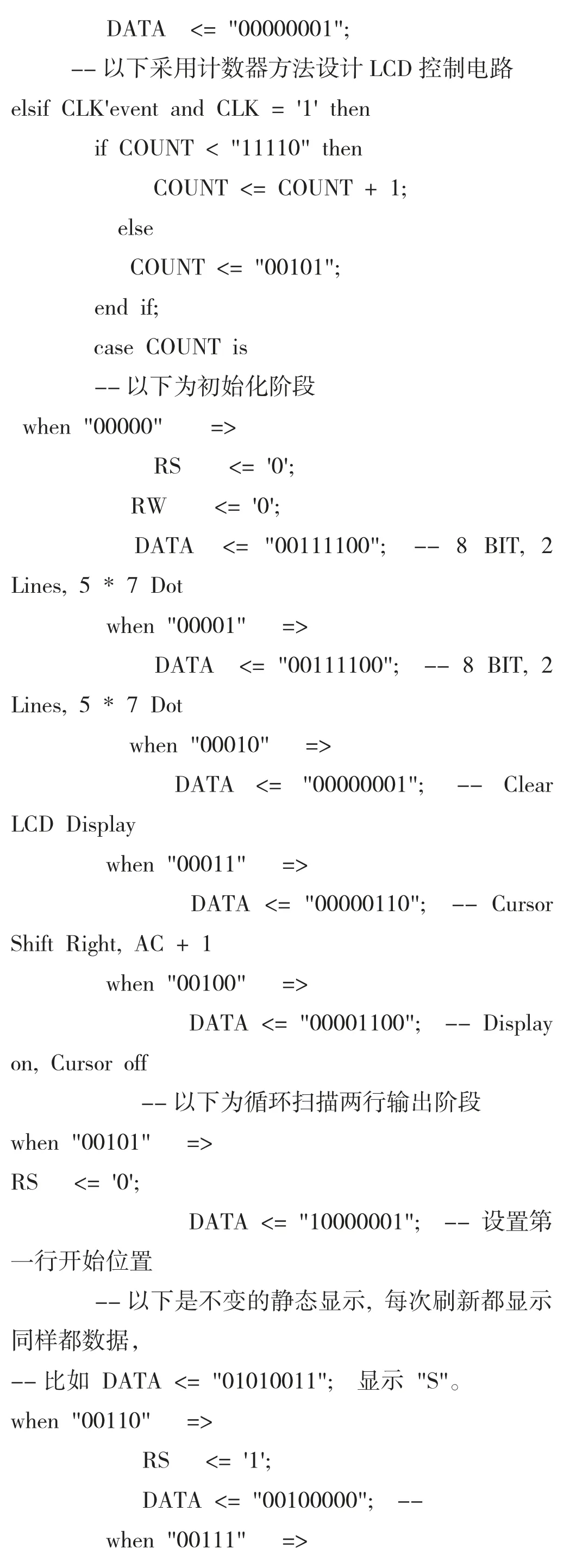

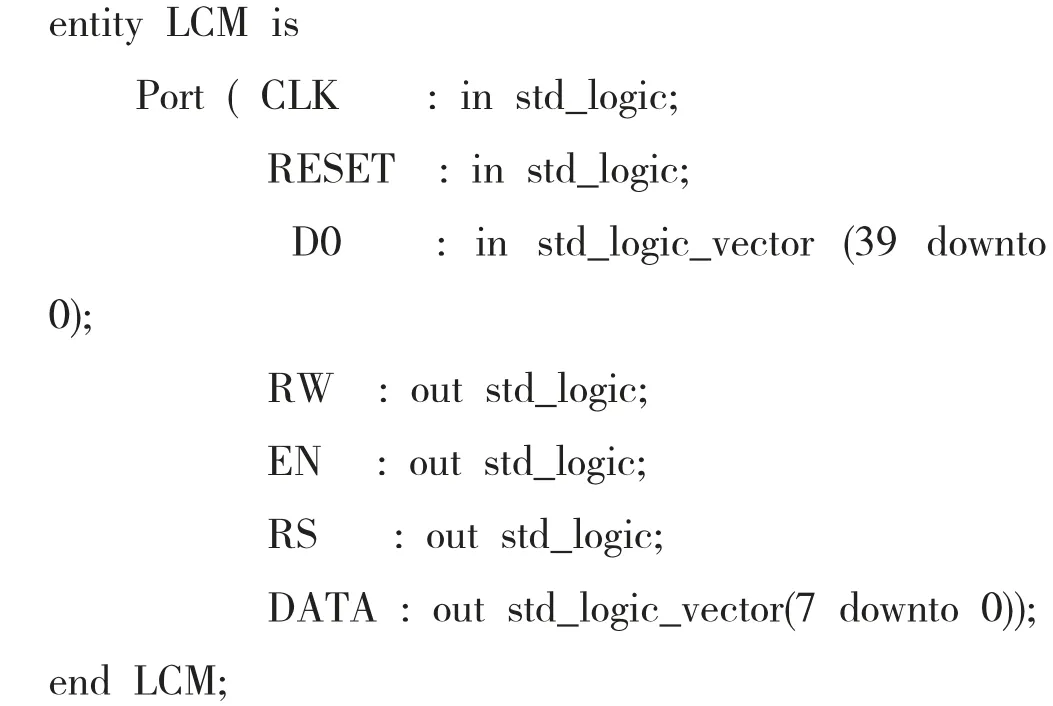

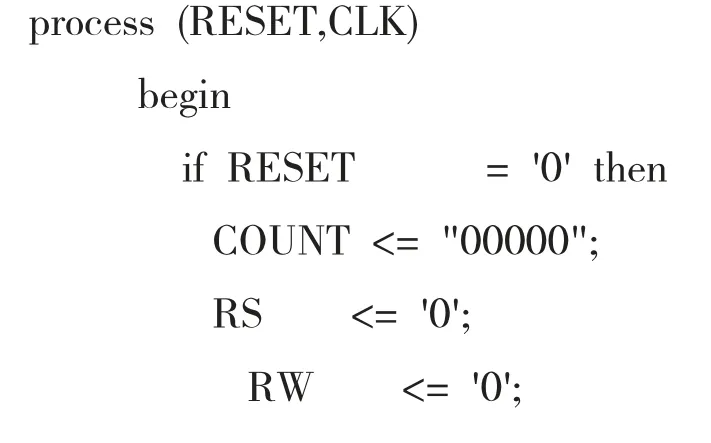

3.3 LCD 顯示輸出模塊(LCM)

LCD 控制過程有兩階段:初始化階段和循環掃描兩行輸出階段;有一經顯示就不變的靜態顯示,有需要不斷刷新的動態顯示。LCD 控制電路設計方法采用計數器方法。

其主要VHDL 代碼如下:

實體聲明:

主要進程:

在基于FPGA 的數字系統設計中,經常涉及到數據輸出顯示電路。而我們的設計經驗表明應用EDA工具能方便地設計數據輸出顯示電路,特別是采用計數器描述顯示驅動的方法,具有設計可讀性及可遷移性,不失是一種好方法[4]。