基于FPGA 的通用多路視頻輸入處理系統設計

宋長駿湯勇明

(東南大學顯示技術研究中心,江蘇 南京 210096)

隨著高清顯示器的普及,全景顯示、視頻融合、畫中畫等顯示應用越來越多。這類視頻拼接或視頻融合的設計中都有多路視頻同時輸入后的處理問題[1]。

本文依托FPGA 硬件平臺,在多視頻輸入情況下,規劃對應的多時鐘域處理方案,建立通用的視頻緩沖控制模式,為后續實現視頻縮放拼接、畫中畫顯示等功能提供解決方案。

本文工作分為兩個部分:第一,規劃了多視頻輸入處理方案,設計多視頻源的時序緩沖控制機制,利用全局緩沖減少關鍵時鐘信號的傳播延時,使用FIFO 實現跨時鐘域信號同步,并設計仲裁策略使多路視頻流共享存儲資源。第二,在FPGA 硬件驗證平臺上實現緩沖控制機制。基于FPGA 平臺和硬件編程設計實現之前的多視頻輸入緩沖控制模式。借助于多路視頻緩沖模式實現了四進一出的視頻拼接、畫中畫疊加等顯示功能,在12.5 GB/s 存儲帶寬條件下支持了4 路1080P60 幀的視頻輸入和1 路輸出。

1 多視頻源緩沖機制設計

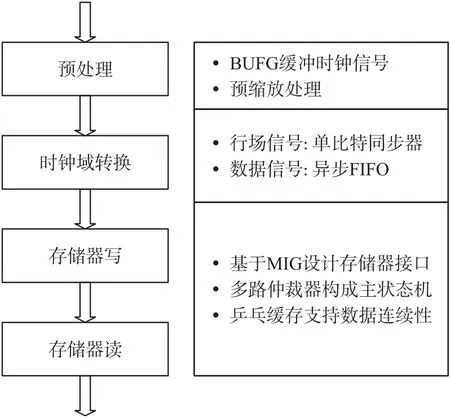

因為FPGA 片上存儲資源十分有限,視頻處理系統對視頻數據流輸入的緩沖,主要是依托外部存儲器[2]。多視頻輸入緩沖機制設計,按照視頻處理的流程分階段討論,視頻緩沖處理過程可劃分為如下四個階段:預處理階段,時鐘域轉換階段,存儲器寫階段和存儲器讀階段。

在預處理階段,完成對輸入時鐘的緩沖處理和視頻圖像的縮放預處理。時鐘信號具有高扇出的特點,采用FPGA 全局時鐘資源驅動高扇出的時鐘信號。對于每路視頻流,可以在各自的時鐘域內執行縮放預處理,縮放處理主要指縮小,圖像的縮小操作不需借助外部存儲器,可以用降采樣的方式簡單實現[3],從而可以降低對存儲器的帶寬需求。

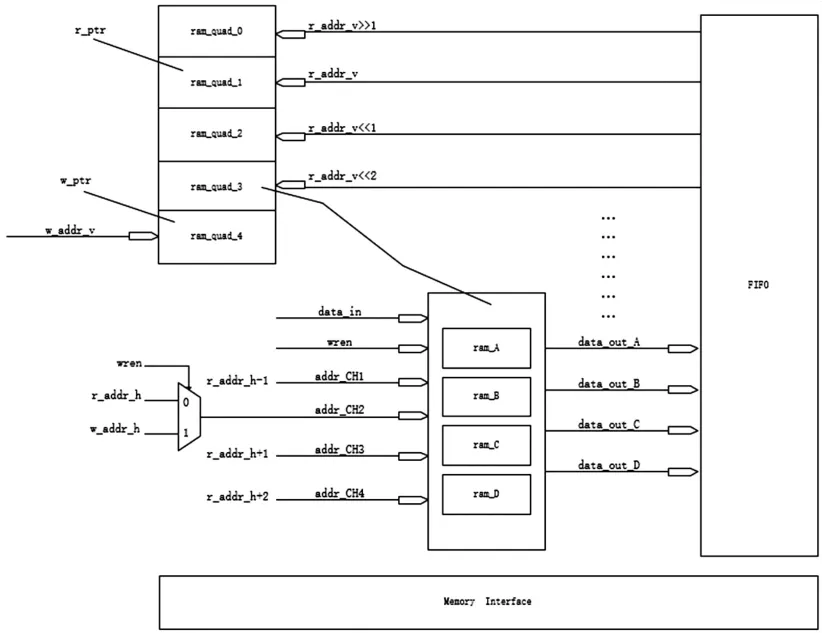

圖1 多視頻輸入處理機制

第二個階段是時鐘域轉換階段。各路視頻流有著獨立的像素時鐘,需要將信號從輸入視頻流時鐘域同步到系統工作時鐘域。對于單比特信號的跨時鐘同步,可使用打拍法實現,將兩個或多個觸發器串聯。在大多數多時鐘域設計里,兩級的同步電路足以避免亞穩態的出現[4]。多比特的信號跨時鐘同步多使用握手法和異步FIFO 法,相比于握手法,異步FIFO 法用更多的資源換取更高的傳輸速度[5]。

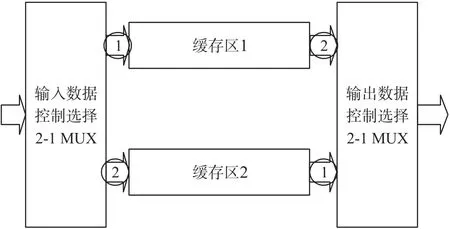

之后是存儲器寫和存儲器讀階段。在存儲器寫階段,系統將輸入數據寫入存儲器。寫入的數據在讀階段讀出,交付給后續的算法處理和顯示輸出。在寫和讀階段,需要實現存儲器讀寫邏輯。本文設計使用DDR3 作為存儲芯片。多路視頻流需要訪問存儲器,而存儲器是單端口的,所以設計一個多路復用器是有必要的。多路仲裁策略包括先到先得服務調度,優先級調度,和輪詢調度策略[6]。為了保證視頻數據的連續性,使用了乒乓緩存策略[7],在存儲器開辟兩塊緩沖區域,一個寫入數據,一個數據被讀出用以后續處理。通過一對2-1 選擇器,每次處理完成后交換功能。以掃描顯示為例,使用兩個幀緩存,當一個在掃描輸出的時候,另一個在改寫數據.到下一個周期改寫好數據的一幀作掃描輸出,而另一個幀緩存改寫數據.總之是一個在接收數據一個在處理,處理完后兩個再交換。從最后的輸出來看,保證了數據的連續性。

圖2 乒乓緩存策略

2 系統的FPGA 實現

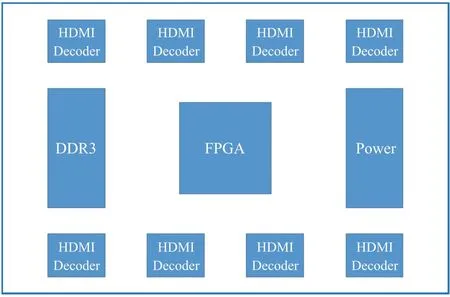

2.1 系統硬件電路

系統使用Xilinx 的XC7K325T FPGA 芯片,硬件板卡搭載了4 對HDMI 編解碼芯片,編碼芯片型號為ADV7511,解碼芯片型號為ADV7611,存儲芯片使用MT8KTF51264-DDR3 芯片[8]。編解碼芯片支持1920×1080P 60Hz 的HDMI 視頻編解碼,系統只需要處理RGB 行場信號。DDR3 芯片提供了12.5 GB/s 的帶寬資源。

圖3 硬件平臺架構布局

2.2 緩沖控制模式的硬件實現

緩沖控制模式圍繞著存儲器進行設計。Xilinx公司已提供DDR3 控制器IP[9]。IP 支持上電后對DDR3 控制寄存器做預配置操作,在使用DDR3 執行讀寫操作過程中可自動進行預充電以及自刷新等操作而無需用戶單獨控制,使用該控制器只需按照接口協議發送控制信號和讀寫數據即可。可直接集成到本系統中使用[10]。

DDR3 存儲器位寬為64 bit,數據讀寫速率設置為1 200 MB/s,設置8 突發寫長度(burst lenth),一次讀寫操作存儲512 bit 的數據。用戶時鐘接口速率為150 MHz,每個時鐘節拍有512 bit 數據被寫入或讀出DDR3。由于該用戶時鐘與模塊外部邏輯時鐘為異步時鐘,因此需要對數據做跨時鐘域同步。DDR3 讀寫電路架構如圖4 所示。

圖4 DDR3 讀寫電路架構圖

多路輸入數據通道讀寫需要對DDR3 存儲資源分時復用,因此需要設計狀態機切換數據通道。全局狀態機為多通道數據仲裁器,實現數據通道調度切換,局部狀態機為讀寫控制器,負責生成DDR3 控制IP 的讀寫信號。

2.3 視頻處理系統的時序約束優化

當不同觸發器之間時鐘信號延遲越小,其電路最大運行頻率越高[11]。Xilinx 7 series FPGA 設置有多種針對時鐘信號傳輸的專用路徑。

全局時鐘緩沖器(Global Clock Buffers,BUFG)輸入端為時鐘信號,輸出端為全局時鐘網絡。BUFG可以驅動FPGA 所有邏輯資源、RAM 資源和DSP 資源,亦可驅動其他時鐘電路結構。由于BUFG 驅動端到達FPGA 任意一處資源的路徑通道經過專門設計,因此經過BUFG 時鐘網絡的時鐘信號到達不同驅動端的時鐘抖動(clock jitter)和時鐘偏移(clock skew)極小[12]。

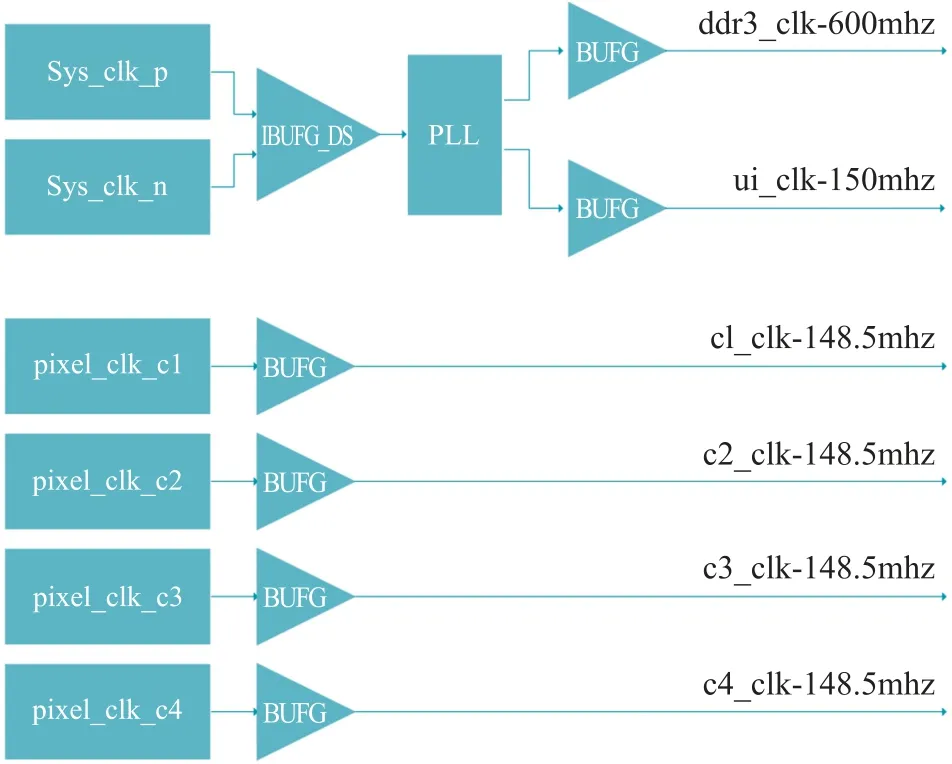

系統輸入時鐘包括200 MHz 差分時鐘sysclk 和各路HDMI 解碼后的148.5 MHz 像素時鐘pixel_clk_ci(i取0,1,2,3)。200 MHz 差分時鐘用于DDR3 IP 控制器,通過PLL 電路生成600 MHz 的DDR3 運行時鐘ddr3_clk 和150 MHz 用戶接口時鐘ui_clk,像素時鐘用于實時處理視頻流數據,像素時鐘的引入同樣經過一級PLL 電路用于穩定時鐘信號,生成新的穩定像素時鐘ci_clk。因為系統占用邏輯資源分布遍及整個FPGA,因此為避免時鐘偏移問題,所有經過PLL 后生成的時鐘信號都要經過BUFG 結構[13]。圖5 描述了本系統的時鐘樹設計。

圖5 系統時鐘樹

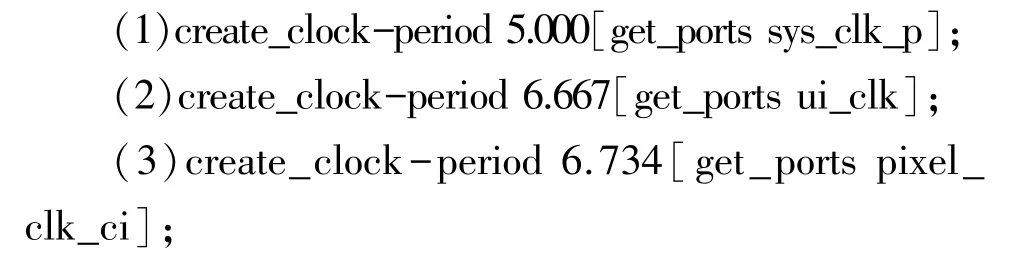

通過在xdc 文件中添加時序約束語句可令軟件在綜合電路的時候優化結構設計,避免時序邏輯電路內組合邏輯鏈過長導致時序邏輯電路不滿足建立時間和保持時間,約束語句如下:

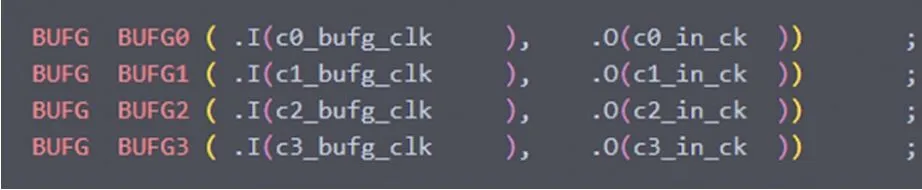

高扇出信號是指的某一信號被過多的邏輯資源同時使用,信號到達不同邏輯塊的時間不同可能導致時序不收斂問題,因此需要對此類信號做單獨處理。

本文設計中的高扇出信號主要為時鐘信號,對于高扇出信號可利用BUFG 驅動,Xilinx 原語聲明使用BUFG 驅動信號方式如圖6 所示。

圖6 BUFG 例化

2.4 跨時鐘域信號同步設計

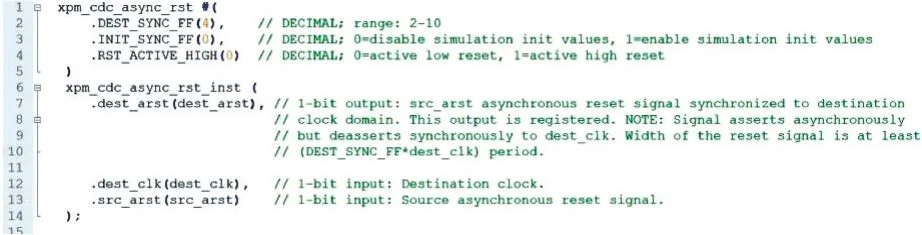

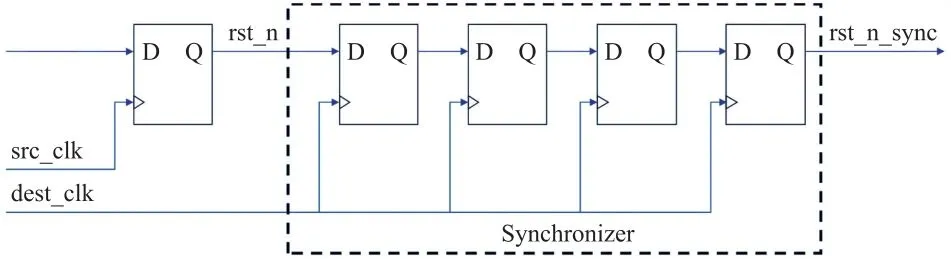

系統中有多個異步時鐘域,包括以HDMI 接口輸入的像素時鐘為源的時鐘域和以系統200 MHz差分時鐘輸入為源的時鐘域。不同時鐘域之間的信號交互必須同步,否則會導致出現亞穩態問題。對于多位數據,通過異步FIFO 進行數據同步。比如DDR 接口和外部數據通過異步FIFO 進行數據交互;對于單比特信號,如復位信號和控制信號,可以通過打拍法來進行,Xilinx 提供單bit 異步信號同步化原語[14-15],用法如圖7 所示。

圖7 使用XPM 原語例化同步器

綜合后電路如圖8 所示。

圖8 單比特同步器電路

3 系統搭建與測試

3.1 系統搭建說明

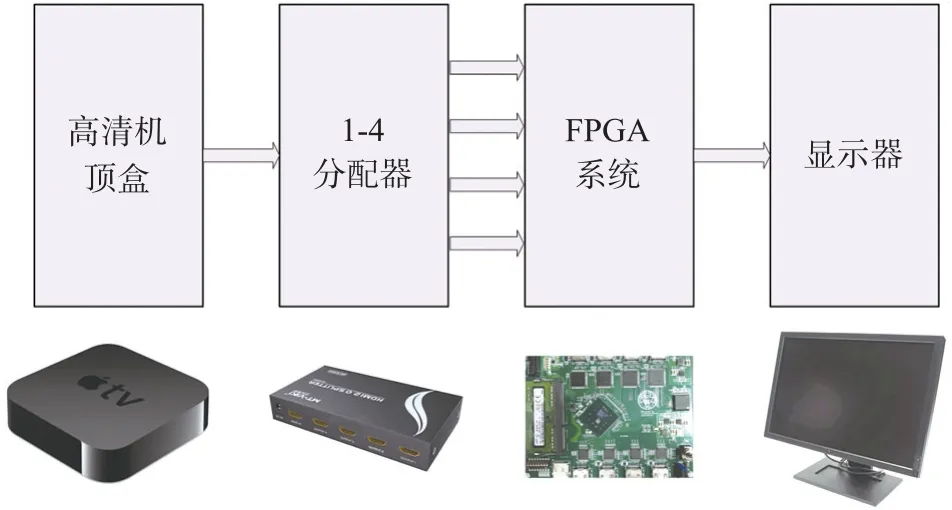

本系統支持4 路全高清視頻輸入和1 路輸出。系統采用高清網絡機頂盒作為視頻源,該視頻源可以提供1920×1080@60 Hz 的視頻數據輸出。通過1 進4 出的HDMI 矩陣輸出為4 路獨立的視頻源,將這4 路視頻數據接入本文設計的多視頻源處理系統,系統輸出的視頻連接顯示器進行顯示。具體連接情況如圖9 所示。

圖9 測試平臺示意圖

3.2 系統功能指標測試

本系統在DDR3 芯片提供的12.5 GB/s 存儲帶寬條件下,接收4 路1920×1080@60 Hz 視頻輸入,輸出1 路視頻。實現了視頻拼接與疊加等顯示功能。

圖10 系統功能測試

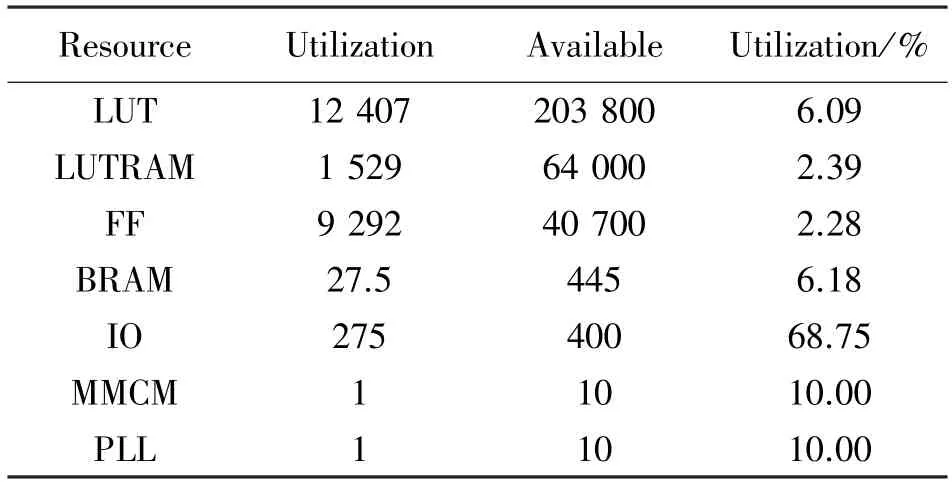

系統對FPGA 資源占用不多,僅使用了7K325芯片內部6.09%的LUT、2.28%的FlipFlop 和6.18%的BRAM,表1 具體給出了系統資源使用。

表1 系統資源使用

4 結論

本文依托FPGA 硬件平臺,在多路高清視頻輸入情況下,提出了通用的視頻緩沖控制設計,為后續實現視頻縮放拼接、畫中畫顯示等功能提供解決方案。

本文工作分為兩個部分:第一,規劃了多視頻輸入處理方案,針對視頻輸入處理流程,設計通用視頻緩沖控制機制。包括在預處理階段全局緩沖時鐘信號,在視頻時鐘域內執行縮放預處理;在跨時鐘同步階段利用同步器和異步FIFO 傳遞信號;在存儲器寫入讀出階段,設計多路調度機制和使用乒乓緩存策略。第二,基于FPGA 平臺硬件實現本文的多視頻輸入緩沖控制模式,并進行時序電路優化。實現四進一出的視頻拼接,畫中畫疊加顯示功能,在12.5 GB/s存儲帶寬條件下,支持4 路1080P 60 幀的視頻輸入和1 路輸出。

本文將多視頻應用中的多輸入視頻緩沖處理這一部分單獨做研究,探討緩沖控制機制的實現,提出的電路設計可應用在諸多應用中,具備實用性與通用性。