電力半導體場效應管瞬態(tài)響應特性研究

鞠 晨

(國能神東煤炭集團公司,陜西 神木 719315)

在電力半導體器件中,電力半導體場效應管(MOSFET)由于其獨特的高輸入阻抗、低驅動功率、高開關速度等特點,使得其在開關電源、馬達驅動、電機調速、不間斷電源、逆變器等各種電力電子設備中得到廣泛應用[1-3]。隨著工藝的不斷發(fā)展,電力半導體場效應管集成度的不斷提高,單胞的尺寸越來越小,加之該類器件經(jīng)常工作在快速開關轉換、大電流的狀態(tài)下,在實際使用過程中,其可靠性問題獲得了研究人員的普遍關注[4-5]。

開關損耗過大導致的功率燒毀是造成電力半導體場效應管失效的主要原因之一。為了從芯片級有效的改善電力半導體場效應管在點火控制器、開關電源等電路系統(tǒng)中的開關性能,并提高電力半導體場效應管的使用可靠性,利用TCAD半導體器件仿真軟件,在擊穿特性、輸出IV特性、轉移特性等靜態(tài)特性滿足電參數(shù)指標要求的前提下,對電力半導體場效應管的使用條件和結構參數(shù)進行優(yōu)化。詳細地分析了不同測試條件(柵極脈沖電壓、漏源電壓、柵極電壓脈沖寬度及占空比)、不同結構參數(shù)(多晶硅窗口區(qū)寬度(LW)與多晶硅區(qū)寬度(LP)的比例、N型外延層摻雜濃度、源極金屬芯片的覆蓋面積比例、柵氧化層厚度)對器件柵充電時間及器件開通時間的影響。

1 場效應管單元結構參數(shù)及物理模型

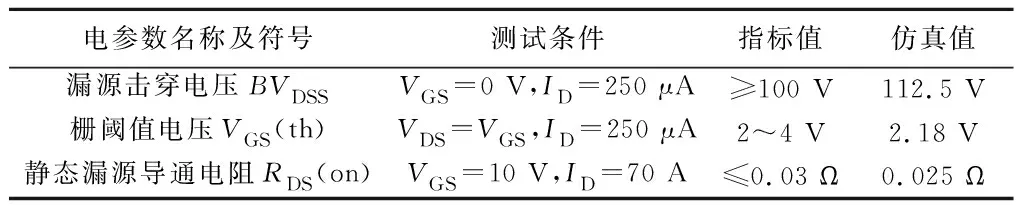

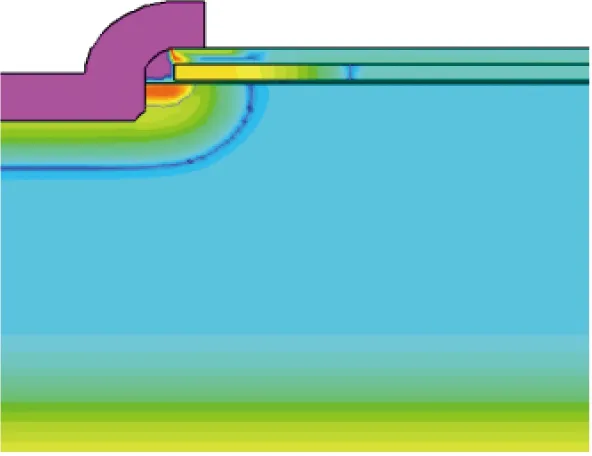

根據(jù)電參數(shù)指標(表1)的要求,利用TCAD半導體器件仿真軟件對電力半導體場效應管單元結構進行設計。設計得到的結構參數(shù)為:采用平面柵、槽型源區(qū)結構,單胞為條形,單胞半寬度為10 μm,多晶硅區(qū)半寬度(LP)為7 μm,窗口區(qū)半寬度(LW)為3 μm,溝道長0.92 μm。N型外延層晶向為<100>,厚度為7 μm,摻雜濃度為1×1015cm-3,外延層少子壽命為0.1 μs。P體區(qū)結深為1.81 μm,溝道表面平均濃度1.5×1017cm-3。N+源區(qū)結深為0.48 μm,表面濃度為3.5×1019cm-3。柵氧化層厚度為60 nm,多晶硅柵厚度為0.35 μm,多晶硅柵極集成防靜電二極管,多晶硅防靜電二極管PN結兩側雜質濃度由N+源區(qū)、P體區(qū)雜質橫向擴散濃度決定。源極引線孔半寬度為2.5 μm,源區(qū)槽深度為0.8 μm。

表1 電力半導體場效應管電學參數(shù)指標Tab.1 Electrical parameters of power semiconductor MOSFET

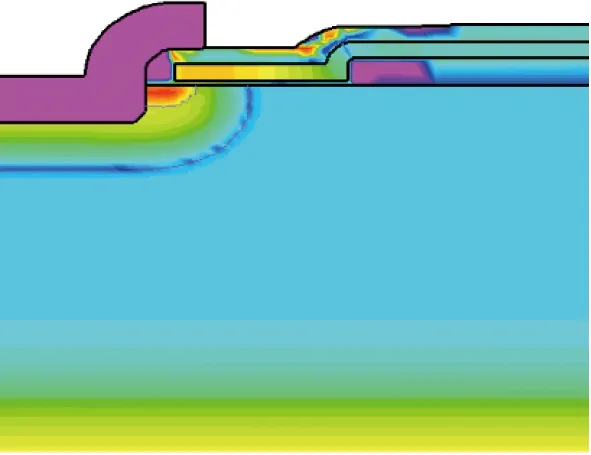

電力半導體場效應管半單胞結構如圖1所示。仿真得到的器件輸出特性均滿足產(chǎn)品的電參數(shù)指標要求,表明器件結構參數(shù)設計較合理。基于上述設計得到的單元結構來對器件的開通性能及結構參數(shù)進行仿真研究。

圖1 電力半導體場效應管半單胞結構Fig.1 Power semiconductor MOSFET semicell structure

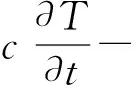

仿真過程中,復合模型考慮了與摻雜濃度相關的SRH復合和俄歇復合;遷移率模型考慮了與溫度、摻雜濃度、橫向及縱向電場相關的載流子遷移率模型。還考慮了重摻雜引起的禁帶變窄效應和能帶簡并效應。對電力半導體場效應管進行瞬態(tài)特性仿真時還需要考慮器件的自熱效應。計算由自熱引起的器件內部的溫度分布需要求解下面的熱傳導方程[6-8]:

(1)

式中,T為熱力學溫度;c為晶格熱容;k為熱導率;Pn和Pp分別為電子和空穴的絕對熱電功率;φn和φp分別為電子和空穴準費米勢;Jn和Jp分別為電子和空穴電流密度;κB是玻爾茲曼常數(shù);EC和EV分別為導帶底和價帶頂能級;q為基本電荷;R為復合率。

為了精確仿真自熱效應對電力半導體場效應管瞬態(tài)特性的影響,利用非等溫能量平衡傳輸模型模擬載流子的輸運過程。非等溫能量平衡傳輸模型對漂移—擴散模型在非等溫情況下進行了擴展,它考慮了晶格溫度梯度對電流密度的貢獻。考慮晶格溫度梯度影響后的電子和空穴電流密度方程為[6-8]:

Jn=-nqμn(▽φn+Pn▽T)

(2)

Jp=-pqμp(▽φp+Pp▽T)

(3)

式中,n和p分別為電子和空穴濃度;μn和μp分別為電子和空穴遷移率。

假設單元結構左、右邊界及上邊界與外界均無熱量交換。瞬態(tài)特性測試條件:柵壓脈沖上升、下降時間均為0.1 ns,脈沖寬度10 μs,占空比50%,空氣自然冷卻(空氣自然換熱系數(shù)為1/0.3)。

2 仿真結果與分析

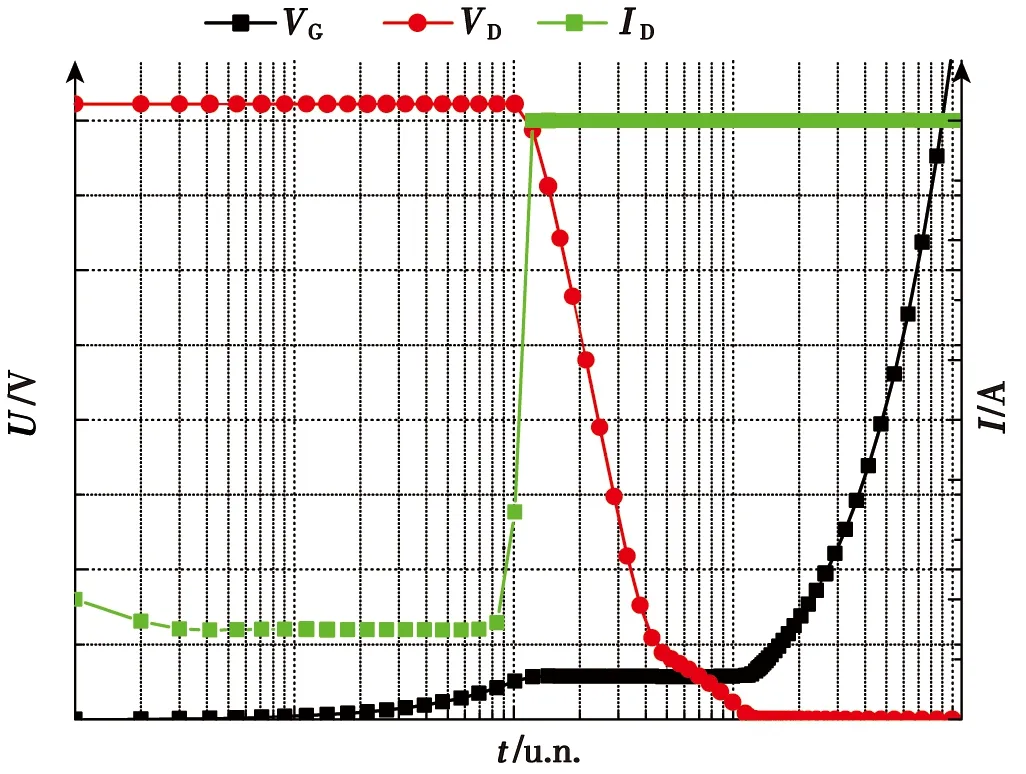

電力半導體場效應管的導通過程電流電壓曲線如圖2所示,測試電路為鉗位非感性負載電路。電力半導體場效應管的導通過程分為3個階段。第1階段:開通延遲階段(開通延遲時間),柵極驅動電壓從0上升,對柵源電容充電,該階段柵源電壓幾乎線性上升,柵源電容越小,柵源電壓上升越快。第2階段:開通上升階段(上升時間),電力半導體場效應管的柵源電壓達到閾值電壓,漏極電流開始上升;漏源等效輸出電容會對器件容性放電,漏源電流上升,漏源電壓下降。同時受到柵漏反饋電容的影響,柵源電壓的上升速率非常平緩(平臺)。第3階段:漏源電容電荷放完,漏源電壓近似為0,并保持不變;反饋消失。柵源電壓升高到開路脈沖,進入穩(wěn)態(tài)導通期。由圖2可見,在柵源電壓平臺階段,漏極電流上升的速度是漏極電壓下降速度的幾倍,導致器件開通功率損耗的增加。

圖2 電力半導體場效應管的導通過程電流電壓曲線Fig.2 Output characteristics of power semiconductor MOSFET during conduction

電力半導體場效應管在導通的3個階段中,單胞內部電流線分布的變化如圖3所示。當柵源電壓較低(圖3(a),第1階段)時,溝道尚未形成,漏源電壓反向施加在P體區(qū)與N-外延層形成的PN結上,電流較小,為PN結泄漏電流,大部分流經(jīng)P體區(qū)與外延層在表面處的結邊緣。隨著柵源電壓的增大(圖3(b),第2階段),柵源電壓大于器件閾值電壓,漏源電流由兩部分組成,一部分為流經(jīng)P體區(qū)與N-外延層形成的PN結的反向泄漏電流,另一部分為流經(jīng)溝道(P體區(qū)表面反型層)的溝道電流。隨著柵源電壓進一步增大,P體區(qū)表面反型程度進一步加強,溝道電阻進一步減小,導致PN結反向泄漏電流進一步減小,溝道電流進一步增大。最終,電力半導體場效應管電流全部為溝道電流(圖3(c),第3階段)。

圖3 電力半導體場效應管導通過程Fig.3 Power semiconductor MOSFET conduction process

仿真得到的漏源電流對器件開通特性的影響如圖4所示。柵源電壓為15 V,柵源電阻為5 Ω,漏源電壓為80 V。由圖4器件開通時間曲線可見:隨著漏源電流的增大,器件開通時間隨之增長,對導通延遲時間的影響較顯著。當電力半導體場效應管處于飽和導通狀態(tài)時,漏源電流近似與柵源電壓的平方成正比。即漏源電流越大,溝道反型電荷密度越大,柵源電容的充電時間越長,器件導通延遲時間越長。且由于柵漏電壓和柵漏電容(柵漏電荷QGD)幾乎相同,因此柵源電壓維持恒定的時間(miller平臺時間)幾乎相同。因此,隨著漏源電流的增大,導通延遲時間隨之增大,上升時間變化幅度較小。

圖4 漏—源電流對電力半導體場效應管瞬態(tài)響應特性的影響Fig.4 Influence of drain-source current on transient response characteristics of power semiconductor MOSFET

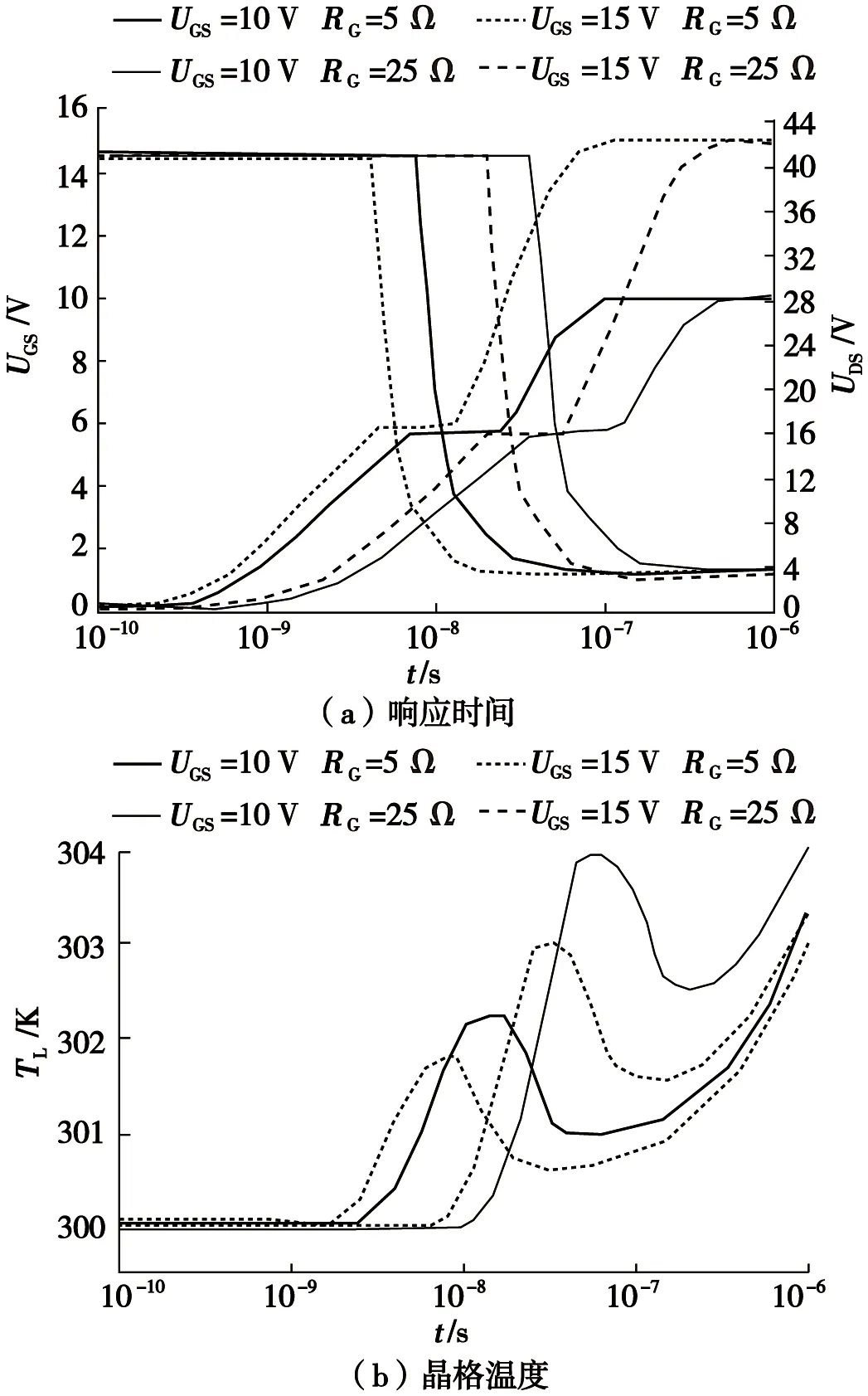

仿真得到的柵源電壓和柵源電阻對器件開通特性的影響如圖5所示。

圖5 柵—源電壓和柵極電阻對電力半導體場效應管瞬態(tài)響應特性的影響Fig.5 Influence of gate-source voltage and gate resistance on transient response characteristics of power semiconductor MOSFET

由圖5(a)可知,導通時間最短的情況為柵源電阻為5 Ω,柵源電壓為15 V情況,導通時間最長的情況為柵源電阻為25 Ω,柵源電壓峰值為10 V的情況。由圖5(b)可知,電力半導體場效應管開通時間越短,其開通過程中器件峰值晶格溫度越低。原因為:隨著柵源電壓的增大或/和柵源串聯(lián)電阻的降低,對柵源電容CGS的充電電流較大,柵源電容充電達到相同閾值電壓的充電時間縮短,因此器件導通延遲時間隨之縮短。電力半導體場效應管在開通過程中受到柵極—漏極電荷QGD的影響。QGD越大,UGS-QG波形中柵源電壓維持恒定的時間越長,漏源電壓從關斷電壓降低到飽和漏源電壓VDSsat(達到飽和狀態(tài))的時間越長。在柵漏電容相同的情況下(器件結構參數(shù)相同),柵源電壓越高,漏柵電壓越低,漏柵電荷越小,相應的柵源電壓維持時間(miller平臺)越短,因此,器件上升時間隨之縮短。漏極電流在miller平臺開始時出現(xiàn),且漏極電流上升的速度是漏極電壓下降速度的幾倍,器件上升時間越長,電力半導體場效應管開通損耗越大,器件產(chǎn)生大量熱量,開通過程中器件峰值晶格溫度越高。

仿真得到的不同多晶硅寬度LP對電力半導體場效應管輸出電流—電壓特性及開通時間的影響如圖6所示。窗口區(qū)寬度LW為2 μm,柵氧化層厚度為60 nm。由圖6(a)可知,當多晶硅寬度在4~7 μm內時,電力半導體場效應管導通電阻均滿足電參數(shù)指標要求。隨著多晶硅寬度LP的增大,電力半導體場效應管導通電阻隨之減小。當多晶硅寬度LP≤5 μm時,在相同的漏源電壓情況下,多晶硅寬度越大,漏源電流越大。當多晶硅寬度LP增大到6 μm時,在較低漏源電壓下,輸出特性曲線幾乎重疊在一起,而在漏源電壓較高時,多晶硅寬度越大,漏源電流越低,即出現(xiàn)了“電流飽和效應”。原因為:隨著多晶硅區(qū)寬度的增大,由溝道流出的電子電流在對晶硅區(qū)域中的輸運路徑發(fā)生了顯著變化,電子電流由溝道邊緣到漏極的輸運路徑展寬,等效于器件導通電阻減小。當多晶硅寬度較大(LP≥6 μm),且漏源電壓較高時,漏源電流減小的原因為:隨著多晶硅寬度的增大,P體區(qū)間距增大,P體區(qū)之間不能成為彼此的有效分壓環(huán),導致達到一定的漏源電壓下,P體區(qū)表面電場強度較大,電子遷移率在強電場下降低,導致隨著漏源電壓增大漏源電流減小的現(xiàn)象。

由圖6(b)開通特性可見:當LP=5 μm時,電力半導體場效應管閾值電壓較低,其導通延遲時間較短,為3.43 ns,其上升時間為9.59 ns。當LP=4 μm時,其導通延遲時間為4.39 ns,其上升時間為11.46 ns,當LP=6μm時,其導通延遲時間為4.49 ns,其上升時間為14.57 ns。當LP=7 μm時,其導通延遲時間為4.64 ns,其上升時間為17.81 ns。對于LP=4 μm,其導通時間為15.85 ns;對于LP=5 μm,其導通時間為13.02 ns;對于LP=6 μm,其導通時間為19.06 ns;對于LP=7 μm,其導通時間為22.45 ns。除LP=5 μm外,隨著多晶硅區(qū)寬度LP的增大,器件導通時間隨之增大。原因為:隨著多晶硅區(qū)寬度的增大,電力半導體場效應管閾值電壓增大,所需柵電荷較多,柵源電容充電時間較長,即器件導通延遲時間隨之增大。同時隨著多晶硅區(qū)寬度的增大,柵漏電容面積增大,在相同的漏源電壓情況下,柵漏電容較大,柵漏電荷QGD較多,從而導致柵源電壓維持恒定值的時間隨之增長,即器件上升時間隨之增長。

圖6 多晶硅柵極寬度對電力半導體場效應管電性能的影響Fig.6 Influence of polysilicon gate width on electrical performance of power semiconductor MOSFET

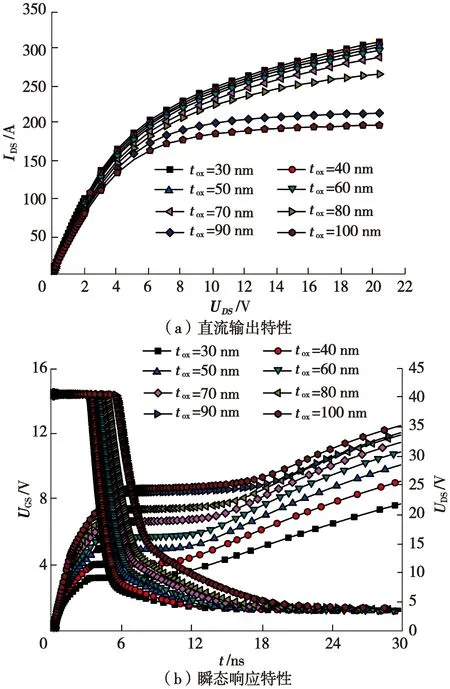

仿真得到的柵氧化層厚度對電力半導體場效應管電性能的影響如圖7所示。

圖7 柵氧化層厚度對電力半導體場效應管電性能的影響Fig.7 Influence of gate oxide thickness on electrical performance of power semiconductor MOSFET

圖7(a)為仿真得到的柵氧化層厚度tox對電力半導體場效應管直流參數(shù)的影響,在仿真過程中,多晶硅寬度LP為4 μm,多晶硅柵電極下的氧化層厚度均勻。由圖7(a)可見:柵氧化層厚度tox在30~100 nm內變化時,隨著柵氧化層厚度tox的增大,電力半導體場效應管導通電阻隨之增大。原因為:在相同柵源電壓下,隨著柵氧化層厚度tox增大,P體區(qū)反型層中電子濃度降低,等效的溝道電阻增大,從而導致電力半導體場效應管導通電阻增大。圖7(b)為仿真得到的均勻氧化層厚度對電力半導體場效應管開通時間的影響。由圖7(b)可見:在器件開通過程中,開通延遲時間和開通上升時間均隨著柵氧化層厚度的增大而增大,且增大幅度較大。原因:隨著器件柵氧化層的增大,器件的閾值電壓隨之增大,器件達到閾值電壓所需要的充電時間較長,導致器件開通延遲時間隨著柵氧化層厚度的增大而變長。隨著柵氧化層厚度的增大,器件導通電阻隨之增大,漏源等效電容放電的過程中所需要的放電時間增大,漏源電壓下降到穩(wěn)定電壓所需的時間較長,因此隨著柵氧化層厚度的增大,器件開通時間增大。當柵氧化層厚度為30 nm時,器件開通時間為10.8 ns,當器件柵氧化層厚度增大到100 nm時,開通時間增大到23.4 ns。器件的開通時間越長,開通過程中的功率損耗越大,器件的峰值晶格溫度越高。因此,為了降低器件的導通電阻和較短的導通延遲時間,在保證氧化層質量和成品率的前提下,需要減薄柵極氧化層厚度。

為了在不影響器件導通電阻和導通延遲時間的情況下,降低電力半導體場效應管的上升時間,即減小柵漏電容對開通時間的影響,器件結構可采用非均勻柵極氧化層結構,器件結構如圖8所示。

圖8 非均勻柵氧化層厚度電力半導體場效應管單元結構Fig.8 Power semiconductor MOSFET unit cell structure with non-uniform gate oxide thickness

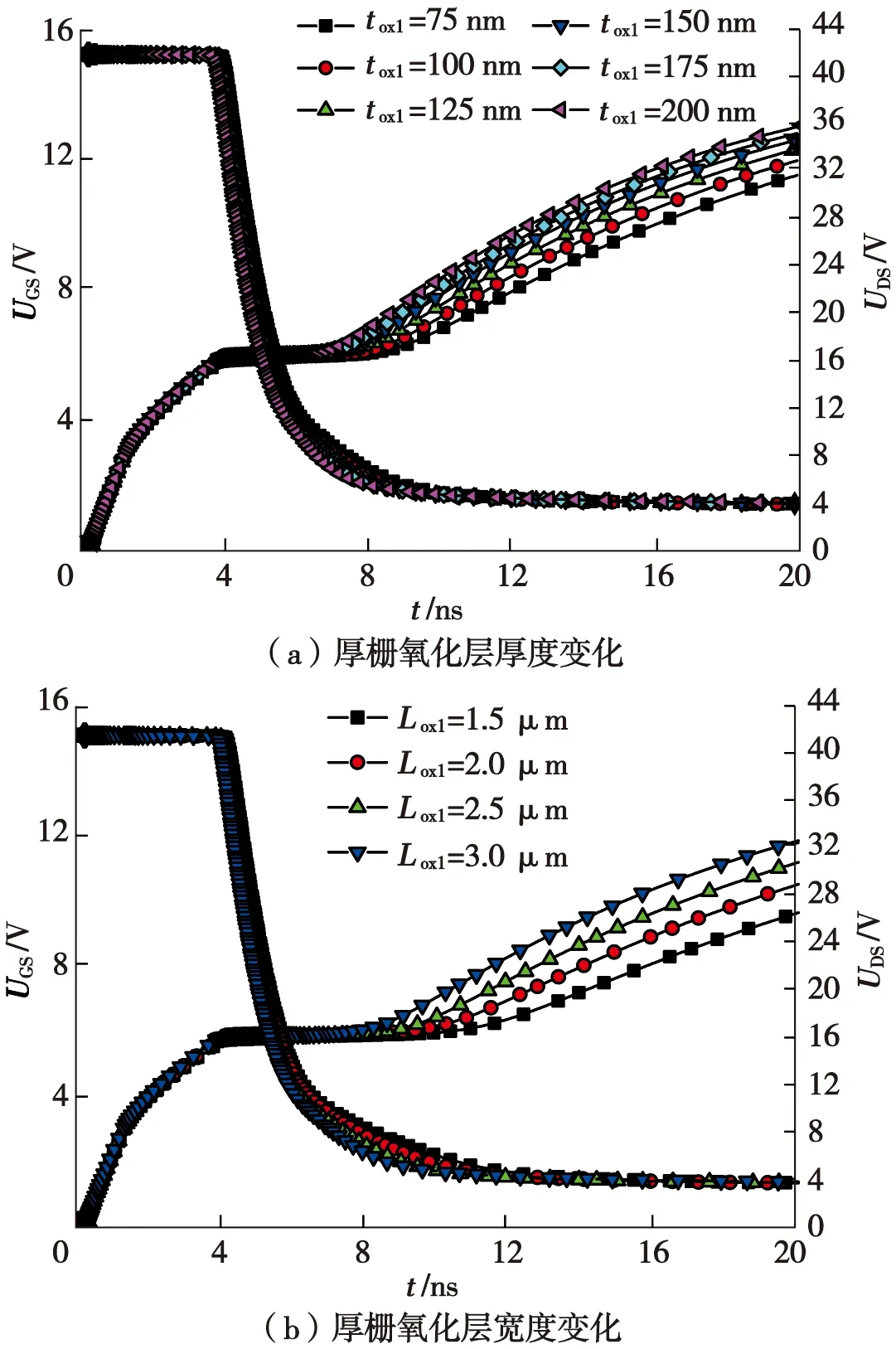

仿真得到的厚柵氧化層結構對電力半導體場效應管瞬態(tài)響應特性的影響如圖9所示。圖9(a)為仿真得到的當薄柵氧化層為60 nm,厚柵氧化層寬度為3 μm時,厚柵氧化層厚度變化對電力半導體場效應管開通時間的影響。由圖9(a)可見:隨著厚柵氧化層厚度的增大,電力半導體場效應管導通延遲時間基本相同,而上升時間隨之顯著降低,表明在一定程度增加厚柵極氧化層厚度有利于降低器件的開通時間。圖9(b)為仿真得到的當薄柵氧化層為60 nm,厚柵氧化層厚度為100 nm時,厚柵氧化層寬度變化對電力半導體場效應管開通時間的影響。由圖9(b)可見:隨著厚柵氧化層寬度增大,器件導通電阻越高,漏源等效電容放電時間越長。厚氧化層越寬,漏柵等效電容對柵源電容的充電時間影響越小,柵源電壓越快地達到閾值電壓,開通延遲時間越短。而對于開通上升時間,隨著厚氧化層寬度的增大,存在最小值。當Lox1為2.5 μm時,器件開通上升時間最短。表明該條件下器件在折衷miller耦合電容和導通電阻方面最優(yōu)。當Lox1為1.5 μm時,器件開通時間為12.5 ns;當Lox1為2 μm時,器件開通時間為11.5 μm;當Lox1為2.5 μm時,器件開通時間為11.1 ns;當Lox1為3 μm時,器件開通時間為11.4 ns。

圖9 厚柵氧化層結構對電力半導體場效應管瞬態(tài)響應特性的影響Fig.9 Influence of thick gate oxide structure on transient response characteristics of power semiconductor MOSFET

3 結論

本文利用TCAD半導體器件仿真軟件對電力半導體場效應管的瞬態(tài)響應特性進行了詳細研究。仿真結果表明,由于影響柵—源電容的結構參數(shù)對器件的直流參數(shù)影響較顯著,不能僅僅通過調整柵氧化層厚度、多晶硅柵極寬度等結構參數(shù)來改善開通性能。為了在不影響導通電阻和導通延遲時間的情況下,降低器件的上升時間,可采用非均勻厚度柵氧化層結構。適當提高柵—源電壓、減小柵極電阻可縮短導通延遲時間。增大柵—漏氧化層厚度、優(yōu)化柵—漏氧化層寬度可減小miller平臺時間,從而減小開通上升時間。