一種基于FPGA資源復用的時域脈壓方法

王輝輝 袁子喬 徐 偉

(西安電子工程研究所 西安 710100)

0 引言

雷達數字脈沖壓縮主要有時域和頻域兩種方法,時域脈壓處理方式更直接,處理效率要高于頻域脈壓,同時處理速度也快,頻域脈壓處理時間隨著處理長度的增加成對數增加,而時域脈壓處理時間只與濾波器階數有關,與輸入數據長度無關[1]。特別是當距離單元較大時,采用頻域實現運算過程復雜,延遲大[2]。FPGA在數字信號處理的硬件實現中扮演著重要角色[3],使用FPGA設計出特定的結構來實現具體的信號處理算法,能提高系統的算法實現性能和執行效率[4],因此對于實時性要求高的雷達系統,一般利用具有在線動態重構能力的FPGA平臺來實現時域脈壓。軟件化雷達通過開放式架構和軟件化設計能靈活地實現系統擴展、更新和升級[5],極大地增加了雷達靈活性。軟件化雷達存在功能可重構要求,需要重構多種可變波形,如果針對不同波形分別獨立設計時域脈壓,這將大大增加了FPGA的乘法器和存儲器資源。因此為滿足軟件對波形的可重構性,本文提出了一種基于資源復用的時域脈壓方法。該方法通過復用FPGA的乘法器和存儲器資源,重構濾波器系數和參數,能實現對多波形多波束多數據率的脈壓處理。

1 脈沖壓縮原理

系統輸入端信號為

x(t)=s(t)+n(t)

(1)

其中,s(t)為目標回波信號,n(t)為系統噪聲。s(t)的頻譜為

(2)

由匹配濾波理論可知,如果時域脈壓濾波器的頻率響應為:H(f)=S*(f)e-j2πft0,則濾波器輸出端的信噪比最大,響應的脈沖響應為

(3)

其中t0是濾波器的時延,因此時域脈沖濾波器的脈沖響應為收入信號的鏡像共軛。在忽略噪聲情況下,脈沖壓縮輸出為

y(t)=x(t)*h(t)

(4)

2 設計實現

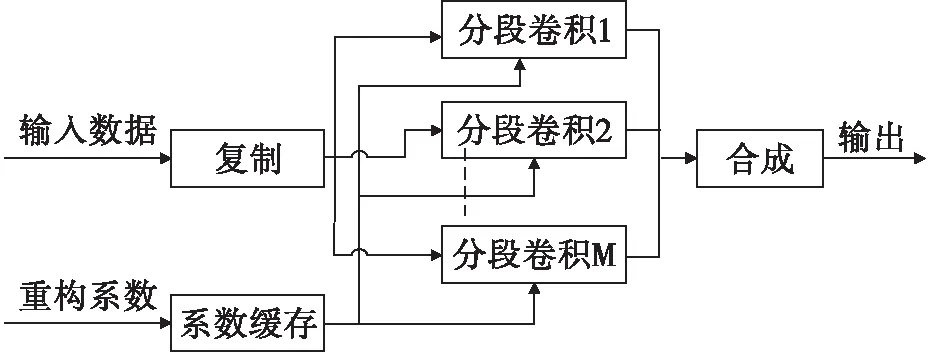

軟件可重構的脈壓面臨不同波形、不同數據速率、不同波束個數分時工作的可能,因此進入脈壓模塊的數據速率是不同的,波束個數也不同,但對于數據速率確定、波形樣式確定的工作模式,時域脈壓的匹配濾波器系數就是固定的,該數據速率該波形條件下的一個波束數據的時域脈壓實現所需的資源是固定的。時域脈壓采用濾波器進行處理,濾波器的階數和波形及采樣率是相關的。基于資源復用的時域脈壓處理流程圖如圖1所示,將輸入的數據進行復制分割得到多個數據段,每個段和對應的系數進行乘累加操作,最后將多段的結果合成輸出。通過系統控制重構系數,即可實現不同波形的脈壓處理。

圖1 資源復用時域脈壓處理流程圖

2.1 設計原理

基于Xilinx公司7系列FPGA的資源復用的時域脈壓詳細設計圖如圖2所示,首先對輸入數據進行緩存,計算并行處理通道個數,并初始化所有處理通道,然后將輸入數據寫入多個雙口RAM;其次進行數據讀處理,根據讀時間片產生讀地址和讀控制信號,控制數據從雙口RAM兩個口正序和反序對稱讀出,并對讀出的數據進行結構調整處理,使得多余的數據不參與計算,根據系統選擇重構濾波器系數和控制參數;一般來說,雷達系統為了節省系統資源,采用的波形一般都是奇對稱或偶對稱的,最后根據重構系數的對稱特性,對處理后的數據進行相應的預加處理,并將預加后的數據和對應的濾波器系數進行乘累加操作得到脈壓輸出,通過重構濾波器系數和控制參數可實現不同波形對相同乘法器的復用。

圖2 資源復用時域脈壓詳細設計

2.2 數據緩存

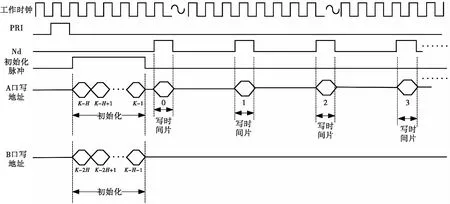

根據輸入數據速率、系統工作時鐘頻率以及時域脈壓濾波器階數這三個參數來計算需要并行處理的通道個數,一個通道對應一個雙口RAM。不失一般性,假定當前波形的脈沖寬度為L(μs),系統時域脈壓模塊的工作時鐘頻率為X(MHz),脈壓模塊輸入的數據率為Y(MHz),M=X/Y,M為大于等于1的正整數。根據波形的對稱特性,與當前波形相匹配的脈壓匹配濾波器的階數為:H=ceil(L×X/2),需要同時處理的通道個數為:N=ceil(H/M),ceil為向上取整。FPGA中存儲數據的雙口RAM的深度K應當大于L×X,并且K為2的整冪次方。由于存儲數據的雙口RAM不具備數據清零操作,為了不同的脈沖重復間隔(PRI)之間數據進行脈壓處理時互不影響,需要在一個新的PRI到來時,對雙口RAM進行清零操作,也就是將雙口RAM中的最后面的深度為L×X的緩存區置零。當PRI到來時,產生一個初始化脈沖,該脈沖的周期個數為H。為了減少清零時間,對N個雙口RAM的兩個輸入口A和B同時進行寫操作,A口寫地址從K-H開始寫,B口地址從K-2×H開始寫,這樣大大減少了清零的時間。當置零結束后,寫控制模塊控制數據按照X(MHz)的速率從緩存區讀出,數據的有效信號如圖3中的Nd信號所示,當有效信號為高電平時,將A口地址進行累加操作,增量為1,同時在寫時間片內將數據同時寫入N個雙口RAM的A口中去,完成數據的寫操作。在寫時間片內,B口不進行寫操作。數據寫緩存的操作時序見圖3所示。

圖3 數據緩存時序圖

2.3 數據讀處理

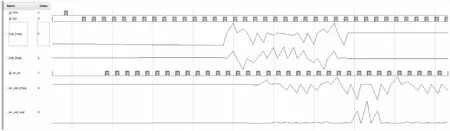

數據讀處理控制時序如圖4所示,當第一個輸入數據寫入N個雙口RAM中后,由讀控制模塊產生一個開始脈壓處理的標志信號start_flag,該信號在PRI脈沖到來時進行復位操作,也即將start_flag置為低電平。當第一個輸入數據的Nd到來后,將該信號置為高電平,高電平一直保持到下個PRI脈沖到來。在start_flag為高電平期間進行讀操作,每輸入一個新的數據也就是一個新的Nd到來時,需要對雙口RAM的A口和B口的讀地址賦初值。當第一個Nd到來時,第一個雙口RAM的A口和B口的初始化讀地址為:K-L×X+1和0;第二個雙口RAM的A口和B口的初始化讀地址為:K-L×X+1+(M-1)和K-(M-1);…… 依此類推,第N個雙口RAM的A口和B口的初始化讀地址為:K-L×X+1+(M-1)×(N-1),K-(M-1)×(N-1)。在Nd信號不為高且start_flag信號為高電平的讀時間片內,所有通道的雙口RAM的A口的讀地址進行累加操作,增量為1。所有通道的雙口RAM的B口的讀地址進行遞減操作,遞減量為1,如圖4所示。從第二個Nd信號到來開始,每當一個新的Nd信號到來時,所有雙口RAM的A口的讀地址在當前的基礎上減去一個固定值,該值為(M-2)。所有雙口RAM的B口的讀地址在當前的基礎上加上一個固定值,該值為M。然后將當前值作為A口和B口下一個讀時間片的初始值,當讀時間片到來時,所有RAM的A口的讀地址進行累加操作,增量為1,B口的讀地址進行遞減操作,遞減量為1。按照上述過程重復進行,由于在FPGA中地址是定點數,雙口RAM的A口和B口的地址循環范圍為0~(K-1),因此當地址為K-1時,如果地址進行自加1操作,則下一個地址變為0;當前地址為0,如果地址進行遞減1操作,則下一個地址變為K-1;因此通過循環地址的讀操作就可實現數據的正序列和反序列對稱輸出。在數據讀出后需要對數據進行整理,只對最后一個通道進行處理,其他通道數據保持不變。在所有的讀時間片內,都將最后一個通道的RAM的B口輸出數據的前H-(M-1)×(N-1)個數據保留,而該通道B口輸出的其他數據強制置零。這樣不管對于奇對稱還是偶對稱能保證一個完整的數據長度L×X被讀出來進行脈壓。數據整理模塊輸出數據時,讀控制模塊同時控制濾波器系數讀出,并將系數和數據同時送入乘累加模塊進行處理。

圖4 數據讀時序圖

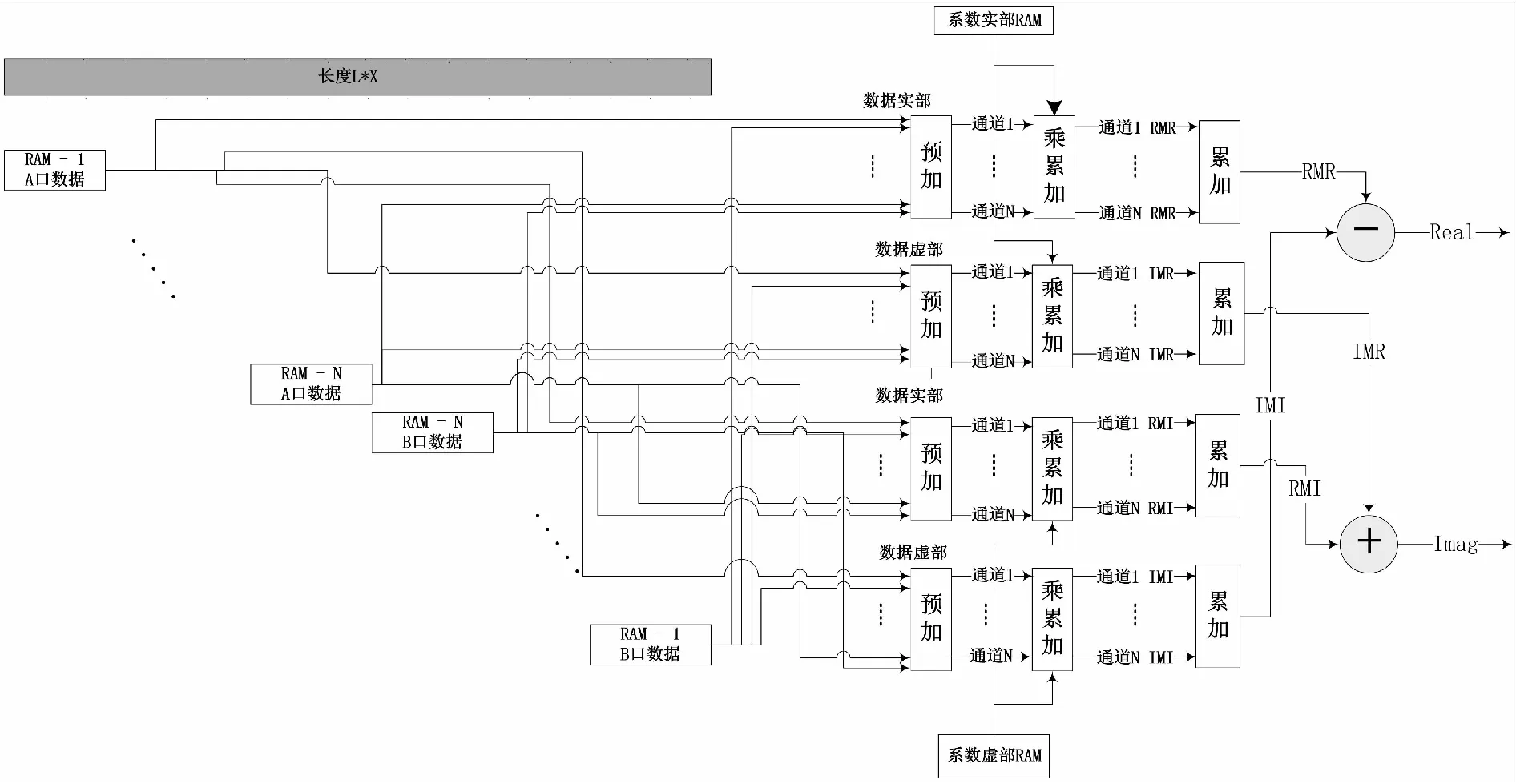

2.4 乘累加

本文中的乘累加模塊使用FPGA自帶乘累加的IP核,該IP核可以對輸入口A和D的兩路數據進行預加處理,然后將預加的結果和B口輸入數據相乘,相乘結果可以從C口輸入和下一個乘的結果進行累加操作并輸出,該IP核的原理圖如圖5所示。

圖5 乘累加器IP核原理圖

將同一個通道的A口和B口整理后的數據送入FPGA自帶的乘累加IP核的A口和D口,先進行預加處理,也就是將A口和B口對應的數據先進行加法計算。同時將系數從系數RAM中讀出,送入乘累加IP核的B口,預加的結果和C口對應的系數相乘得到第一個數據的乘結果,并在一個讀時間片內將相乘的結果反饋到乘累加IP核的C口,實現當前讀時間片內所有乘結果的累加,從而得到當前讀時間片內的當前通道的乘累加輸出結果,最后把N個通道當前讀時間片內的結果對應相加就得到了該讀時間片內最終的乘累加結果,也就是一個脈壓輸出值。數據和系數都為復數,因此一個通道需要四個乘累加器。

濾波器系數可通過軟件進行重構,由于劃分了N個通道,因此濾波器的系數存儲需要做特別的處理,濾波器系數矩陣按照M-1 行N列進行存儲,第一列存儲濾波器系數的1~M-1第二列存儲濾波器系數的M~2×(M-1),依此類推,第N列存儲濾波器系數的(N-1)×(M-1)+1~H,第N列未填滿的共(M-1)-(H-(N-1)×(M-1))-1 個數據進行補零處理,在重構不同濾波器系數時,只需要按照次規則生成對應系數矩陣,并將矩陣寫入FPGA的內部存儲器RAM中即可。

讀控制模塊在每個讀時間片內對該RAM進行讀取,按照當前波形對應的脈壓濾波器系數存放的地址依次讀出濾波器系數。濾波處理是個線性卷積的過程,為直觀可見,本文僅以一個長度為L×X的完整輸入數據的乘累加過程示例,乘累加數據控制流程實現如圖6所示。在每個讀時間片內,將第一列系數和第一個通道的預加后的數據依次相乘并進行乘累加,第二列系數和第二個通道讀時間片內的預加后的數據依次相乘并進行乘累加,依此類推,第N列系數和第N個通道讀時間片內的預加后的數據依次相乘并進行乘累加。重構系數讀取如圖7所示,每個讀時間片內都按照行地址進行遞增,一次讀出一行的數據,并把該行的N個數據分別對應的送到N個通道,依次循環往復,直到所有輸入數據全部處理完畢。

圖6 乘累加處理流程圖

圖7 系數矩陣讀取示意圖

3 仿真與實現

利用本文的設計,對某相控陣雷達的三種波形進行仿真驗證。波形1脈沖寬度為1.5μs,波形2脈沖寬度為31μs,波形3脈沖寬度為40μs。三種波形對應的帶寬也不同,所形成的波束個數也不一樣。使用乘法器資源最多的為40μs對應的波形。因此該系統設計只需要滿足40μs所需資源即可,其余消耗資源少的波形都可以通過參數重構來實現,不局限于本文仿真的三種波形,只需要按照本文設計進行計算,所需資源少于最大資源,都可以進行重構脈壓處理。

波形1的脈壓仿真結果如圖8所示,波形2的脈壓仿真結果如圖9所示,波形2的脈壓仿真結果如圖10所示。通過重構不同的濾波器系數和配置參數,在相同資源的條件下實現了三種波形的脈壓結果,驗證了本文方法的正確性。

圖8 波形1對應脈壓仿真結果

圖9 波形2對應脈壓仿真結果

圖10 波形3對應脈壓仿真結果

4 結束語

以軟件為核心的軟件化雷達是未來雷達的重要發展方向,通過靈活的軟件化重構即可實現系統的擴展、更新和升級。因此軟件化雷達存在不同波形不同波束不同數據速率的脈壓需求,如果對多個波形的脈壓進行分別設計,則大大增加了FPGA內的資源消耗,并且不利用系統重構。因此本文設計了一種基于資源復用的時域脈壓方法,根據系統波形和FPGA 資源,計算得到最大化的可用資源,只要脈壓資源小于所使用的最大資源,通過重構濾波器系數和配置參數,在不改變系統設計的條件下即可實現多波形的脈壓,能滿足對多波形多波束多數據率的重構需求。本文所提方法在一定程度上推動了軟件化雷達發展。