基于CPU+GPU的圖像處理模塊設計

錢軍琪,許夢蕓,樊 超

(航空工業西安航空計算技術研究所,陜西 西安 710065)

0 引言

隨著數字視頻時代的到來,圖形圖像處理作為數字化的重要組成部分越來越重要,特別是支持二維/三維高清圖形圖像顯示技術已經成為業界的研究熱點。本文針對數字視頻處理技術的特點提出了一種能夠支持綜合顯示界面繪制、二維/三維數字地圖加速等功能的硬件解決方案[1-2]。

1 總體結構及硬件設計

1.1 總體結構

圖像處理模塊系統如圖1所示,顯示輸出的分辨率可達1 600×1 200,視頻幀不低于30幀每秒[2]。由于要同時完成界面繪制、二維/三維數字地圖生產等復雜工作,因此對處理平臺的性能有較高的要求,經過技術分析,選用CPU+GPU的處理構架。CPU 選用飛思卡爾公司的高性能低功耗PPC構架T系列處理器,負責系統管理調度、數據存儲加載、通信管理等工作;GPU選用國內廠商景嘉微電子的JM系列圖形處理器,負責圖形圖像繪制和加速工作。

模塊的核心是中央處理器Txx和圖形處理器JMxx,CPU和GPU之間通過PCIE-PCI橋芯片連接,完成指令發送和數據傳遞。GPU完成圖形繪制后通過兩路DVI接口進行視頻輸出,一路DVI輸出綜合顯示界面,一路DVI輸出二維/三維數字地圖。數字地圖原始數據存儲在電子盤內,CPU通過內置SATA接口對電子盤進行訪問,讀取數據后送入GPU進行后續圖形處理。同時模塊預留了以太網、USB、VME等通信總線接口,用于和其他模塊及外設通信。

1.2 CPU電路設計

Txx提供2個單線程的e5500內核,基于Power Architecture?技術構建,主頻最高可達1.2 GHz,e5500內核提供256 kB的高帶寬、低延遲的共享平臺緩存,這樣在運行獨立的操作系統時,能保證很高的處理效率。CPU有1個64位的DDR3L控制器接口,有效利用了存儲器帶寬。處理器使用e5500內核和高速內部互聯技術來平衡處理器的性能與IO系統的吞吐率。配置了高性能PCI Express接口,共提供4個PCI Express2.0控制器,采用PCI-E總線實現板級高性能設備的串行點對點互連;2個SATA接口,支持1.5 Gb/s和3.0 Gb/s傳輸速率。配置了2個以太網控制器,支持10 Mbps,100 Mbps,1 000 Mbps速率通信。此外,Txx還集成了2路UART接口、中斷控制器、2個8通道的DMA控制器、GPIO等資源。

采用該處理器,利用其豐富的外圍接口,可方便實現SATA、以太網、PCIE等接口,其內部功能如圖2所示。

1.2.1 存儲器電路設計

模塊提供獨立的存儲器系統,通過CPU進行管理,包括:DDR3L SDRAM、系統FLASH、用戶FLASH、NVSRAM。

圖2 Txx處理器內部結構

模塊中CPU處理器提供獨立的DDR3L或DDR4存儲器接口,模塊設計為DDR3L接口。處理器集成的DDR3存儲控制接口支持72位數據寬度(其中8位為數據校驗位),可以直接對接DDR3-800的存儲器。DDR3 SDRAM存儲器采用Micron公司的MT41K256M16HA-125 AAT DDR3存儲器,每片存儲器容量512 MB,DDR3L SDRAM時鐘頻率最大可達800 MHz,設計降頻到600 MHz工作。存儲器地址從0開始,地址范圍為:0x0~0x7fffffff。

處理器提供容量為256 MB系統FLASH,采用1片S70GL02GS11FHI010實現,按16位工作方式,通過CPU的IFC總線進行訪問。系統FLASH用于CPU模塊的啟動,系統FLASH上駐留BIT測試程序、FLASH在板編程程序、操作系統等系統軟件。

處理器提供512 kB的NVSRAM,采用8位數據寬度訪問,地址空間連續,E2V公司的EV2A16AMNYU35,器件容量為256 k×16 bit,工作電源3.3 V。NVSRAM用于掉電保護,每片內有SRAM和EEPROM,掉電時利用芯片內部控制由SRAM中的數據寫入EEPROM中,上電時自動從EEPROM中寫入SRAM中,恢復掉電時的數據。

1.2.2 PCIE總線接口設計

處理器集成1個高速外部接口復合體(HSSI),包含8路SerDes laneA--laneH,SerDes模塊包含串行器/解串器和物理編碼子層PCS(Physical Coding Sublayer)的功能。高速接口復合體支持5種類型的接口。上電過程中,由配置字RCW的SRDS_PRTCL_S1位決定SerDes配置的接口協議類型,模塊中SRDS_PRTCL_S1位初始化為0x06,SerDes配置為寬度為×4線的PCI-E接口協議。PCI-E接口的速率由配置字RCW的SRDS_DIV_PEX位決定,支持2.5 G和5 G兩種線速。本設計中將處理器的SerDes接口配置為2路PCIE接口。提供2路標準PCIE接口,總線時鐘100 MHz。

1.2.3 調試以太網接口

處理器集成了2個獨立的以太網控制器(eTSEC)。每個接口都支持10M/100M/1 000 M以太網和IEEE 802.3網絡協議,并且配置通用8位/16位FIFO接口。eTSECs支持MII和RGMII標準外部以太網收發器接口。

模塊采用處理器的1路eTSECs接口,用于處理器的調試端口。外部連接10M/100M/1 000M以太網PHY電路,通過以太網變壓器從模塊底板連接器引出,用于模塊的調試。

1.3 GPU電路設計

JMxx是長沙景嘉微電子股份有限公司推出的一款高性能、低功耗的圖形處理芯片(GPU),具有完全自主知識產權。GPU采用全新架構設計,基于65 nm CMOS工藝實現,可廣泛應用于有高可靠性要求的圖形生成、顯示等領域。GPU能夠高效完成2D,3D的圖形加速功能[3],提供了多種外設接口,在芯片上集成了1 GB的DDR3存儲器,支持兩路多種格式的外視頻在圖形上進行開窗、縮放、旋轉以及疊加顯示。芯片的主要功能如圖3所示。

圖3 GPU總體結構

JMxx的主機接口為PCI接口,CPU不直接支持PCI接口,因此在電路設計中采用橋芯片進行總線轉換,將CPU的PCIE接口轉為PCI接口,進而完成和GPU的通信,完成指令和數據的傳送。GPU可直接將繪制的圖形通過DVI顯示接口輸出。

圖5 時鐘電路

1.4 FPGA電路設計

CPU模塊采用Xilinx公司的Spartan-3 XC3S200AN-4FTG256I實現模塊內部控制邏輯以及局部總線接口轉換。該FPGA具有200 k系統門電路、448個CLB單元、195個IO等豐富資源,兼容TTL(LVTTL)、CMOS(LVCOMS)等多種單端電氣接口,能夠滿足應用需求。

在FPGA內部主要實現以下功能:FLASH存儲器控制邏輯,中斷控制電路,復位邏輯,看門狗邏輯,離散量控制邏輯。

模塊上處理器的IFC接口是一個16位總線,設計中將處理器的局部總線接口通過FPGA轉換為外部/內部存儲器的地址和控制信號,用于訪問FLASH,FPGA內部的控制/狀態寄存器等資源。

1.5 電子盤電路設計

電子盤設計指標為存儲容量1 TB,其中1 TB為標稱值,實際可用容量不小于900 GB;支持SATA 2.0接口協議,接口速率3 Gbps,向下兼容SATA1.0接口協議;電子盤裸盤連續讀寫速率不小于80 MB/s;電子盤的連接器可插拔次數不小于1 000次。

電子盤設計采用成熟主控芯片+NAND FLASH存儲陣列的形式設計實現,主要功能如圖4所示。主要包括:SATA控制器電路;掉電保持電路,電源控制電路、毀鑰電路;時鐘電路;復位電路;SATA接口電路。

圖4 電子盤模塊功能結構

SATA控制器采用GK8802-GBIV100,是深圳華電通訊有限公司自主研發的固態硬盤控制器芯片,支持SATA3.1接口,最高速率6 Gb/s,并且向前兼容1.5 Gb/s與3 Gb/s;支持1.8 V和3.3 V的Flash IO電壓,擁有4個NAND Flash通道,每個通道8個CE,總共支持32個NAND Flash Device;支持DDR3和DDR3L DRAM,支持ECC校驗糾錯,能力在130 bits/kB,兼容主流廠商的SLC,MCL NAND Flash。支持S.M.A.R.T,支持最多32個NCQ命令。

此控制器支持國科獨有的NANDXtraTM糾錯技術,最大可提升TLC/3D TLC 3倍擦寫壽命 ;支持動靜結合的Wear Leveling技術,平衡NAND Flash擦寫次數,延長使用壽命;支持增強型垃圾回收機制,有效降低寫放大 ;支持國密SM2,SM3,SM4,內置硬件加密算法引擎,內置國際通用SHA256,AES256,內置硬件加密算法引擎。連續讀寫性能:最高550 MB/s和520 MB/s,隨機讀寫性能:最高90 k和80 k IOPS(@4K) 。

1.6 模塊時鐘電路設計

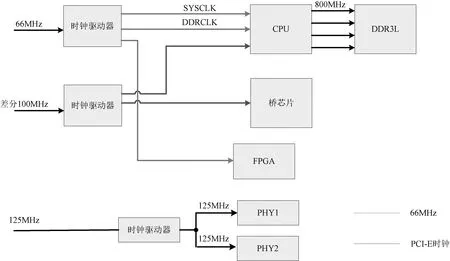

CPU模塊上配置了66 MHz,125 MHz的單端晶振和100 MHz中的差分晶振。其中,66 MHz時鐘經時鐘驅動器后一分三,分別作為CPU系統時鐘、DDR3時鐘和FPGA工作時鐘;125 MHz時鐘經時鐘驅動器后一分二,分別作為兩路以太網PHY的參考時鐘;100 MHz時鐘經時鐘驅動器后一分二,分別作為CPU的PCIE時鐘和橋芯片的PCIE時鐘。時鐘配置情況如圖5所示。

1.7 復位電路設計

圖像處理模塊復位關系如圖6所示。上電復位:電源5 V電壓低于4.65 V時,系統處于復位狀態,電壓大于4.65 V后,產生大于200 ms復位;模塊上電時,為保證FPGA配置過程中其他功能塊處于復位狀態,設計時把FPGA加載完成信號DONE連接到SM706T的手動復位輸入端。當FPGA加載完成后,SM706T再產生200 ms復位信號,模塊啟動工作。在正常工作中,如果SM706T檢測到+5 V電壓低于4.65 V時,SM706T產生復位信號,模塊處于復位狀態;當電壓恢復至4.65 V以上時,SM706T產生撤銷復位信號,模塊重新啟動[4]。軟件復位,可以通過軟件寫FPGA寄存器方式復位CPU,復位時間大于2 ms。

2 結語

基于CPU+GPU構架的圖像處理模塊具有圖形處理能力強、工作穩定性高、綜合功耗低等特點,非常適合需要圖形圖像處理工作的嵌入式應用場景。該模塊在提供了多用途的圖形圖像處理能力的基礎上,兼顧了性能、體積和功耗的平衡,同時具備較強的內部通信和對外交互聯通能力。

圖6 復位電路關系