56 Gbps高速信號傳輸系統仿真驗證設計*

李寶峰,黎鐵軍,劉勇輝,馬柯帆,羅煜峰,姚信安

(國防科技大學計算機學院,湖南 長沙 410073)

1 引言

隨著高性能計算機中的信號傳輸速率超過25 Gbps,傳統NRZ(Non-Return-to-Zero)信號對傳輸鏈路設計的限制更加嚴苛[1],通過提高波特率來實現高帶寬傳輸的難度越來越大[2 - 4]。而PAM4(4 Pulse Amplitude Modulation)信號采用4個電平表征符號,每個符號編碼2比特信息,相同波特率下的帶寬是NRZ的1倍,在25 Gbps以上高速信號傳輸系統中廣泛應用。但是,PAM4信號的信噪比相對NRZ劣化了約9.5 dB[5],相同電平幅度下的眼高只有NRZ的1/3,更易受到噪聲影響,導致誤碼率大幅增加[6 - 9]。

新一代高性能計算機的高速信號傳輸系統采用56 Gbps PAM4信號實現,傳輸通道跨越多塊PCB(Printed Circuit Borad)板和多級連接器,走線長度長、阻抗不連續點多,信號完整性設計面臨極大挑戰。為提高設計成功率,本文提出了面向全通道的56 Gbps高速信號傳輸系統仿真驗證方案,通過仿真與測試相結合的方法,建立了更接近實際情況的跨越多PCB和多連接器的復雜傳輸通道模型,并對其進行了全通道的協同仿真實驗。通過多次仿真實驗與設計優化迭代驗證了該設計較好地預測了56 Gbps高速信號傳輸系統的性能瓶頸,有力保障了56 Gbps PAM4高速信號的穩定傳輸。

2 仿真驗證設計

2.1 仿真驗證方案

56 Gbps高速信號傳輸系統的傳輸通道由1塊背板BPM、3塊子板(上層互連接口板ZNIB、下層互連接口板ZNIT和互連通信板NRM)和3級連接器組成,PCB走線層采用松下M7N(MEGTRON7系列低介電常數DK(Dielectric Constant)材料)板材,銅箔類型為極低輪廓HVLP(High-frequency Very Low Profile)銅箔。為提高仿真精準度,本文提出了面向全通道的仿真驗證方案。第1步,通過仿真與測試擬合方法確定板材仿真參數;第2步,通過測試確定連接器仿真參數;第3步,提取傳輸通道上各傳輸鏈路的PCB設計模型,建立全通道HFSS(High Frequency Structure Simulator)仿真模型;第4步,對仿真模型進行全通道的TDR(Time Domain Reflectometry)仿真、S參數仿真和有源仿真,根據仿真結果驗證56 Gbps高速信號傳輸系統設計的可靠性。

仿真驗證的硬件環境:3臺Windows 7服務器,每臺服務器配備2顆Intel Xeon E5530 12核CPU,內存160 GB。軟件環境:ANSYS SIwave 2018.2.0、HFSS 2018.2.0、ANSYS HPC軟件套件和KEYSIGHT ADS2017軟件。

2.2 確定板材參數

高速信號仿真中,PCB板材的介電常數DK、損耗角正切DF(Dissipation Factor)值及銅箔粗糙度是主要輸入參數[10]。通過對真實測試板進行仿真與測試結果的擬合,不斷調整優化PCB板材的DK、DF值及銅箔表面粗糙度,以得到與測試相吻合的仿真結果。

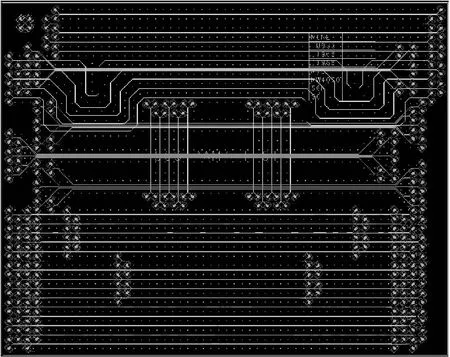

制作的56 Gbps-PAM4測試板各通道的出線情況如圖1所示;測試板所采用的板材為M7N板材,銅箔類型為HVLP銅箔,各通道中的過孔均能滿足最小的過孔殘樁要求。

Figure 1 56 Gbps-PAM4 test board圖1 56 Gbps-PAM4測試板

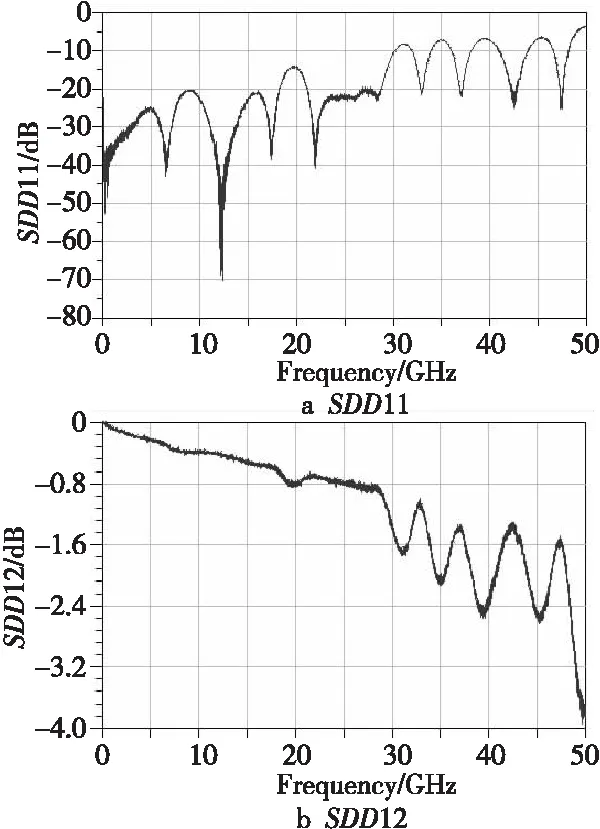

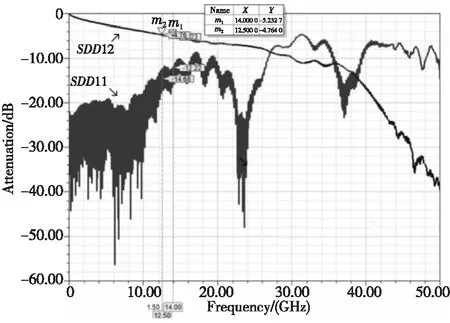

采用矢量網絡分析儀VNA(Vector Network Analyzer)測量得到該通道的S參數結果,如圖2所示。

Figure 2 S parameter of VNA measured channel圖2 VNA實測鏈路S參數

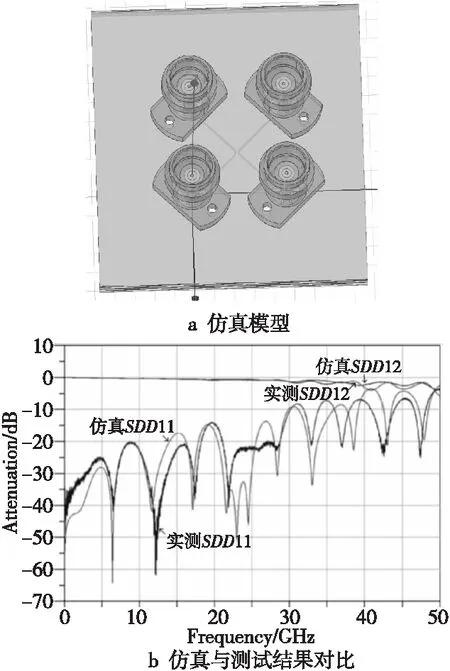

在SIwave軟件中提取相應的模型并導入HFSS仿真軟件進行仿真參數的提取,仿真模型如圖3a所示。該模型中,為達到仿真與測試環境的一致性,在該模型的4個端口處分別添加了4個SMA(Sub-Miniature-A)模型。仿真與測試的對比結果如圖3b所示。

Figure 3 Simulation model and comparison of simulation & test results圖3 仿真模型和仿真與測試結果對比

圖3所示為仿真與測試的插入損耗和回波損耗結果對比圖。由圖3可知,兩者的插入損耗曲線擬合得較好,30 GHz之前兩曲線完全重合;回波損耗曲線在第2個諧振點可以很好地對應上,且隨頻率變化的趨勢相同。以上仿真和測試的對比結果較好地說明了當銅箔粗糙度為0.3 um時,采用表1所示的DK、DF值,可較好實現仿真與測試結果的一致性,仿真可信度較高。

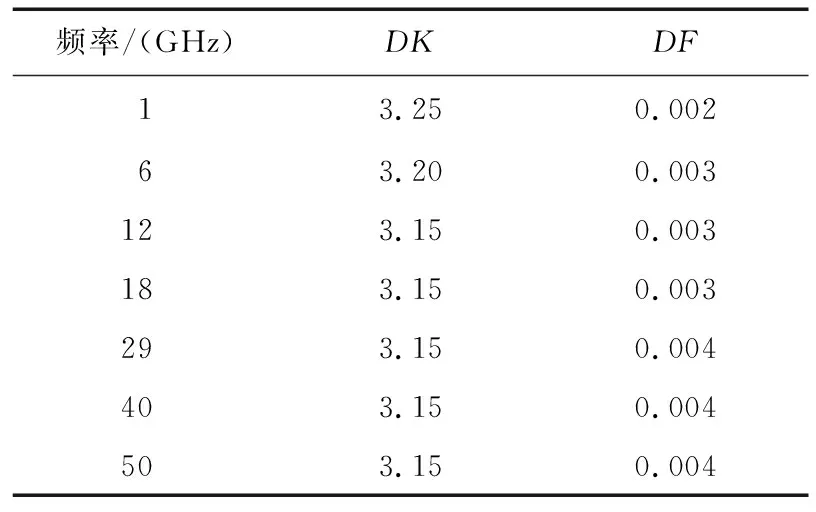

Table 1 DK/DF values after simulation and test fitting 表1 仿真與測試擬合后的DK/DF值

2.3 確定連接器參數

為提高信道中的數據傳輸速率,減少由于損耗引起的信號完整性問題,高速連接器在設計時會綜合考慮引腳排列、板卡間距、介質材料和信號完整性等因素,提供低損耗、低串擾和阻抗匹配性能強的高速連接器[11]。

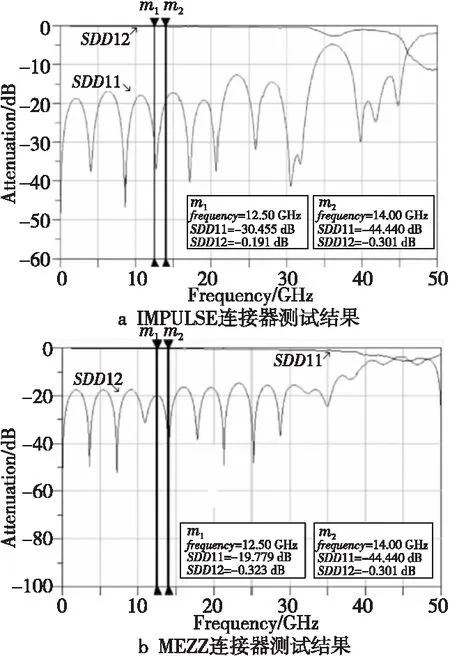

56 Gbps高速信號傳輸系統中的最長通道采用了3級連接器傳輸鏈路,共使用了IMPULSE連接器和MEZZ連接器2種類型的高速連接器。分別對2種連接器采用VNA進行傳輸參數的測試,得到的結果如圖4所示。

Figure 4 Results of connector test 圖4 連接器測試結果圖

2.4 建立全通道HFSS仿真模型

2.4.1 傳輸通道拓撲結構

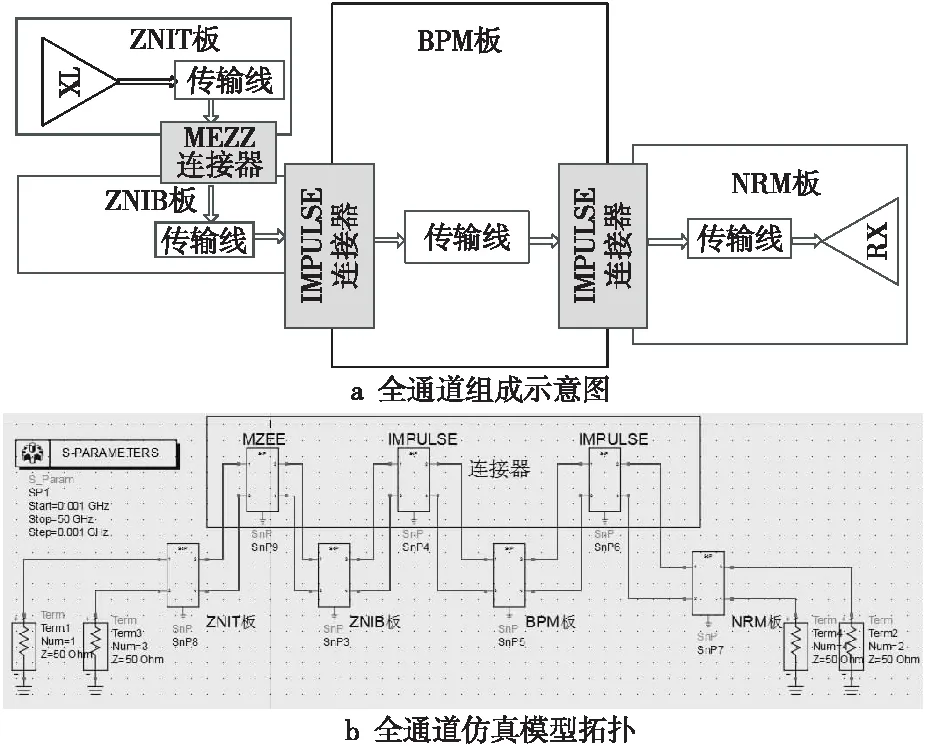

為保證仿真驗證結果的代表性和覆蓋性,本文選取了56 Gbps高速信號傳輸系統中長度最長、構成最復雜的通道作為仿真對象。如圖5a所示,該通道跨越3級連接器和4塊PCB板,分別為ZNIT板、ZNIB板、BPM板以及NRM板、2級IMPULSE連接器和1級MEZZ連接器。由于信號經過的PCB板較多,傳輸損耗加大;經過的連接器較多,鏈路的阻抗一致性變差,從而使得56 Gbps PAM4高速信號的傳輸面臨巨大挑戰。

Figure 5 Composition of full channels and simulation model topology 圖5 全通道組成與仿真模型拓撲

為預先驗證設計的有效性,本文采用HFSS仿真軟件分別對各PCB傳輸鏈路進行提取,進而在ADS(Advanced Design System)仿真軟件中建立了全通道HFSS仿真模型,如圖5b所示。

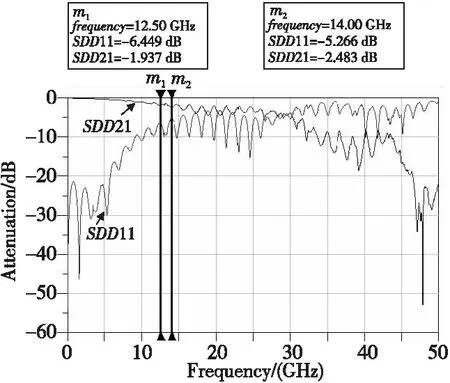

2.4.2 BPM傳輸鏈路模型

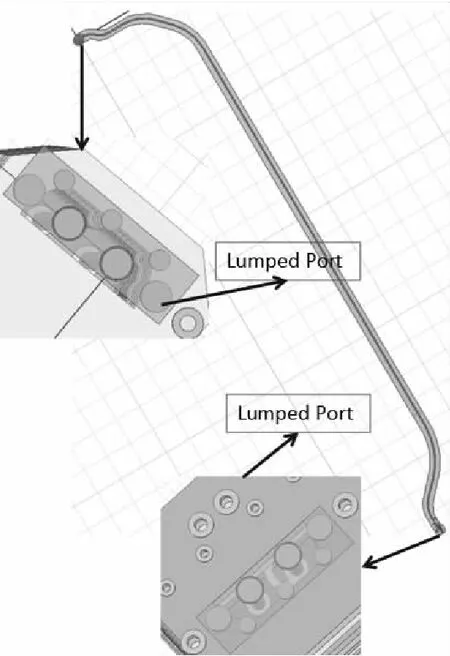

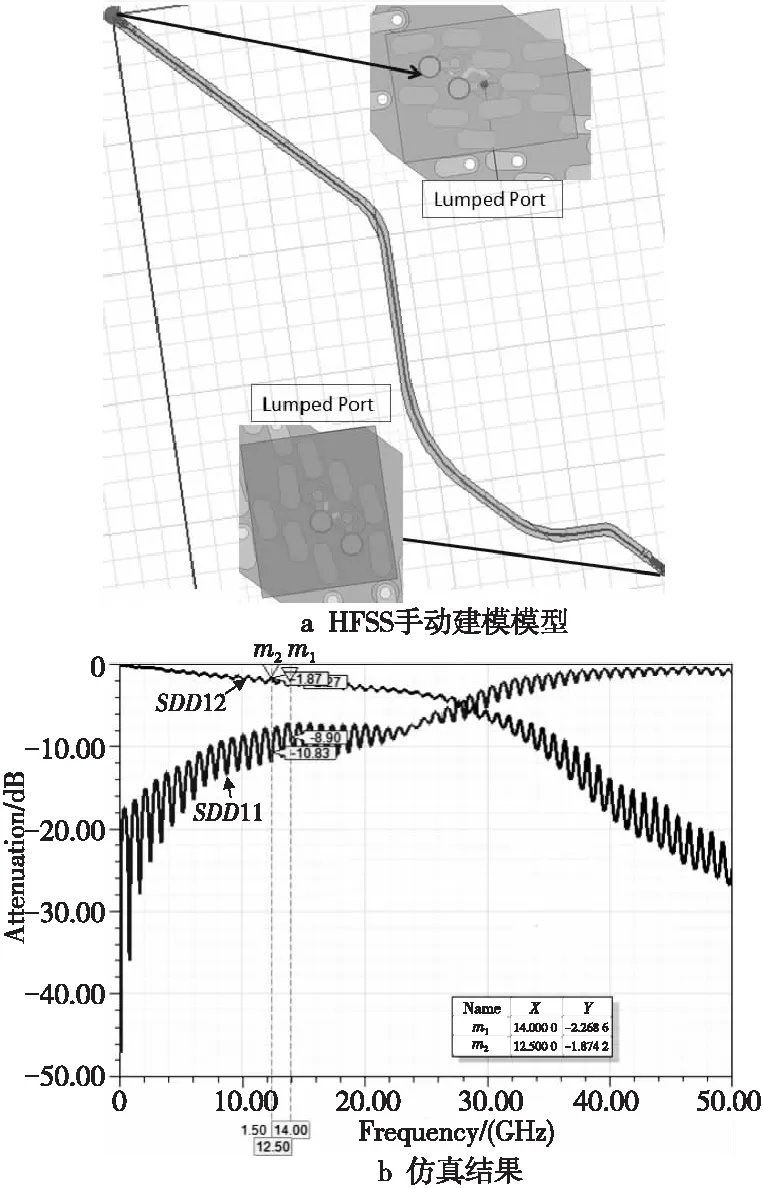

對BPM板創建的仿真模型如圖6所示。BPM板共計28層,所選擇的仿真網絡位于S07層,線長為329.419 4 mm(12.969 inch),線寬、線距為9 mil/12 mil/9 mil,信號的目標阻抗為92 (1±10%)Ω,過孔的成品孔徑為0.31 mm(12.20 mil);板厚為5.984 mm(235.59 mil),最大板厚孔徑比設計為19.3∶1。該信號一端為NRM板的連接器,一端為ZNIB板的連接器,其中NRM板的連接器位于Bottom層,背鉆需從Top層鉆至GND06層;ZNI板的連接器位于Top層,背鉆需從Bottom層鉆至GND08層,該端所經歷的過孔通道較長。走線2端均添加Lumped Port仿真端口,仿真的中心頻點為14 GHz,掃頻在10 MHz~50 GHz,步進(Step)為0.001 GHz。所創建的模型中過孔的背鉆均能夠鉆至與走線層相鄰的信號參考層,因而過孔殘樁對信號的影響可以忽略[12 - 15]。仿真結果如圖7所示,圖7中分別給出了該模型的回波損耗和插入損耗結果,并分別列出了信號在12.5 GHz頻點和14 GHz頻點時的傳輸損耗。

Figure 6 Manual HFSS model of BPM board圖6 BPM板HFSS手動建模模型

Figure 7 Simulation results of BPM board圖7 BPM板仿真結果

由仿真結果可知:在12.5 GHz頻點處,信號的插入損耗值為-4.764 dB@12.5 GHz,回波損耗值為-14.68 dB@12.5 GHz;在14 GHz頻點處,信號的插入損耗值為-5.232 7 dB@14 GHz,回波損耗值為-12.22 dB@14 GHz。信號的傳輸損耗表現較好。

2.4.3 ZNIT傳輸鏈路模型

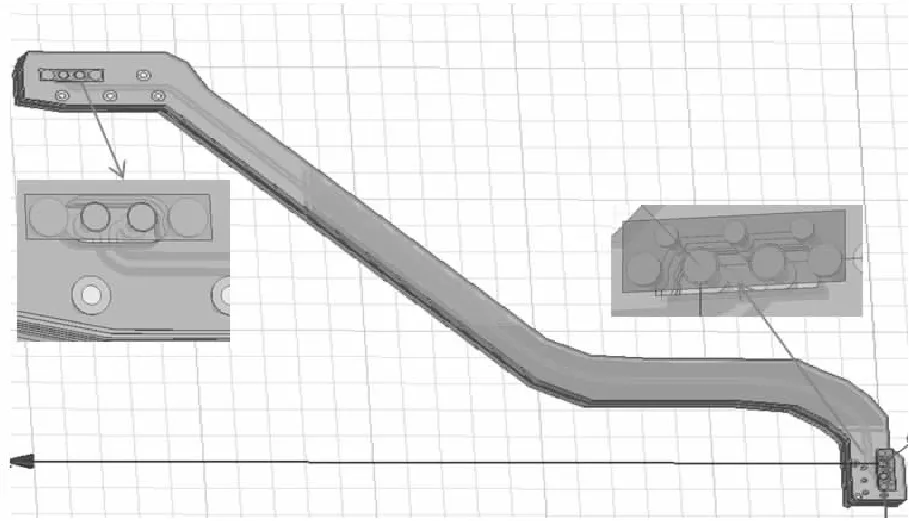

對ZNIT板創建的仿真模型如圖8所示。模型中過孔的背鉆均能滿足最小的殘樁要求,因而過孔殘樁對信號的影響可以忽略。仿真結果如圖9所示。

Figure 8 Manual HFSS model of ZNIT board圖8 ZNIT板HFSS手動建模模型

Figure 9 Simulation results of ZNIT board圖9 ZNIT板仿真結果

由仿真結果可知:在12.5 GHz頻點處,信號的插入損耗值為-1.937 dB@12.5 GHz,回波損耗值為-6.449 dB@12.5 GHz;在14 GHz頻點處,信號的插入損耗值為-2.483 dB@14 GHz,回波損耗值為-5.266 dB@14 GHz。信號的傳輸損耗表現較好。

2.4.4 ZNIB傳輸鏈路模型

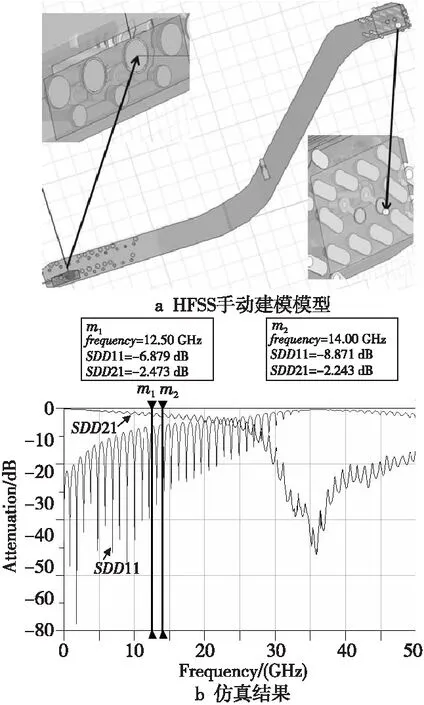

對ZNIB板創建的仿真模型如圖10a所示,仿真的插入損耗SDD21和回波損耗SDD11結果如圖10b所示。

Figure 10 Manual HFSS model and simulation results of ZNIB board圖10 ZNIB板HFSS手動建模模型及仿真結果

由仿真結果可知:在12.5 GHz頻點處,信號的插入損耗值為-2.473 dB@12.5 GHz,回波損耗值為-6.879 dB@12.5 GHz;在14 GHz頻點處,信號的插入損耗值為-2.243 dB@14 GHz,回波損耗值為-8.871 dB@14 GHz。信號的傳輸損耗表現較好。

2.4.5 NRM傳輸鏈路模型

對NRM板創建的仿真模型如圖11a所示,仿真的插入損耗和回波損耗結果如圖11b所示。

Figure 11 Manual HFSS model and simulation results of NRM board圖11 NRM板HFSS手動建模模型及仿真結果

由仿真結果可知:在12.5 GHz頻點處,信號的插入損耗值為-1.87 dB@12.5 GHz,回波損耗值為-10.83 dB@12.5 GHz;在14 GHz頻點處,信號的插入損耗值為-2.26 dB@14 GHz,回波損耗值為-8.90 dB@14 GHz。信號的傳輸損耗表現較好。

3 仿真驗證結果

本節對建立的全通道仿真模型進行TDR仿真、S參數仿真和有源仿真實驗。

3.1 TDR仿真結果及分析

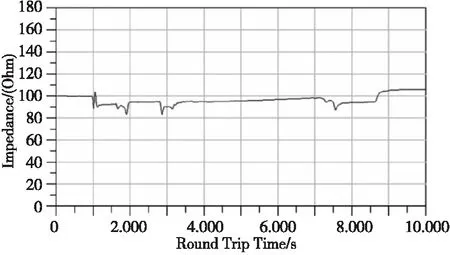

根據圖5b所搭建的全通道仿真模型拓撲圖,進行全通道TDR仿真分析,通過TDR仿真可以查看到全通道中阻抗突變的點,從而有針對性地進行優化。得到的仿真結果如圖12所示。

Figure 12 TDR simulation results圖12 TDR仿真結果

從TDR仿真結果中可發現,全通道的阻抗基本滿足目標阻抗92±10%的要求,通道中個別點處的阻抗值較低,對應為連接器與過孔相接處。由于此處突變較短,因此對全通道整體影響不大。

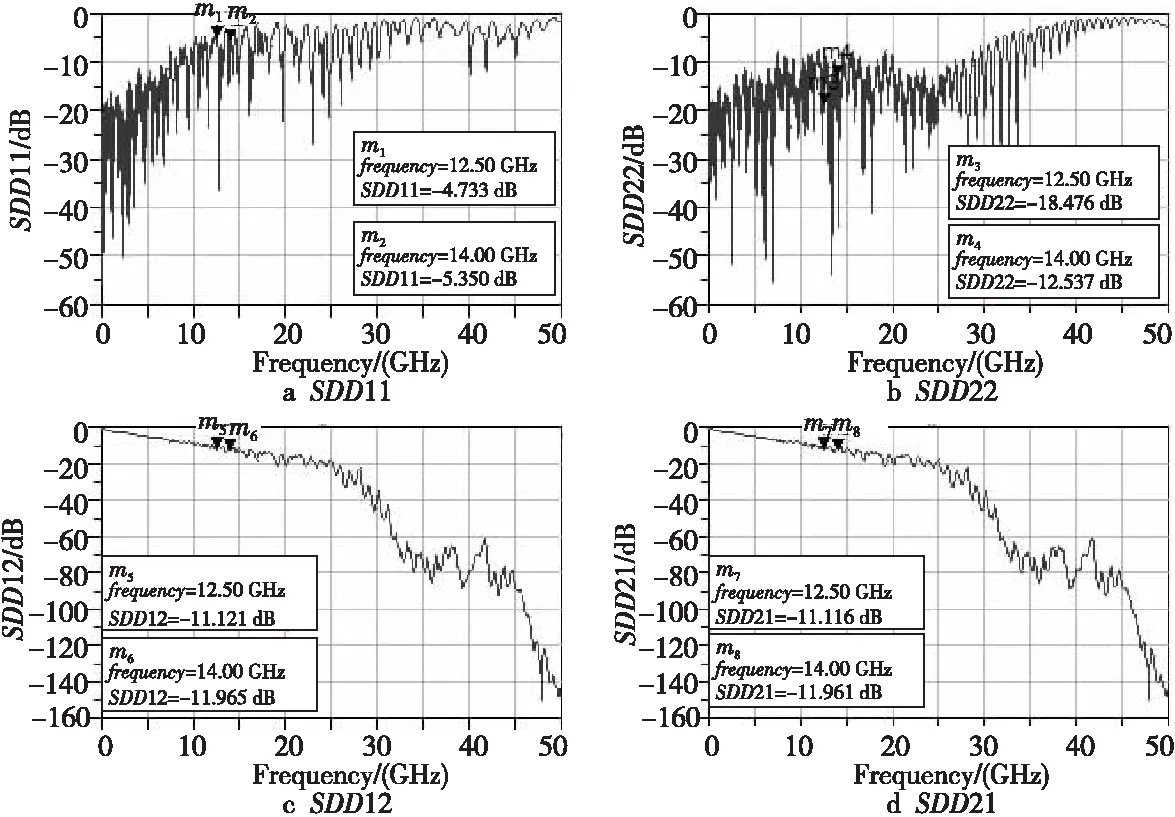

3.2 S參數仿真結果及分析

根據圖5b所搭建的拓撲圖,進行全通道S參數仿真,得到的全通道的S參數結果如圖13所示。

Figure 13 Simulation results of S parameter of full channel 圖13 全通道S參數仿真圖

由全通道的S參數仿真結果可以看出,插入損耗在12.5 GHz頻點處為-11.121 dB@12.5 GHz,在14 GHz頻點處的插入損耗值為-11.965 dB@14 GHz;回波損耗在12.5 GHz頻點處為-18.476 dB@12.5 GHz,在14 GHz頻點處的回波損耗值為-12.537 dB@14 GHz。全通道的傳輸損耗較低。

3.3 有源仿真結果及分析

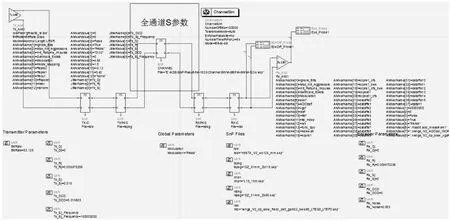

在得到全通道S參數的基礎上進行有源仿真,搭建的仿真拓撲圖如圖14所示。圖14中全通道S參數導入的文件為利用圖5b所示拓撲仿真得到的全通道S參數結果。

Figure 14 Topology of active simulation圖14 有源仿真拓撲圖

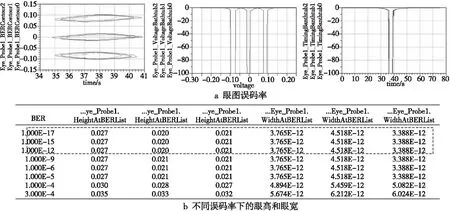

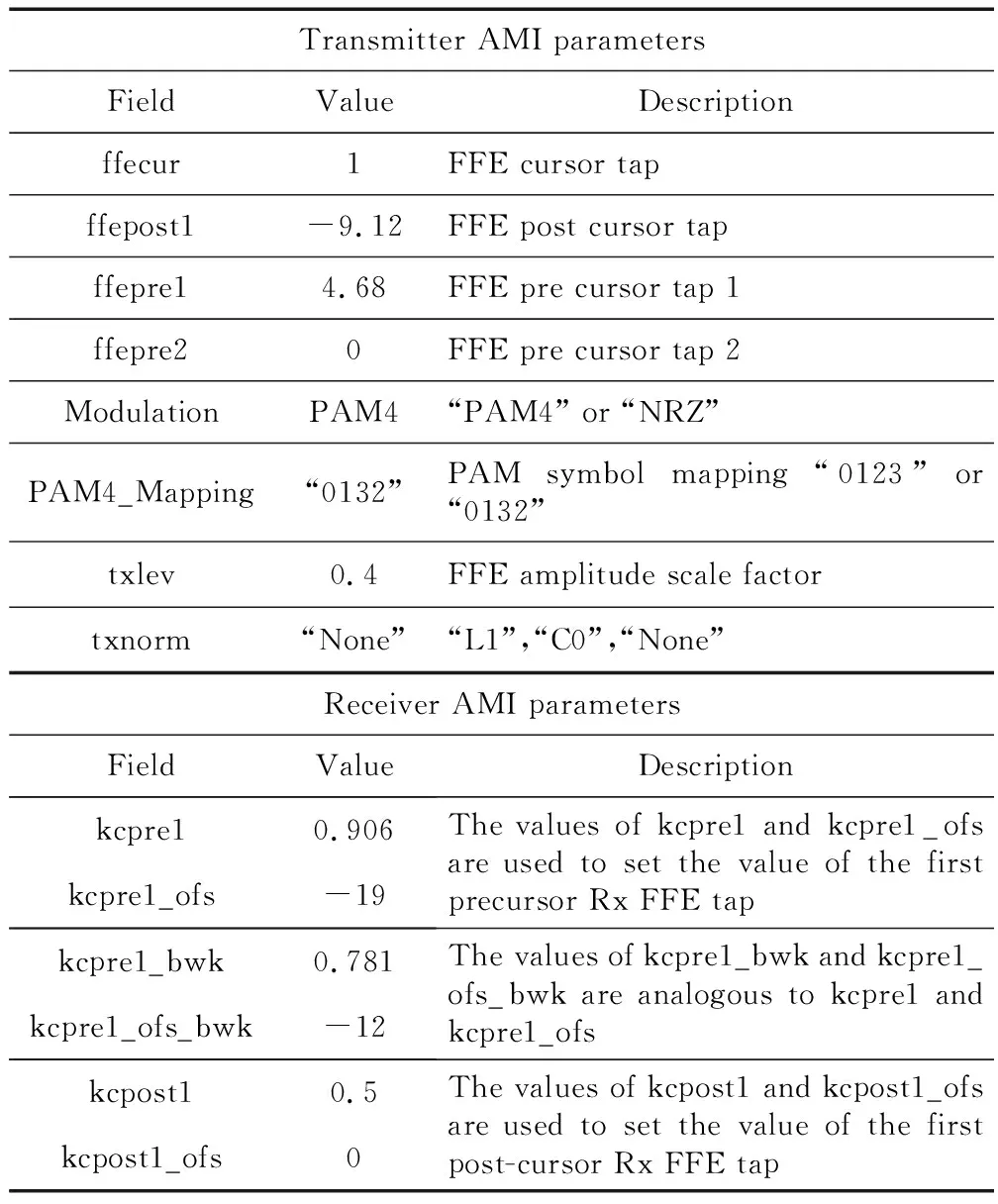

圖14中,接收端TX和發送端RX的芯片模型采用廠家提供的IBIS-AMI模型代替,該模型可設置不同的信號調制方式,作為與56 Gbps-PAM4信號的對比,此處同時仿真了25 Gbps-NRZ信號。鏈路跨板且有多級連接器長,需要對TX和RX端進行均衡參數的設置才能夠在接收端得到眼圖,實現有效的傳輸。基于全通道的傳輸損耗,發送端和接收端AMI參數設置如圖15所示。

仿真的速率分別設置為25 Gbps和56 Gbps,圖14中該模型的第2部分為芯片的封裝參數,此處采用芯片廠家提供的封裝S參數文件;該模型的第3部分為CHANNEL,該部分為所需要仿真的全通道,此處導入圖5b中仿真得到的全通道S參數文件;該模型的第4部分為眼圖探針,作為仿真結果的查看窗口,此處分別在接收端芯片前添加一個差分探針,查看未經接收端芯片處理的眼圖效果及在接收端芯片后添加一個探針,查看對比經過接收端芯片后的眼圖效果。具體的眼圖仿真結果如圖15所示。

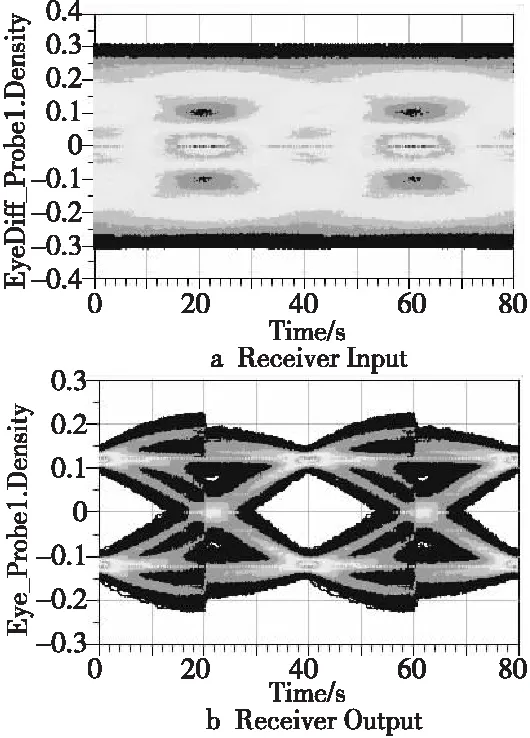

Figure 15 25 Gbps-NRI simulation results of eye pattern圖15 25 Gbps-NRI 眼圖仿真結果

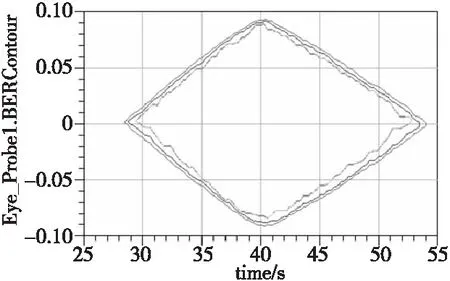

圖15為25 Gbps-NRZ的眼圖仿真結果。由圖15可知,在Receiver Input端未經過接收端芯片均衡時,眼睛完全關閉;在Receiver Output經過接收端芯片均衡后,眼睛的張開情況得到較大的改善。圖16a給出了該眼圖的具體眼高和眼寬值。由圖16a可知,當誤碼率為1.000E-6時,能夠得到張開的眼睛,此時的眼高為0.172,眼寬為2.360E-11;但當誤碼率超過1.000E-6時,眼圖成閉合趨勢,得不到信號質量良好的眼圖。

a 眼圖誤碼率

b 不同誤碼率下的眼高和眼寬Figure 16 25 Gbps-NRZ eye map and eye height & eye width of eye pattern with different error rates圖16 25 Gbps-NRZ眼圖誤碼率及在不同誤碼率下的眼高和眼寬

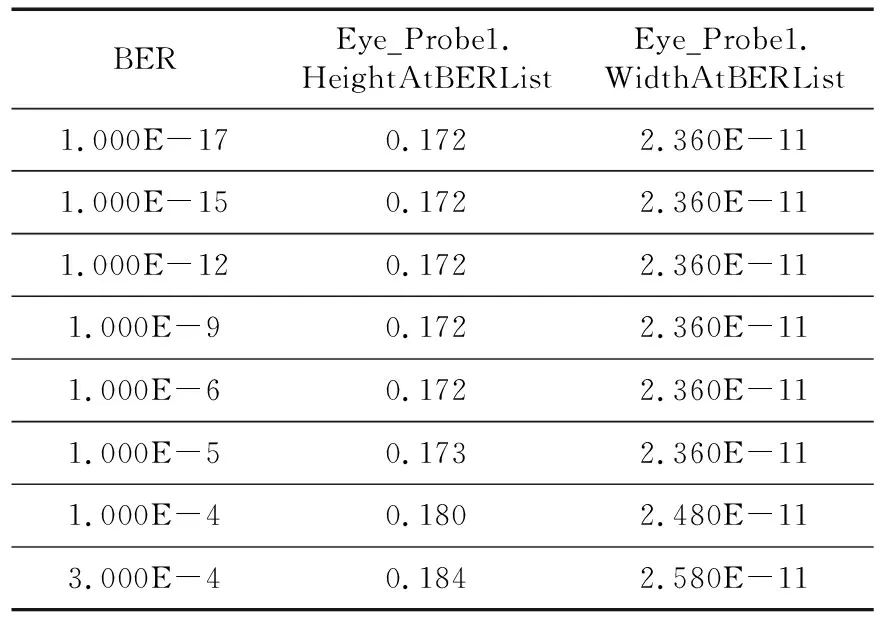

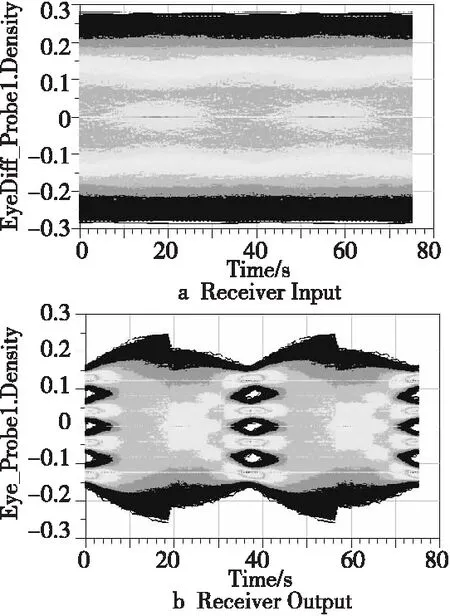

圖17為56 Gbps-PAM4的眼圖仿真結果,在Receiver Input端未經過接收端芯片均衡時,眼睛完全關閉;在Receiver Output經過接收端芯片均衡后,眼睛的張開情況得到較大的改善。圖18b給出了具體的眼高眼寬值。

Figure 17 56 Gbps-PAM4 simulation results of eye pattern圖17 56 Gbps-PAM4眼圖仿真結果

Figure 18 56 Gbps-PAM4 eye map and eye height & eye width of eye pattern with different error rates圖18 56 Gbps-PAM4眼圖誤碼率及在不同誤碼率下的眼高和眼寬

Table 2 Transmitter and receiver AMI parameters表2 發送端和接收端AMI參數

由圖18b可知,當誤碼率為1.000E-6時,能夠得到張開的眼睛,但誤碼率超過 1.000E-6時,眼睛關閉,得不到眼圖。

對比圖16a和圖18a的眼圖仿真結果可以發現,在當前跨板多級連接器長鏈路傳輸系統中,通過對發送端和接收端的均衡設置,系統能夠有效地實現25 Gbps-NRZ和56 Gbps-PAM4信號的傳輸;同時,在相同的鏈路環境下,系統傳輸NRZ信號和PAM4信號的誤碼率相同,均為1.000E-6,但系統的傳輸速率卻從25 Gbps上升到了56 Gbps,傳輸速率大為提高。

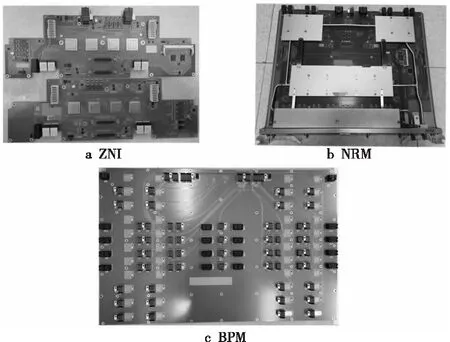

3.4 結論與工程實現

從全通道的TDR仿真可知,全通道的真實阻抗基本滿足設計的目標阻抗要求,減少了信道傳輸過程中因阻抗匹配不一致而造成的反射問題;S參數仿真結果表明,全通道的傳輸損耗較低,14 GHz處的插入損耗低于-12 dB;有源仿真中當加入均衡時能夠有效地得到張開的25 Gbps-NRZ和56 Gbps-PAM4眼圖,此時全通道的傳輸誤碼率為1.000E-6。全通道的仿真結果表明,在當前仿真驗證設計中能夠有效地實現56 Gbps PAM4信號的傳輸。本文所述成果已經應用于本單位高性能計算機系統的工程構建,實際應用結果表明,系統能很好地保證56 Gbps PAM4高速信號的穩定傳輸,系統所需印制板如圖19所示。

Figure 19 System engineering implementation圖19 系統工程實現

4 結束語

本文針對56 Gbps高速信號傳輸系統進行仿真分析研究,基于信號完整性,通過對仿真板材參數的精準確定、連接器參數的確定及各傳輸子模塊仿真模型的建立,基于仿真結果實現了56 Gbps-PAM4信號的穩定傳輸。通過仿真結果可知,采用仿真與測試的擬合方法可較好地確定板材仿真參數,為進行高速信號仿真建立基礎;連接器和過孔為全通道中阻抗不連續的點,但在整個通道中由于突變較短,對通道整體性能影響較小;基于真實PCB板提取的3D仿真模型較準確地說明了各子模塊的傳輸損耗,并把每個模塊的S參數代入全通道拓撲中,通過調整均衡值仿真得到全通道的S參數與眼圖滿足設計要求。本文實現的傳輸系統仿真設計不僅為56 Gbps高速信號傳輸系統提供了指導,還為未來更高速率的設計打下了基礎。PAM4信號傳輸中較為關注的傳輸介質的線性度及對應的群延時影響方面的研究有待進一步深入。