L波段快速鎖定頻率合成器的設計與實現

劉長明,江飛

(同方電子科技有限公司,江西九江, 332000)

0 引言

跳頻通信由于其具有抗干擾、抗截獲的能力,在當前軍事抗干擾通信系統中被廣泛應用。跳頻通信系統的一項重要參數是頻率的跳變速度,它在很大程度上決定了系統抗跟蹤式干擾的能力。因此,快速鎖定頻率合成器的設計就成為跳頻通信的關鍵技術之一。本文采用自適應精確預置技術實現了一個L波段快速鎖定頻率合成器的工程設計。

1 自適應精確預置技術原理

頻率合成器鎖相環路在開始工作時,參考頻率fR與壓控振蕩頻率fV可能不相等,處于失鎖狀態。因而需要靠鎖相環鑒相輸出的相位誤差電壓控制系統進行調整,最后鎖定在狀態fR=fV,這一過程稱為鎖相環路的捕獲過程。環路捕獲過程包括頻率捕獲過程和相位捕獲過程。

相位捕獲與頻率捕獲只是用于區別環路運動狀態的兩種不同過程,表征環路捕獲過程中的不同階段,實際上并不能進行嚴格劃分。當環路中的相差做較大范圍變動時,環路處于頻率捕獲階段;當環路中的相差不再超過2π而進入鎖定時的捕獲過程被稱為相位捕獲。

環路依靠自身的控制作用而捕獲的方式稱為自捕獲,借助于輔助電路實現捕獲的方式稱為輔助捕獲。自捕獲的缺點:捕獲速度慢、捕獲范圍小、可靠性差,通過改變環路參數的方法改善捕獲性能時會嚴重影響環路的跟蹤性能,實現時一般采用輔助捕獲方法改善環路的捕獲性能。

在實際的跳頻系統應用中,既要提高環路自身的頻率捕獲性能,同時又保證鎖相環路的相噪性能,單靠鎖相環本身來說是很難實現的,必須采用一些頻率輔助捕獲技術。自適應精確預置技術就是一種提高環路捕獲性能的方法,它是在粗調預置技術基礎上進行完善的,其基本原理如下:

粗調預置技術的采用基本上避免了鎖相環路的失鎖和假鎖現象,粗調預置技術的合理采用,可以使得鎖相環路迅速進入快捕帶,從而大大加大環路的鎖定速度,減小壓控振蕩器的增益,減小壓控振蕩器輸出相位的抖動噪聲。但是在長期工作的跳頻系統中,要求鎖相環路始終能夠滿足一定的鎖定速度要求,而粗調預置技術在某一頻點始終都用同樣的值去預置壓控振蕩器。由此可見,粗調預置技術缺乏靈活性,不能保證鎖相環路始終都能得到比較準確地預置。

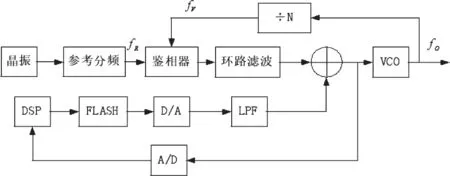

因此,對此粗調預置技術進行了改進。在粗調預置技術的基礎上提出了自適應精確預置技術。在跳頻系統的實際工作中,由于環境溫度等因素的變化,VCO的壓控特性會有所變化,原定的預置值可能會與實際所需值出現誤差。為了及時修改頻率碼與預置電壓的對應關系,可以用FLASH作為存儲器(如圖1所示)。當環路在某一頻率鎖定時,系統把鑒相器輸出的電壓值采樣進入數字信號處理器(DSP),用該電壓修正原來的預置值,修改后的值作為下一次跳入該頻率時的預置值。由于環境變化速度相對于跳頻周期慢得多,更新的預置值能準確、實時地跟蹤任何環境條件的變化。這樣,通過不斷的精確預置,頻率跳變時,VCO的輸出頻率與要實現的頻率只有很小的相位偏差,鎖相環基本上工作在相位跟蹤狀態,大大減小了頻率轉換時間,從而很好地滿足快速跳頻的要求。

圖1 采用自適應精確預置技術的頻率合成器原理框圖

2 自適應精確預置技術的工程實現

■2.1 快速鎖定頻率合成器方案設計

以一個L波段快速鎖定頻率合成器為例,要求輸出頻率為1200~1600MHz,換頻時間不大于100μs。

頻率合成方案充分考慮數字直接頻率合成(DDS)技術和鎖相環頻率合成技術優缺點互為補充的特點,采用DDS+PLL架構。由DDS提供快速跳頻的小步進間隔,鎖相環(PLL)工作在大步進間隔,這樣可以提高鑒相頻率,增大環路帶寬,并抑制雜散分量。DDS相當于一個小數分頻器。接收VCO輸出的頻率,通過改變頻率控制字K,使其輸出固定的頻率。此方案的設計中體現出以下顯著優點:

利用了DDS頻率轉換速度快,頻率分辨率高的優點,并克服了其輸出頻率低和輸出信號頻率范圍小的缺點。

利用了鎖相環頻率合成技術良好的跟蹤特性和噪聲特性。

本系統方案在相當程度上解決了鎖相環中提高鑒相頻率和降低頻率間隔的矛盾。既實現了頻率的快速跳變和精細步進,又實現了高的頻率輸出。

系統結構簡單,容易實現,實現成本也較低。

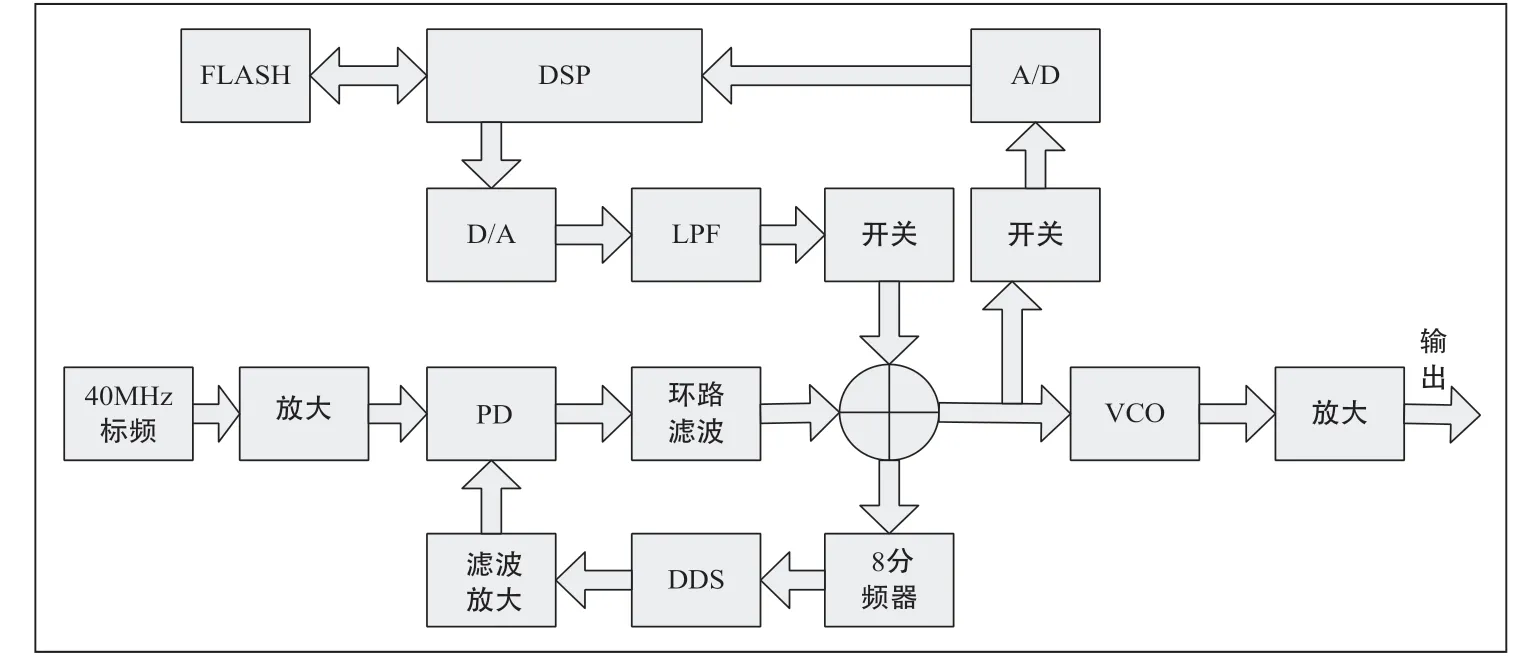

為了滿足電臺高速跳頻的要求,在方案中同步采用了自適應精確預置技術,在環路輔助捕獲電路上設計了對VCO的壓控電壓進行采樣的A/D以及預置壓控電壓所需的D/A,其原理框圖如圖2所示。

圖2 快鎖鎖定合成器原理框圖

采用自適應精確預置技術的頻率合成器快速鎖定設計思路如下:

首先,開機先進行全頻段掃描,把全頻段鎖相環鎖定后的VCO調諧電壓采樣并存儲起來,這樣在下次換頻時,可直接預置其相應壓控電壓,可省去鎖相環頻率捕獲時間和A/D采樣時間而讓鎖相環直接工作,完全避免了鎖相環捕獲時間過長的問題。這樣,頻率合成器實際需要的頻率轉換時間就只有D/A建立時間,鎖相環捕獲時間和送數時間。一般來說,前2種時間都很短,都在微秒量級,送數的時間相對要長一些一般在幾十微秒。因此從原理上講,可以實現鎖相環的捷變頻。

其次,為了保證頻率合成器正式工作時每次頻率轉換,鎖相環均能一次鎖定。除了在開機及某些特定的時間利用鎖相環工作對預置電壓數據進行修正外,在每次鎖相環鎖定后仍同步對VCO調諧電壓采樣,并將此次采樣得到的數據刷新原來的預置電壓數據。這樣,在跳頻過程中VCO預置電壓得到了實時修正,從而使輔助頻率捕獲電路自動跟蹤了VCO特性的變化,對VCO的一致性及外界環境的要求降低。

■2.2 電路仿真

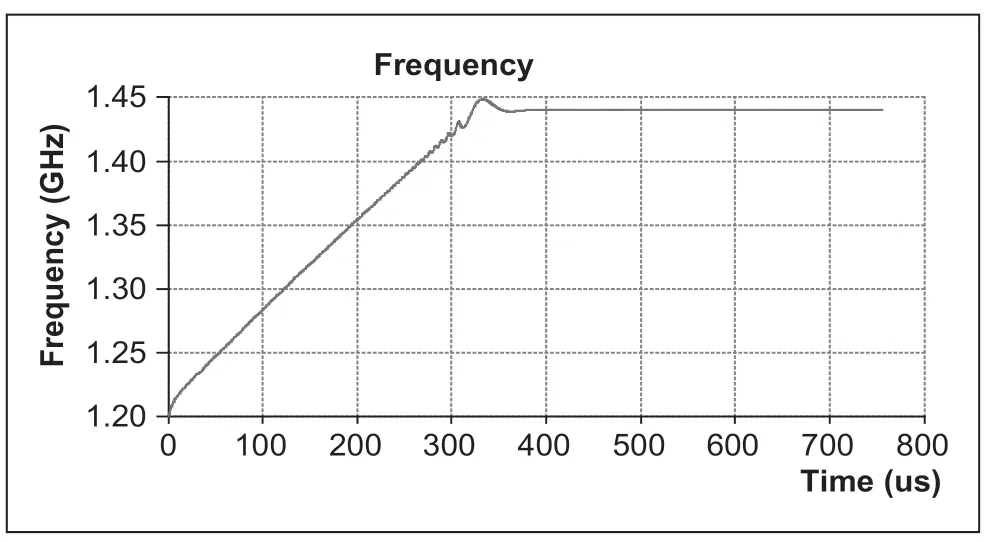

首先對鎖相環路進行仿真以優化頻率合成器的輸出相噪及雜散抑制,同時可以對環路自身鎖定時間有一個大概的了解,并可與加了輔助捕獲電路以后的環路鎖定時間進行對比。筆者用AD公司的ADIsimPLL進行了仿真,仿真參數設定鑒相頻率8MHz,環路帶寬20kHz,仿真結果見圖3。

圖3 環路特性仿真圖

由圖3可見如果不采用預置技術單靠環路自身鎖定,由于要保證低相噪,所以要求鑒相頻率不能太高,環路帶寬比較窄,從仿真結果來看單環鎖定時間在350μs以上,并且考慮到實際工作時各種器件及送數等相關方面的延時,實際鎖定時間只會比理論估算時間要長。

■2.3 軟件程序流程

軟件程序流程需要分為對壓控電壓的采集過程和采集處理后對壓控電壓進行預置的正常工作過程。

2.3.1 采集數據流程

設置起始頻率1200MHz,頻率步徑為0.5MHz(即從1200MHz開始,每隔0.5MHz頻率采集一次),次數為801次。然后將開關切換到采集狀態,通過DSP進行預定頻率點的頻率控制字計算,將計算結果通過串口按時序將頻率控制字送入PLL電路的相應芯片,等待PLL電路的鎖定指示,這樣就完成了一次頻率送數工作。當DSP芯片收到鎖定指示后便開始采集壓控電壓,該電壓值通過A/D采集并輸送到DSP中,DSP將這個數值多次累計后求其平均值,并將其平均值和相對應的頻率點放入緩存,待到全部頻率點的壓控電壓數值均已經采集完畢,將所有數值做成一個頻率/壓控電壓的表格寫入FLASH芯片中保存下來,這樣則采集工作結束。圖4為采集階段的流程圖。

圖4 采集流程圖

2.3.2 正常工作流程

設置需要的頻率點,通過DSP對該頻率點的頻率控制字進行計算,并將計算出的頻率控制字送入PLL電路的相對應的芯片內,送數的同時把開關切換到預置狀態,從FLASH中將該頻率對應的壓控電壓數值讀出并寫入DA芯片,其輸出的模擬電壓就是環路的預置電壓,幫助PLL電路快速鎖定頻率。

需要注意的是,開關不能一直處于預置狀態,不然由DA送出的電壓一直存在就會干擾鎖存芯片的正常工作,所以開關預置狀態只能在送數時開啟,在送數結束后就應該立刻將其斷開以保證鎖相環能正常鎖定頻率。

為了方便測量,可以在一個頻率正常鎖定后(取得鎖定指示后)延遲一小段時間又開始輸入另一個頻率點。繼續以上操作,再次鎖定后再切回原先的頻率,使得頻率合成器在兩個一定跨度的頻率點之間來回循環切換,以方便使用儀器來測量這兩個頻率切換所需要的時間。

3 測試結果及結論

■3.1 測試結果

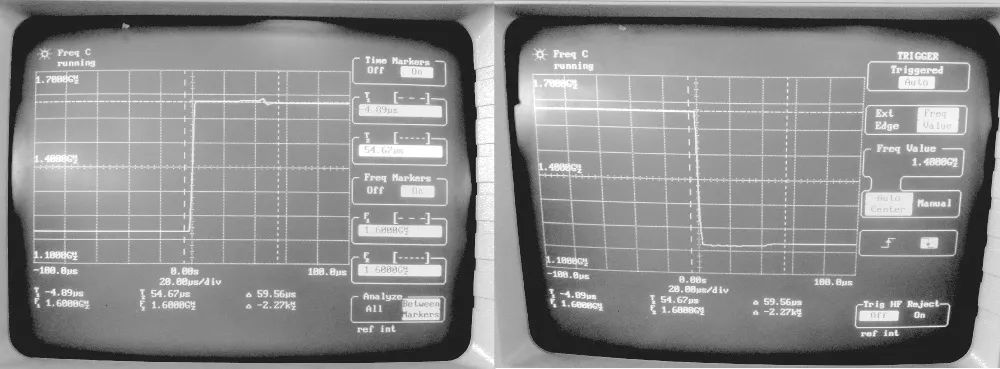

經過反復對電路進行指標優化以后,對換頻時間測量后發現,在1200M和1600M兩頻率已可縮短至60μs以內(頻率跨度400M,壓控電壓范圍2~13V,這個時間里面包括了預置時間4μs,送數時間30μs,環路相位捕獲時間20μs),測試結果如圖5所示。

圖5 加自適應精確預置技術的測試結果

對PLL去除自適應精確預置技術相關電路,重新測試換頻時間,兩個頻點間切換時間在400μs以上,測試結果如圖6所示。

圖6 不加自適應精確預置技術的測試結果

從上述測試結果來看,采用自適應精確預置技術的頻率合成方案能達到非常好得快鎖效果。

■3.2 結論

本文介紹了自適應精確預置技術的基本原理以及工程化實施方案,通過對實際樣品的測試試驗,證明了采用該快速方案的可行性,為以后高速跳頻頻率合成器的設計提供了一種新的參考思路。