一種新型信號發生器的設計

熊文

關鍵詞:FPGA;MCU;DDS;信號發生器

1引言

信號發生器是一種常用的信號源,廣泛應用于信息電子、通信系統和科學實驗等領域。它是一種為電子測量和計量工作提供符合嚴格技術要求電信號的設備。因此,信號發生器和我們熟悉的電量測試儀器(如電壓表)一樣是最普通、最基本的,也是應用最為廣泛的儀器之一,絕大部分電路及其電量的信號源都需要由信號發生器來提供。

直接數字頻率合成(Digital Direct FrequencySynthesis,DDS)技術是一種新的數字化技術。它不需要任何的振動,也不需要鎖相環,只需要將一系列的數據通過DAC來生成一個預定的模擬信號。由于采用了數字信號的高級處理原理和技術,信號的頻率變換速度較快,頻率分辨率高,頻率穩定度高,輸出信號頻率和相位可以迅速地進行程序控制,從而能夠便捷地進行信號的完全數字調制。本文根據信號發生器的特點及應用情況,以FPGA芯片為主要控制器,結合MCU與高速DAC模塊,設計出一款使用簡單方便、性能優良的新型信號發生器。

2信號發生器硬件設計

本設計采用FPGA與MCU雙核心,外接DAC模塊來完成DDS信號發生器的設計實現。以“FPGA+DAC”與濾波器負責完成DDS功能的實現,以“MCU+”屏幕與外圍負責完成人機交互的功能。本設計采用“雙子板+底板”的設計,子板將MCU與FPGA的所有引腳都引出到底板,以便擴展,同時在底板上引出多個硬件接口,可大大提升該發生器的功能擴展性。

2.1FPGA子板介紹

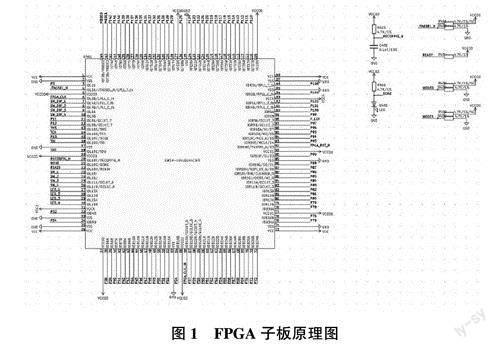

本設計的FPGA子板采用GWIN-LV4LQ144C615芯片來構建,該芯片是高云GWIN系列產品,其具備相當豐富的邏輯能力,具備各種I/O電平標準,并內嵌了塊狀靜態隨機寄存器、數字信號處理模塊、鎖相環節等新技術。另外,在其內嵌入了Flash技術,是一種具備非易失性的FPGA產品,具有低功率、高穩定性、商品體積較小、封裝形式多樣、使用方便靈活等優點。

圖1是以GWIN為核心的FPGA子板電路圖,本設計在該芯片以及其他芯片的電源部分增加了去耦電容、旁路電容以及磁珠來進行抗電磁干擾優化。

2.2MCU子板介紹

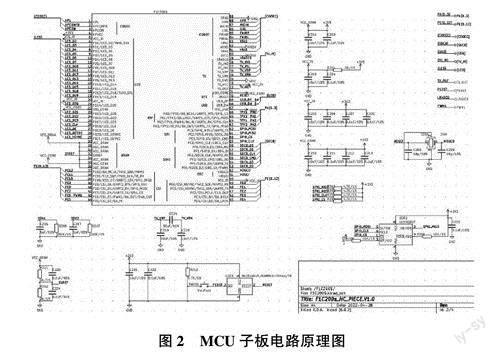

MCU子板采用F1C200S芯片作為內核,主要負責進行交互功能,可接常用的外部設備(如屏幕、Wi-Fi與紅外等)。F1C200S內帶有高速的通信總線接口,大大提高其運行速度與能力,以及2個外設接口、1個USB接口,還配有常用的攝像頭接口、顯示屏接口,音頻接口等[1]。

因為F1C200S較為方便配置以及具有極為經濟的價格,加之其內置的多項資源可以大大簡化硬件設計難度,因此其被廣泛應用。

F1C200S支持多個系統,在此選用Linux系統進行操作,能有效降低開發難度。圖2是以F1C200S為核心的MCU子板電路原理圖。

2.3DAC模塊介紹

在本設計中,DAC模塊選用3peakdac模塊進行設計,搭配FPGA即可實現發生器任意波形的產生功能。該模塊的特點有:(1) 16管腳直插或郵票孔封裝;(2)方便快捷的搭載FPGA最小系統;(3)適用于雙通道高速數據采集項目;(4)單通道10位/125Msps高速運行;(5)輸出模擬信號2Vpp;(6)3.3~5V穩壓供電電源。

2.4電源模塊

電源是任何設備必不可少的部分,本系統分別對FPGA和MCU提供了專門的電源模塊。

2.4.1FPGA電源模塊

本板根據GWIN芯片的自身特性,電源模塊為FPGA提供1.2 V的核心電,并提供1.2 V,1.8 V,2.5 V和3.3V四種電壓作為Bank電壓的可調選項,另為VCCX提供3.3V或2.5V作為可選的輔助電壓。本板1.2V的核心電采用SGM2028-ADJ進行供電。SGM2028是一款低功耗、低噪聲、低壓差、CMOS工藝的線性穩壓器,輸入電壓范圍為2.5~5.5V。SGM2028使用靜聽供電的系統,一個連接在器件BP接口的低外部噪聲旁路電容器,能夠進一步降低噪聲。

2.4.2MCU電源模塊

本板采用了EA3036電源模塊,這是一顆三通道的Boost DC-DC電源芯片,用來提供1.2 V,2.5 V,3.3V的電平電源。EA3036采用了20引腳的QFN 3×3封裝,有效節省了PCB面積。芯片內整合了3個同時降壓控制的變換器,可以同時在低負荷和高負載的工作下實現高性能控制。內部的架構也改善了整個電路設計。另外,還有獨立的使能控制器,也能任意調整上電時間的順序[2]。

3信號發生器軟件設計

3.1FPGA軟件部分

FPGA軟件部分主要采用“Gowin+Visual StudioCode”進行編譯,采用Verilog語言來進行編寫。由Gowin_V1.9.8.03進行項目構建、編譯與燒錄。由Visual Studio Code來進行Verilog的編寫,這基于其極高的擴展性,有著大量的插件來提升它的功能性[3]。

下面介紹主要的Verilog模塊。

(l)PLL.v:這一步是為了使GWIN內置的PLL模塊代碼上調,用Gowin內置的IP核形成一個PLL.v文件。

(2) ROM.v:此模塊是在FPGA內部形成一塊ROM并存人正弦波的波形,以供查找表使用。

(3) Divide.v:采用if來進行分頻,并通過輸入不同的值來控制輸出頻率,以達到DDS頻率控制。

(4) SPI.v:調用IP核,實現SPI功能,完成與MCU的交互功能。

3.2MCU軟件部分

3.2.1BootLoader啟動程序

PC在啟動時,首先進入BIOS,再根據BIOS中配置信息引導后續的啟動操作系統,如Windows啟動。而對于嵌入式Linux啟動,則沒有BIOS,而是用BootLoader來進行程序的引導。在嵌入式操作系統中,BootLoader是在操作系統內核運行之前運行。可以初始化硬件設備、建立內存空間映射圖,從而將系統的軟硬件環境帶入一個合適狀態,以為最終調用操作系統內核準備好適合的環境[4]。

BootLoader啟動過程可分為stagel,stage2兩個階段,其中stagel完成初始化硬件,如CPU的寄存器、內存的控制器,來為stage2的運行準備內存空間。

當Arm開發板上電以后,第一個要加載到內存并運行的程序就是BootLoader.本設計選擇了U-boot作為引導程序[5]。

3.2.2Linux啟動程序

FIC200S的核心licheepi nano已經完成了Linux官方源碼的移植。所以可以直接采用licheepi nano文件進行使用,并燒錄到TF卡中,從而使設備進行Linux的啟動[6]。

3.2.3界面顯示程序

本設計采用LittlevGL進行界面顯示。

LittlevGL是一款功能強大的用戶界面顯示軟件,調用簡單方便。LittlevGL自帶大量的控件,如工具、視窗、按鈕、標志、list、圖形等,還能夠自定義控件。LittlevGL還支持眾多特效,如透明、陰影、手動展示隱藏的滑動條、頁面轉換動畫、圖標開啟結束動畫、光滑的拖拽控制、分層屏幕、反鋸齒效果、只耗少許內存的字體等[7]。

4系統調試及結果分析

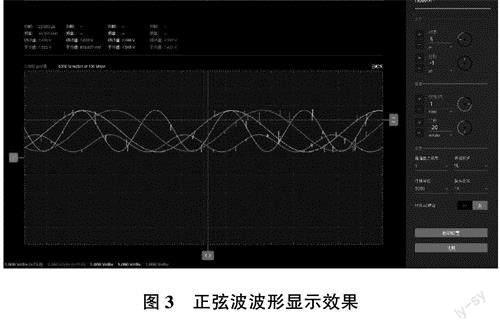

本設計采用了ADALM2000中的示波器功能來對信號器產生的波形進行顯示與調節。圖3顯示了由該示波器所采集的正弦波波形信號,為改變頻率與電壓后的多次顯示效果。

由圖3可知,本設計實現了不同頻率、幅值下的正弦波形的顯示,波形失真率較低,達到了預期效果。此外,其他幾種常見波形(如矩形波、三角波等)都可以得到很好的顯示效果。

5結束語

本文介紹了一種基于DDS技術信號發生器的組成原理與功能,并重點介紹了該信號發生器的硬件組成部分及軟件實現部分,最后對信號波形結果進行顯示與調節。該信號發生器功能齊全、操作方便、擴展性強,具有一定的使用價值。