原子層沉積法制備ZnO薄膜晶體管教學研究

陳雪 吳宏偉

文章編號:1003?6180(2023) 03?0073?05

摘? 要:采用原子層沉積法制備ZnO薄膜晶體管,研究高溫退火對其性能的影響,并將其引入半導體物理課程教學,讓學生更加直觀了解半導體的樣品制備和測試分析,更加有效地培養學生的探索創新精神.

關鍵詞:電子器件;半導體物理;后處理

[? ?中圖分類號? ? ]G642 [? ? 文獻標志碼? ?]? A

Teaching Research on Preparation of ZnO Thin Film

Transistor by Atomic Layer Deposition

CHENG Xue,WU Hongwei

(School of Mechanics and Photoelectric Physics,Anhui University of Science and Technology,

Huainan 232001,China)

Abstract:ZnO thin film transistors were prepared by atomic layer deposition and the effect of high temperature annealing on their properties was studied. By introducing these research processes into the teaching process of semiconductor physics,students can have a more intuitive understanding of the preparation,testing and analysis of semiconductor samples,and cultivate their spirit of exploration and innovation more effectively.

Key words:electron device; semiconductor physics; post-processing

近年來,氧化物半導體作為一種用于薄膜晶體管(Thin Film Transistors,TFTs)的活性層材料引起了廣泛關注.與傳統的非晶硅TFT相比,氧化物TFT具有較高的電子遷移率,與低溫多晶硅TFT相比,氧化物TFT制備溫度低,均勻性好.氧化物半導體禁帶寬度大,在可見光范圍內透明,對未來透明柔性電子器件的發展具有重要意義.銦鎵鋅氧(IGZO)TFT是目前唯一實現量產的材料,因其使用含有稀有金屬In和Ga元素的溝道材料制備TFT,故生產成本高.ZnO二元化合物薄膜成分簡單、存儲豐富、價格便宜、無毒、禁帶寬度大、制備溫度低,未摻雜的ZnO薄膜含有高密度的晶界和未填充的陷阱密度,TFTs開態電流小、亞閾值擺幅大(0.90 V/dec)、遷移率低(1.6 cm2V-1s-1).利用先進的薄膜制備手段,加上工藝的優化,ZnO TFT的遷移率可以超過20 cm2V-1s-1,甚至優于IGZO等多元化合物的性能.因此,進一步深入研究ZnO TFT以滿足商業應用的標準是十分必要的.

制備氧化物半導體薄膜的手段很多,原子層沉積由于其獨特的生長機理,在制備超薄薄膜、3D集成等領域具有很大優勢.2009-2018 年,使用 ALD 制備氧化物 TFT 的文章總數達到 100 篇左右,其研究熱度依然高漲,高性能的 TFT不斷被研發出來.[1-4]研究發現,使用ALD法制備ZnO薄膜時,由于 ZnO 材料總是具有很高的載流子濃度,通常聚焦研究 ZnO 材料的厚度、后處理方法(如O2 plasma 處理)以及使用金屬氧鍵比 Zn-O 更大的金屬離子進行摻雜,抑制氧空位的產生,從而控制ZnO薄膜中的電子濃度.這些手段的使用,不可避免地會增加生產成本,提高制備工藝的復雜性,不利于大規模產業發展.本文采用原子層沉積法低溫制備ZnO薄膜,研究退火溫度以及退火時間對TFT性能的影響規律.通過對原子層沉積技術的特點、薄膜晶體管的工作原理、制作流程的介紹以及結合半導體物理學的相關知識對器件進行分析,讓學生深入了解科研思維的訓練過程,了解半導體知識在實際中的應用[5-6],了解所學知識在未來的應用前景,從而提高學生的學習興趣,提高學習效果.

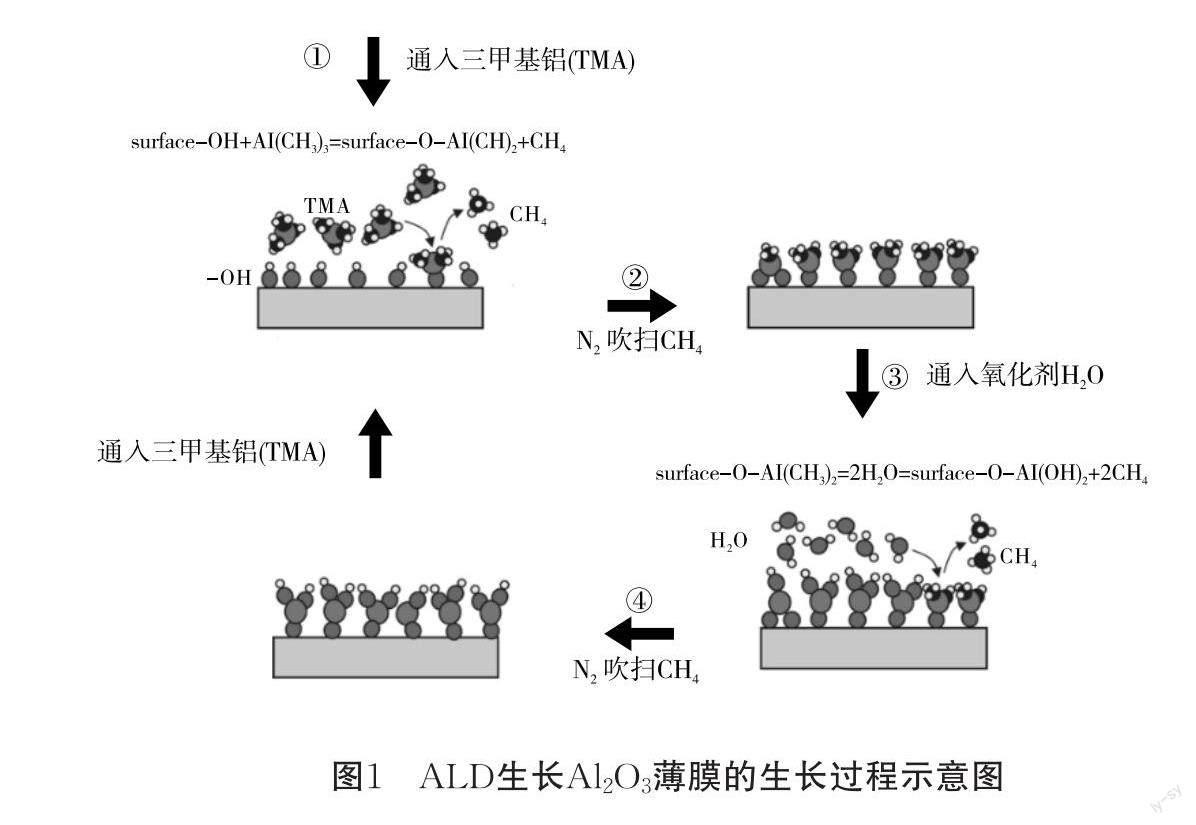

1 原子層沉積技術的特點

原子層沉積(Atomic Layer Deposition,ALD)是以化學反應為基礎的一種薄膜制備方法,將不同的化學前驅體源以氣體的形式交替通入反應腔,通過調節腔室溫度,提供熱能,使之在襯底表面發生化學反應,從而生成所需要的薄膜.圖1為Al2O3薄膜生長過程示意圖.襯底由于晶格周期性在表面的突然中止而出現表面懸掛鍵,大氣中的水分子與該懸掛鍵發生反應,形成化學吸附的羥基(—OH),覆蓋于襯底表面.當三甲基鋁以脈沖形式通入ALD腔室后,TMA的一個或者兩個甲基就會與襯底表面的—OH發生反應,形成CH4.持續通入TMA,使襯底表面的每個—OH都與TMA分子反應,此時即使繼續通入TMA,也不再有多余的—OH與之反應,表面達到自限制狀態.接著將控制TMA的氣動閥門關閉,向腔室中通入高純N2氣,利用載氣提供的動力,將生成的CH4以及多余的TMA清除.再向腔室中以脈沖形式通入氧化劑(如H2O).襯底表面化學吸附的—CH3與H2O發生反應,在襯底表面形成—OH鍵以及副產物CH4,利用自限制效應反應完全后,關閉H2O源氣動閥,再次通過高純N2將多余的H2O分子和副產物CH4清除.這就是一個完整的ALD生長周期.通過不斷重復以上步驟,就可以得到一定厚度的Al2O3薄膜.由其生長原理可知,薄膜生長過程中,每次化學反應都和襯底表面的反應官能團數量密切相關,當襯底表面官能團反應完全,即使通入過量的前驅體源,也沒有與之反應的位點,因此,ALD反應可以達到自限制,在原子尺度上控制薄膜的生長.隨著集成電路產業不斷朝著微型化方向發展,傳統的硅基電子器件橫向尺寸不斷達到發展極限,人們開始慢慢朝著三維堆棧結構方向探索.這時就需要薄膜沉積時具有高保型性,納米尺度上厚度精確可控.ALD技術在這種社會發展中逐漸被工業界所青睞,成為半導體行業中最具發展潛力的薄膜制備手段.

2 薄膜晶體管工作原理

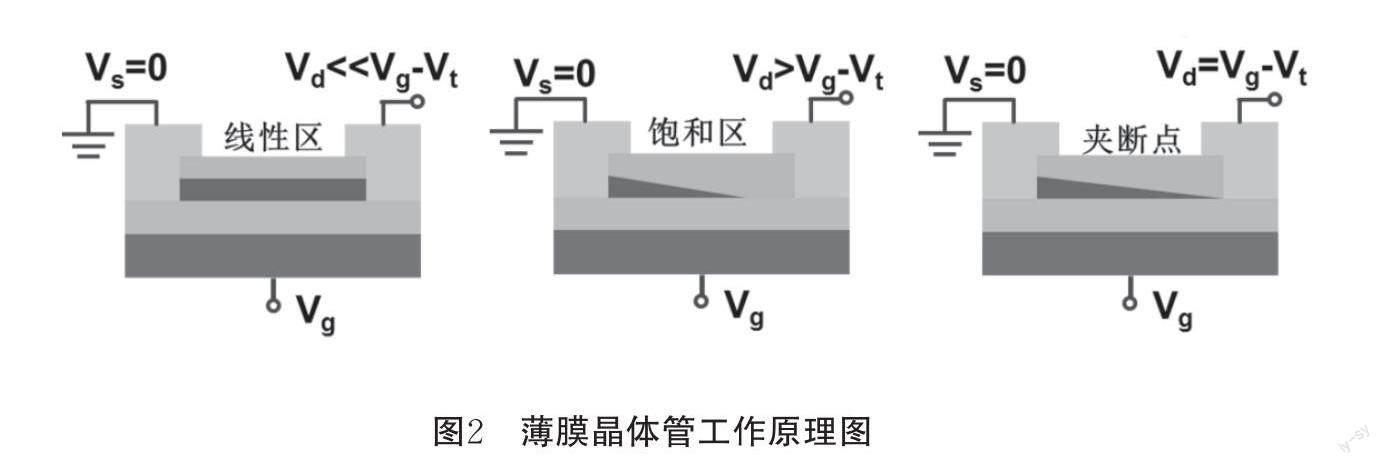

在半導體行業中,薄膜晶體管(Thin film transistors,TFTs)可用作顯示器背板電路驅動電路的開關,控制單位像素,防止它們之間發生串擾.隨著氧化物薄膜晶體管領域的發展,有望替代Si基器件成為集成電路領域的新秀.[7-9]TFT是一種簡單的三端半導體器件,器件結構如圖2所示.工作時,可以通過在柵極施加電壓控制位于源極和漏極之間的半導體中的電流.絕緣層插入半導體和柵極之間,通過介電層和半導體界面的表面場效應實現電流調制.

薄膜晶體管工作原理.以n型溝道底柵交錯型 TFT 為例.首先定義一個閾值電壓VTH,即溝道形成時的電壓.由于溝道為 n 型半導體,電子為多子.當柵極電壓 VGS>0 時,由于電場效應,溝道中的電子會被吸引至溝道和絕緣層的界面.在 VGS< VTH 時,溝道中感應的電子還不足以形成導電溝道,雖然此時漏極有正電壓(VDS),但是源漏電流 IDS 很小,器件表現為截止狀態.當 VGS>VTH 時,電場足夠大,導致溝道和絕緣層界面附近的電子積累得足夠多,形成導電溝道,在 VDS 的作用下產生電流,IDS 隨著 VDS 的增大而線性增加.由于溝道受柵極電壓以及漏極電壓的共同作用,所以溝道中的電場不是均勻場,而是漏極附近的電場要大.當 VDS 增大到和 VGS-VTH 相等時,夾斷點形成,導電溝道被夾斷.此時繼續增加 VDS,電壓大部分都落在夾斷區,IDS 不會隨 VDS 變化,達到飽和區.由此可見,當柵極電壓小于閾值電壓時,TFT為關斷,電流小;當柵極電壓大于閾值電壓時,TFT打開,有電流流通.基于此,利用柵極電壓控制晶體管的開關從而對單位像素進行控制,這是有源矩陣液晶顯示背后像素驅動電路的常用手段.

3 原子層沉積法制備ZnO薄膜晶體管教學

課堂教學中,闡述絕緣層和溝道層材料的選擇,加深學生的理解.選擇P型重摻雜Si作為襯底,將襯底依次放入丙酮、酒精中超聲10 min以清洗表面的有機污染,氮氣吹干后直接放入ALD反應腔室中.對腔室進行加溫處理,以獲得化學反應時所需要的熱能.選擇在100 ℃條件下,使用三甲基鋁和H2O作為反應源,生長40 nm Al2O3薄膜作為絕緣層,使用二乙基鋅和H2O作為反應源,生長30 nm ZnO作為溝道層.半導體薄膜之所以可以用作薄膜晶體管的溝道層,是因為其載流子濃度可以用電場調控.如果使用金屬作為溝道層,則薄膜晶體管會一直是導通狀態,若使用絕緣層,則一直是關斷狀態.絕緣層的作用是使柵極-絕緣層-溝道層可以構成一個電容器,依靠電容效應,可以很容易達到柵極電壓控制溝道層中的載流子濃度.[1]

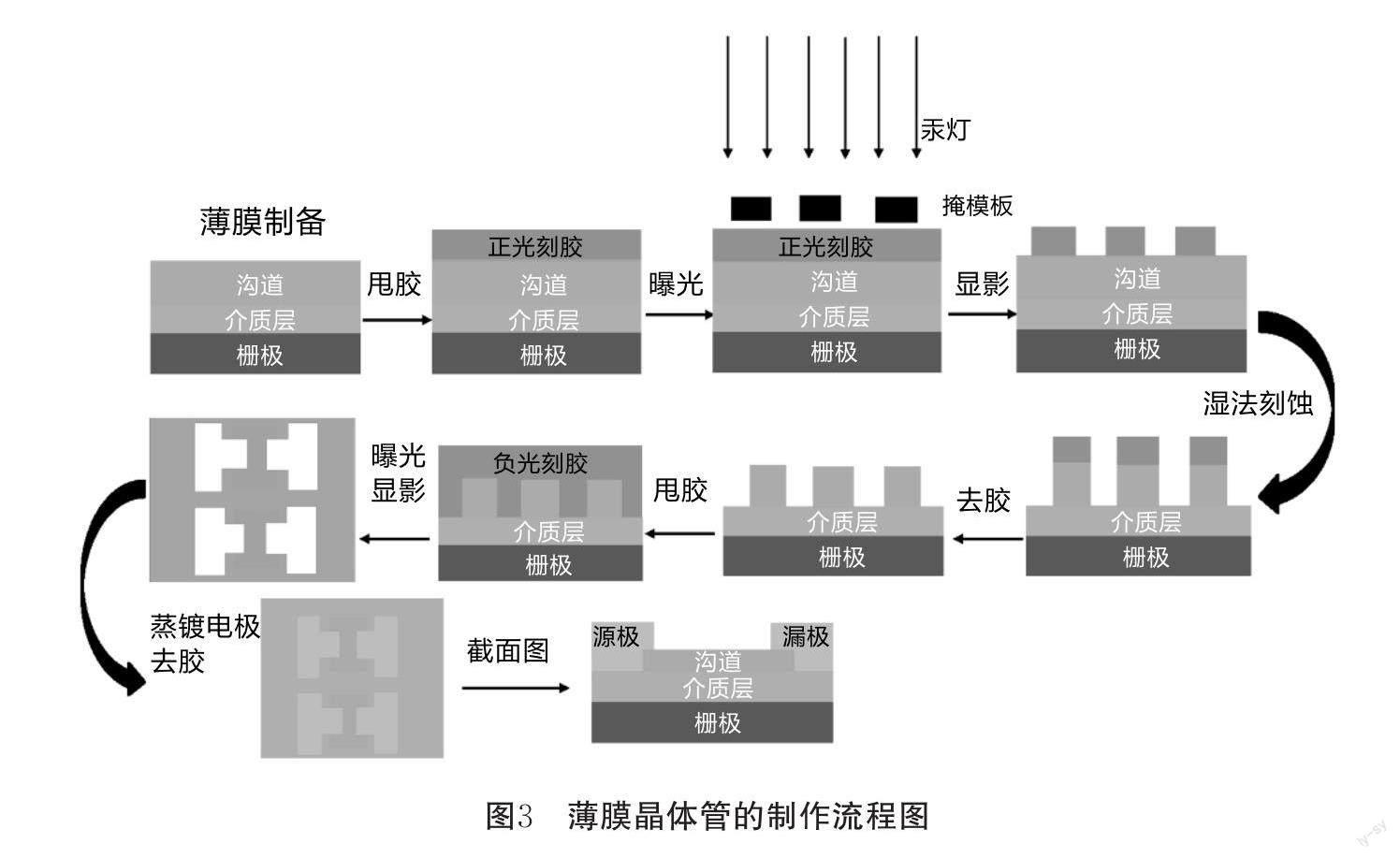

對TFT進行光刻處理,將溝道層刻開,防止由于邊緣電流效應而導致遷移率高估.

(1)使用勻膠機在樣品上旋涂一層正光刻膠,接著將襯底放置在所制作的溝道掩膜版下,使用紫外光照射后,再放入顯影液中顯影.這樣直接暴露在紫外光下的正膠就會在顯影液的作用下被腐蝕,只留下溝道部分有光刻膠.然后將帶有溝道圖案的襯底放入稀鹽酸,將多余ZnO腐蝕,丙酮洗去光刻膠,就可以得到ZnO溝道圖案.

(2)源漏電極的制作.使用旋涂機在襯底表面旋涂一層負膠,接著將襯底放置在所制作的源漏電極掩膜版下使用紫外光照射,再放入顯影液中顯影.形成源漏電極圖案.將襯底放入熱蒸發腔室蒸鍍Cr/Au電極后,再利用丙酮去除光刻膠,就得到完整的薄膜晶體管器件圖.整個流程如圖3所示.

4 ZnO薄膜晶體管的測試與分析教學

課堂教學中,講解半導體材料受溫度、光照等外部因素影響的機理,闡述薄膜晶體管高溫退火后的性能變化,結合實驗測試結果,實現學生理論與實踐的結合,更加有效地培養學生的探索創新精神.

圖4為ZnO TFT經過不同溫度退火、不同時間后的轉移特性曲線.從圖中可以看到,沒有經過退火的ZnO TFT即使在-10 V的柵極電壓下也不能將溝道中的電子耗盡,說明ZnO半導體薄膜內部載流子濃度太大,不適合直接用作溝道層.將TFT放置在熱板上進行高溫退火,300 ℃下僅需要1 min就可以將TFT的漏電流從10-5 降低至10-12 A,開關比直接提高到108.

用公式[μ=LWVdsCox×?Ids?Vgs],[SS=(dlogIdsdVgs)-1],分別提取出TFT的遷移率和亞閾值擺幅(SS).式中,L,W分別為TFT溝道的長和寬,Cox為Al2O3絕緣層單位面積的電容密度.[10-11]將Ids1/2-Vgs曲線的線性部分外推,與VGS軸的交點得到閾值電壓VTH,提取出的參數見表1.表1中的數據表明,未經過高溫退火的ZnO薄膜內部電子濃度含量高,不適合作為溝道層材料;空氣中高溫退火是降低溝道內部電子濃度的有效手段;退火時間越長,閾值電壓越大,SS越小,遷移率越低,需要權衡他們之間的取舍;低溫長時間退火比高溫段時間退火具有更高的遷移率,更小的亞閾值擺幅,更有利于高性能TFT的獲得;較低溫度退火適用于柔性襯底,可為柔性TFT制備提供機遇.

5 結論

本文以原子層沉積法制備ZnO TFT退火研究為例,介紹半導體器件的制備流程、光刻手段以及分析測試知識.通過不同溫度、不同時間退火器件的性能對比,得到氧化物薄膜中載流子濃度含量對晶體管性能的影響.高溫退火可有效降低氧化物薄膜中的電子濃度,提高開關比.低溫下長時間退火更有利于高性能的獲得.原子層沉積法制備ZnO薄膜晶體管退火教學引入薄膜晶體管科學研究過程,讓學生更加直觀了解半導體的樣品制備,測試分析,更加有效地培養學生的探索創新精神.

參考文獻

[1]Sheng J.,Lee J.H.,Choi W.H.,Hong T.H.,Kim M.J.Park J.S..Review Article:Atomic layer deposition for oxide semiconductor thin film transistors:Advances in research and development [J]. J. Vac. Sci. Technol.,2018(36):060801.

[2]Seul H.J.,Kim M.J.,Yang H.J.,Cho M.H.,Cho M.H.,Song W.B.,Jeong J.K.Atomic Layer Deposition Process-Enabled Carrier Mobility Boosting in Field-Effect Transistors through a Nanoscale ZnO/IGO Heterojunction [J]. ACS Appl Mater Interfaces,2020,12(30):33887-33898.

[3]Chen X.,Wan J.,Wu H.,Liu C.ZnO bilayer thin film transistors using H2O and O3 as oxidants by atomic layer deposition [J]. Acta Materialia,2020(185):204-210.

[4]Sheng J.,Hong T.,Kang D.,Yi Y.,Lim J.H.,Park J.S.Design of InZnSnO Semiconductor Alloys Synthesized by Supercycle Atomic Layer Deposition and Their Rollable Applications [J]. ACS Appl Mater Interfaces,2019,11(13):12683-12692.

[5]劉永智,解立強,梁盛德,等.開放與傳統:兩種范式物理實驗教學比較研究[J].牡丹江師范學院學報:自然科學版,2011(1):71-72.

[6]王莉,樊柏村,楊艷.淺談在大學物理教學中培養學生的物理思維———以光的干涉和衍射為例[J].牡丹江師范學院學報:自然科學版,2008(4):69-70.

[7]Kim,H. J.,Park,K.,Kim,H. J.High‐performance vacuum‐processed metal oxide thin‐film transistors:A review of recent developments[J]. Journal of the Society for Information Display,2020,28(7):591-622.

[8]Ji,D.,Jang,J.,Park,J.H.,Kim,D.,Rim,Y.S.,Hwang,D.K.,Noh,Y.Y.Recent progress in the development of backplane thin film transistors for information displays[J]. Journal of Information Display,2021(22):1-11.

[9]Lee,H. E.,Kim,S.,Ko,J.,et al.Skin-Like Oxide Thin-Film Transistors for Transparent Displays[J]. Advanced Functional Materials,2016,26 (34):6170-6178.

[10]Brotherton S.D.Introduction to Thin Film Transistors[A]. Cham,Switzerland:Springer International Publishing Switzerland,2013.45-67.

[11]Schroder D.K.Semiconductor Material and Device Characterization [A]. New Jersey:John Wiley & Sons,Inc.,2005. 319-387.

編輯:吳楠