基于FPGA的通用自動測試平臺設計

摘 要:為了實現電子產品在調試、測試中測試指令下發和測試數據獲取的自動化,結合FPGA技術、SCPI命令、儀表程控、QT軟件開發平臺等提出一種通用自動測試平臺設計方案,在傳統調試測試方式的基礎上有效提升測試效率,降低測試成本,實現測試指令下發以及數據處理的一體化和自動化。

關鍵詞:自動測試;FPGA ;SCPI;儀表程控;QT

引言

隨著電子信息技術高速發展,數字化、模塊化的高集成度電子產品被廣泛應用于各個領域,對于產品功能調試,測試驗證,售后維修的要求逐步提升。手動使用儀器儀表和測試工裝的測試手段落后,效率低下,為了提高生產調試效能,節約多方成本,通用自動化測試平臺的研制需求日益遞增。合成儀器技術(Synthetic Instruments,SI)是美國國防部為開發新一代自動測試系統提出的關鍵技術[ 1 ],該技術旨將多種標準儀器儀表通過程控的方式與計算機進行數據交互,實現計算機對儀器儀表的參數設置以及測量結果的自動獲取[2-3]。FPGA能夠產生滿足絕大多數被測電子設備所需的專用信號,如:控制指令、時鐘信號等,目前在數據采集處理、邏輯功能實現等多種領域得到了廣泛的應用[ 4 ]。本文提出一種基于FPGA的通用自動測試平臺設計,通過將合成儀器技術與FPGA技術二者結合,結合目前常用的模塊化硬件作為通用自動測試平臺的硬件組成[5-6],外觀結構為一臺便攜式加固計算機,通過SCPI命令及VISA I/O庫實現對儀表程控設置,上位機軟件采用QT平臺開發以支持WINDOWS、銀河麒麟等多個操作系統,實現跨平臺運行。通用自動測試平臺能夠實現系統的參數設置、測試流程編輯以及數據的自動捕獲、處理和可視化顯示。

1 通用自動測試平臺總體設計

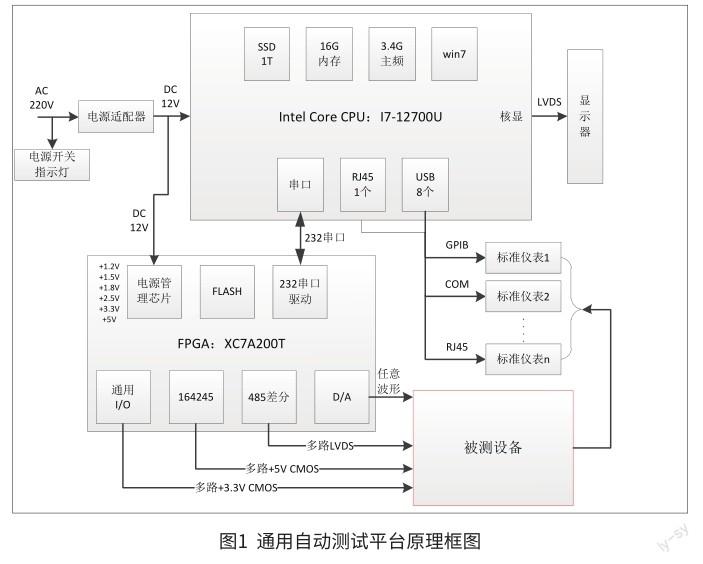

圖1是通用自動測試平臺的原理框圖,AC220V市電經電源適配器后變為12V直流送至計算機主板及FPGA核心板,FPGA核心板中使用DC/DC直流降壓芯片構成電源管理組,將DC+12V變為板內其余器件所需的DC+1.0V、+1.5V、+1.8V、+2.5V、+3.3V、+5V等多種電壓;核心板上配有256M的FLASH與FPGA通過標準SPI總線連接,便于上電后加載程序。將FPGA的BANK13~16內所有通用I/O引出,部分引腳作為+3.3V CMOS單端信號直接輸出,部分引腳通過164245對其進行驅動和電平轉換后變為+5V CMOS單端信號輸出,其余部分引腳經過485差分轉換芯片后變為標準485 LVDS格式信號輸出,此外為了滿足某些特殊的測試需求,對FPGA的+1.8V及+2.5V內核BANK34/35的輸出引腳后端增加D/A模塊,能夠產生靈活且滿足時序要求的任意波形測試信號。FPGA核心板通過232串口與計算機主板之間進行信息交互,接收主板控制指令,回傳當前工作狀態。計算機主板上配有8個標準USB2.0/3.0兼容接口以及一路RJ45網絡接口,能夠同時對多路符合IEEE-488.2通用命令的儀器儀表進行遠程控制,配置儀表參數,接收測試結果。

2 通用自動測試平臺的設計實現

2.1 核心器件的選型及硬件設計

計算機主板選用研華MIO-5272,實物見圖2,其內部核心為第七代英特爾 酷睿 U系列CPU,TDP功耗低至15W,雙通道DDR3L內存高達16 GB,具有可擴展至8路的USB接口,支持多個GPIB儀表的程控。

FPGA核心板為自主設計且具有豐富種類、可靈活配置的多路輸出接口,組成框圖見圖3。FPGA芯片選用Xilinx公司的XC7A200T-1FFG1156I,該芯片具有200萬邏輯單元數量,500路通用I/ O接口,數據速率最高可達6.6Gb/s[7],可提供多類被測產品所需的專用信號,電源管理組選用TI公司的TLV62130直流降壓芯片,其支持高達3A的輸出電流,通過配置不同的外部分壓電阻可獲得+0.9V~+5.5V的輸出電壓,滿足核心板內所有器件所需。232串口驅動電路選用MAXIM公司的MAX3232芯片,負責將232電平轉換為FPGA_UART要求的+3.3V TTL標準電平。FLASH選用MICRON公司的N25Q256系列芯片,與FPGA之間為標準QSPI總線接口,用于存儲可執行bin程序文件,上電加載,FLASH內部可分16個緩存區,對于不同測試的應用,可由上位機的232串口通過指令控制FPGA隨時調用FLASH內部的不同bin文件適配不同的測試需求。50MHz晶振選用國產13所的有緣晶振,通過FPGA內部集成的PLL,對50MHz晶振進行20倍頻后得到高達1GHz的系統時鐘,以高速的系統時鐘保證提供給被測設備最小脈寬可達1ns的測試信號。此外,核心板內配有4片16路245電平轉換電路SN74ALVC164245、10片4路485差分驅動電路SN75LBC172及2片14位、500Mbis/s高速D/A芯片DAC5675,負責完成FPGA通用I/O引腳+3.3V CMOS至+5V CMOS和485 LVDS的信號轉換,DAC5675負責產生部分測試需求的任意波形信號。

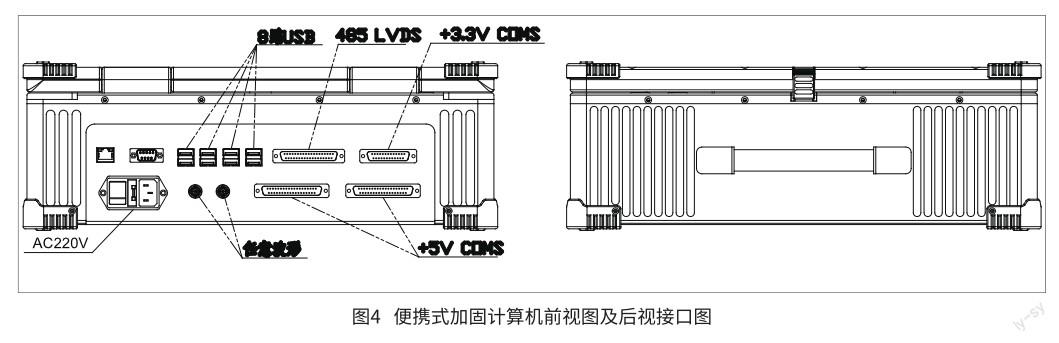

通用自動測試平臺采用便攜式加固計算機的結構形式設計,外殼采用5106標準金屬機箱,內置計算機主板,FPGA核心板及電源適配器,所有接口均在便攜式加固計算機后方,USB、網絡、串口通過標準接口引出,核心板的輸出信號根據信號類型的不同通過不同的矩形連接器引出,D/A后的信號通過BNC/ SMA接口引出。外觀示意見圖4。

2.2 軟件設計

通用自動測試平臺軟件分為嵌入式FPGA軟件及上位機軟件兩類,嵌入式FPGA軟件主要用于提供被測設備所需的專用信號,結合被測設備的測試需求,通過專用接口送出不同電平、不同信號類型的控制信號、時序信號等。上位機儀器儀表程控軟件通過標準GPIB接口完成對所需儀表的一鍵設置,并對測試結果進行采集和分析,實現被測設備性能的自動測試。

2.2.1 嵌入式FPGA軟件

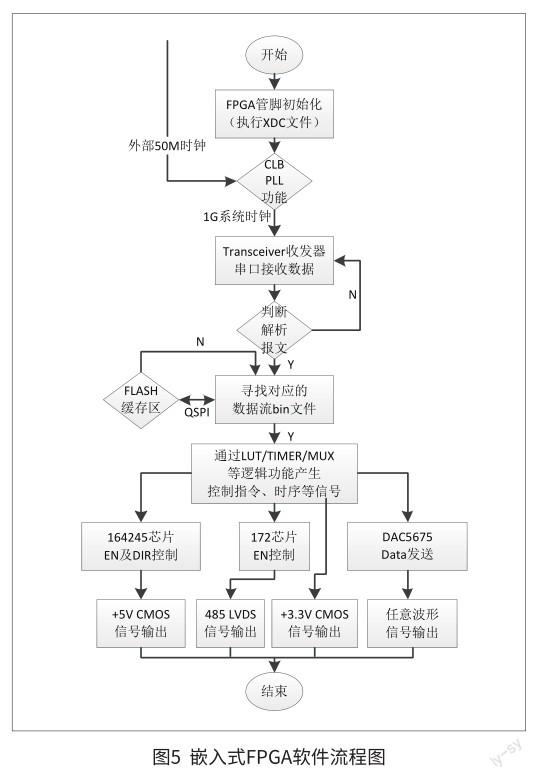

針對FPGA芯片的邏輯功能開發,通過Xilinx的官方軟件Vivado作為本次設計的EDA開發平臺,使用Verlog HDL語言編程,軟件會自動完成邏輯編譯、綜合、打包、布局布線、仿真邏輯映射(XDC)等工作[8],通過核心板上的FLASH芯片,上電后將程序加載至FPGA芯片中,實現預設的硬件功能。其軟件設計流程詳見圖5。

程序開始運行后,FPGA首先加載FLASH中初始化數據流origin.bin中的XDC配置項完成初始化管腳配置,通過CLB中多個LUT集成PLL功能將外部輸入的50MHz時鐘倍頻至1GHz,提供給FPGA芯片作為運行所需的系統時鐘。之后等待Transceiver收發器接收上位機發來的UART數據,成功接收報文并解析后,明確當前的測試場景及應用。隨后通過QPSI接口從FLASH的16個緩存區內找到對應當前測試需求的最終數據流bin文件后重新加載,依據最終程序的配置和響應,調用BANK13~16的多個CLB單元,通過LUT查找表配合具有嵌套關系的MUX復用器及最高可達1GHz的高級定時器,產生滿足邏輯要求的+3.3V CMOS類型通用I/O接口輸出,最后對FPGA后端外圍電路的EN使能端、DIR方向端、DAC芯片的14位數據進行發送和控制,最終得到在當前測試應用下所需的專用信號。

2.2.2 通用測試平臺上位機軟件

通用測試平臺上位機軟件采用Qt開發平臺,通過SCPI命令及VISA I/O庫實現對儀表程控設置。自動測試軟件支持WINDOWS、銀河麒麟等多個操作系統,能夠實現跨平臺運行。

2.2.2.1上位機軟件組成

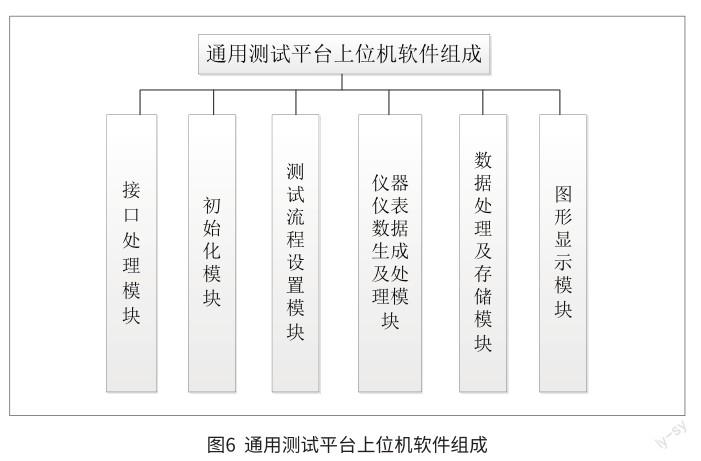

根據實現功能不同,將上位機軟件進行模塊化劃分,如圖6所示,通用測試平臺上位機軟件由接口模塊、初始化模塊、測試流程設置模塊、儀器儀表數據生成及處理模塊、數據處理及存儲模塊、圖形顯示模塊組成。

接口處理模塊:實現上位機與FPGA核心板、上位機與儀器儀表程控接口的通信控制,對FPGA核心板以及儀器儀表鏈接狀態進行實時監測;

初始化模塊:實現上位機系統內存初始化、各變量初值初始化、接口初始化以及儀器儀表默認參數初始化設置;

測試流程設置模塊:實現用戶對被測設備測試項目、測試模式、測試流程以及測試數據存儲和顯示的設計;

儀器儀表數據生成及處理模塊:根據相應的測試設置對所選的儀器儀表生成相應的SCPI命令,對儀器儀表所回傳的標準數據進行處理形成用戶所需的測試數據;

數據處理及存儲模塊:根據用戶的設置對測試數據結果進行篩選、劃區等處理并存儲;

圖形顯示模塊:對存儲的最終測試數據以圖形、圖像或圖表形式進行可視化顯示。

2.2.2.2上位機軟件工作流程

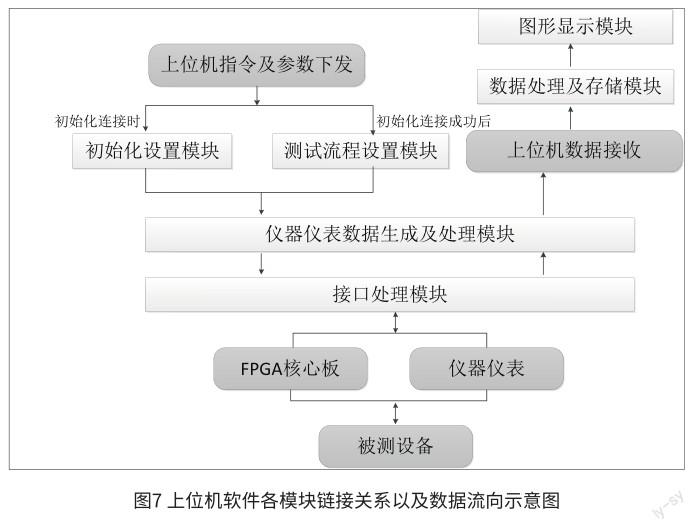

通用自動測試平臺上位機軟件各模塊連接關系以及數據流向示意圖如圖7所示。

上位機軟件工作基本流程如下:

a)發送FPGA核心板、被測設備、儀器儀表建立連接命令,與FPGA核心板、被測設備、儀器儀表建立連接;

b)發送FPGA核心板、被測設備、儀器儀表初始化命令,初始化FPGA核心板、被測設備、儀器儀表;

c)發送FPGA核心板、被測設備、儀器儀表參數設置命令,觀察反饋信息。若反饋信息正確,則表示連接成功,反之,連接失敗。檢查FPGA核心板、被測設備、儀器儀表狀態,若狀態正常,則返回上一步,否則,人工修正連接;完成FPGA核心板、被測設備、儀器儀表相關參數設置;

d)FPGA核心板、被測設備、儀器儀表連接成功后,選擇相應測試項目;

e)根據測試需求,設置測試模式(包括單步測試、輪循測試、交檢測試等);

f)下發相應測試模式下儀器儀表、FPGA核心板參數設置,設置成功后,需將設置參數反饋至上位機,等待測試人員確認;

g)各項準備工作完成后,點擊開始測試。等待被測設備相關性能基本穩定并達到可測狀態、儀器儀表測試結果穩定后,上位機讀取儀表測量結果并在軟件系統界面可視化刷新顯示,判斷后續是否有未測試項目,直至所有測試項目測量完畢,將測試數據根據用戶選擇以.Txt、.doc、.xsl等格式進行存儲。

通用測試平臺上位機軟件基本工作流程圖如圖8所示。

3 結語

本文提出并設計了一種基于FPGA的通用自動測試平臺設計,對電子產品在調試、測試中測試指令的下發和測試數據獲取及處理實現了全自動化控制。基于FPGA的通用自動測試平臺設計,總體外觀結構為一臺便攜式加固計算機,內部設計一塊FPGA核心板,對外接口采用統一的模塊化設計,通過SCPI命令及VISA I/O庫實現對儀表程控設置,通過上位機平臺實現系統的參數設置、測試流程編輯以及數據的自動捕獲、處理和可視化顯示。

參考文獻

[1]田晚成,基于FPGA和LabVIEW的某產品自動測試系統設計與實現[D].成都:電子科技大學,2019.

[2]尚建波,展利,一種射頻濾波組件自動測試系統的設計與實現[J],電子質量,2019(3),61-64.

[3]張翔,基于GPIB的數字電路自動測試系統設計分析[J],電子設計工程,2019,27(16),88-91.

[4]王華,基于ATE的FPGA測試技術研究和應用[J],電子與封裝,2018,18(7),12-15.

[5]雷愛強,某系列雷達自動測試系統研制[D].哈爾濱:哈爾濱工業大學,2014

[6]董志玉,發射接收模塊自動測試系統軟件模塊機流程設計[D].成都:電子科技大學,2017

[7]許麗君,一種PCB板測試系統的設計與實現[D].成都:電子科技大學,2018

[8]李雪瑩,FPGA軟件自動化測試平臺的設計與實現[D].上海:東華大學,2018

(作者簡介:馬緒鐸,碩士,工程師,主要研究為雷達系統信號處理及數字電路設計。工作單位:西安導航技術研究所)